A real-time backpressure method that supports pipelining

A pipeline and clock technology, applied in the direction of instrumentation, calculation, concurrent instruction execution, etc., can solve the problem of continuous interruption of the pipeline, and achieve the effect of satisfying reading and writing and ensuring continuity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

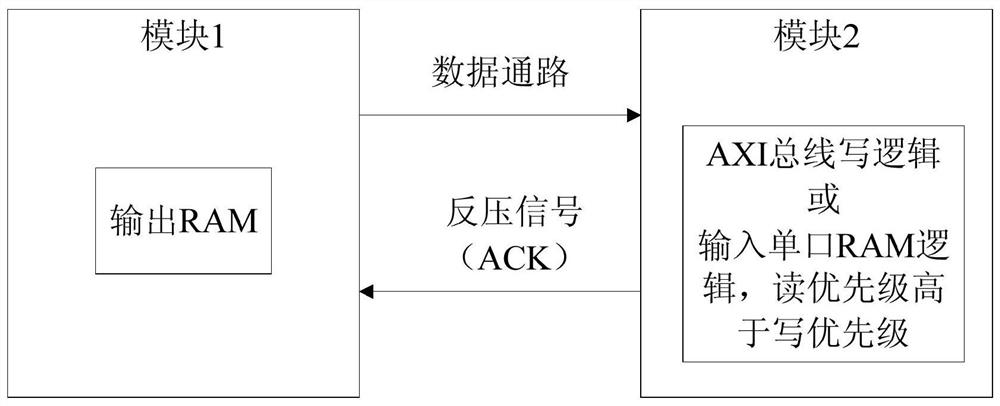

[0029] Based on the existing defects described above, Embodiment 1 of the present invention provides a hardware design scheme that supports real-time backpressure in units of pipeline units. On the preset level of the N-level pipeline, a corresponding number of registers is added to form a ping-pong structure. register set; preferably, N>=2.

[0030] For the real-time backpressure scenario of the RAM read path and the general real-time backpressure scenario except for the RAM read path, because the RAM read has its own restrictions (after the read data is valid, it can only maintain stability for one cycle, even if it is no longer read, the next period, there is no guarantee that the data can be maintained), so different hardware design schemes are used for these two real-time backpressure scenarios;

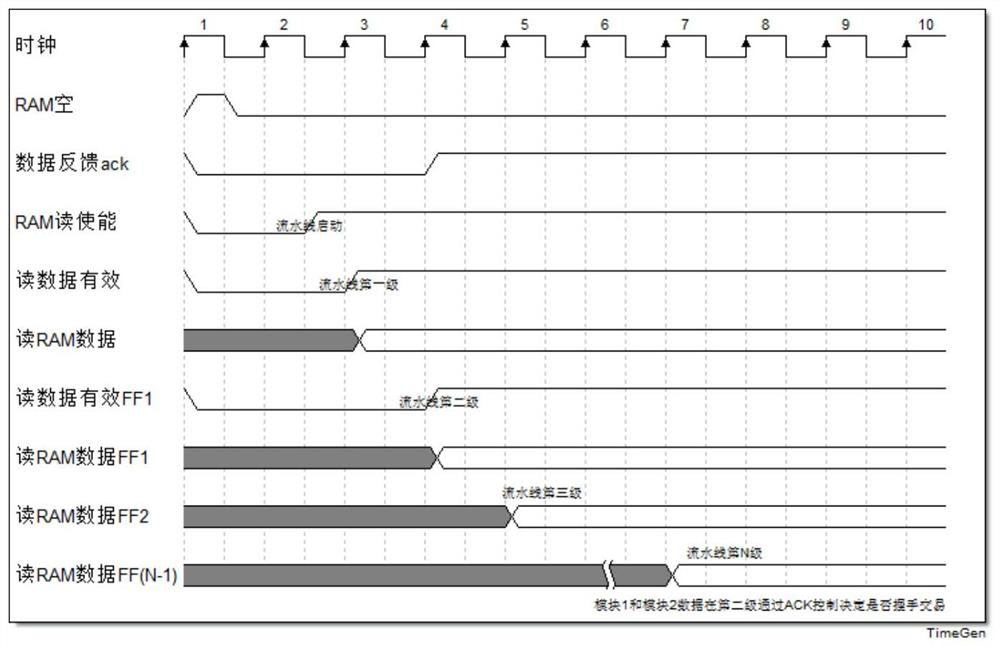

[0031] (1) RAM read path N-level pipeline real-time backpressure scenario

[0032] On the second stage of the N-stage pipeline, add (N-1) registers, and form N ping-pong regist...

Embodiment 2

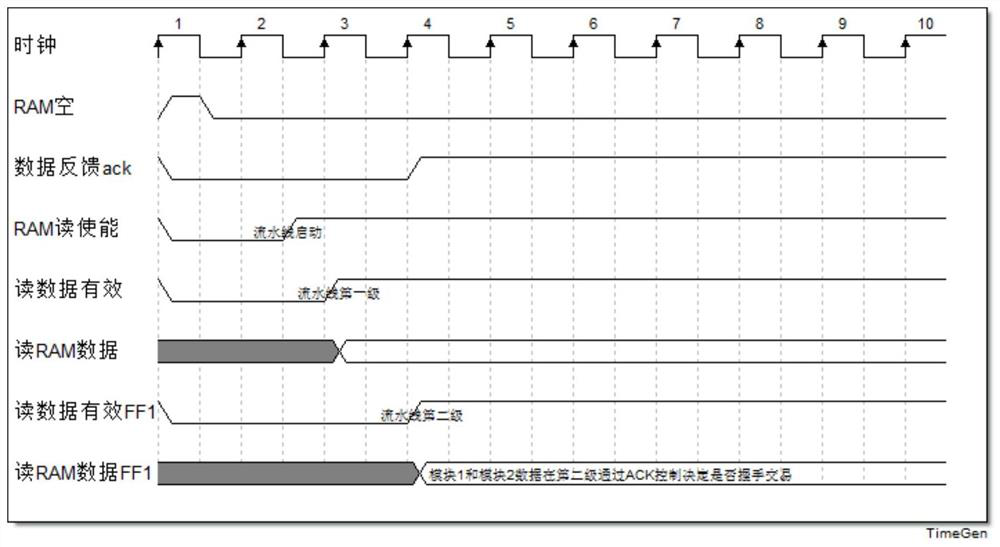

[0046] This embodiment takes N=2, that is, a two-stage pipeline as an example. It should be noted that, when the amount of collected data is not very large, setting up a two-stage pipeline can not only realize the normal and uninterrupted flow of the pipeline, but also have a simple design Easy to operate.

[0047] This embodiment is applicable to the situation where there is no real-time backpressure requirement in the second-level pipeline. image 3 It shows a schematic diagram of the second-stage pipeline structure of the on-chip RAM read path without real-time backpressure requirements;

[0048] When the RAM read enable signal is valid, the pipeline is started; when the next beat clock of the RAM read enable signal is valid, the first stage of the pipeline is started; when the next beat clock of the RAM read enable signal is valid, the second stage of the pipeline is started. For the RAM read enable signal to be valid, the RAM is empty and invalid and the read RAM data FF...

Embodiment 3

[0054] Embodiment 3 of the present invention is improved on the basis of Embodiment 2. Since Embodiment 2 is only applicable to the situation without real-time backpressure, if the feedback ACK signal is sent to change in real time at each clock, that is, real-time backpressure, then The situation of pipeline interruption occurs; Therefore, on the second-stage pipeline, add a register FF1_1 again, form the ping-pong register structure with FF1, improve the pre-full state of judging the ping-pong register in the valid condition of judging the RAM read enable signal.

[0055] In this embodiment, the RAM read enable effectively satisfies one of the following conditions:

[0056] (1) The pre-full status of the FF1 register for reading RAM data is invalid;

[0057] (2) The pre-full state of the FF1 register is valid for reading RAM data, and the ACK signal is valid.

[0058] Such as Figure 4 As shown, after the pipeline is started, the RAM read enable signal is always in an acti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More