Successive Approximation Analog-to-Digital Converter Based on Code Value Estimation

An analog-to-digital converter, successive approximation technology, applied in the direction of analog/digital conversion, code conversion, instrument, etc., can solve the problems of high power consumption, limited ADC conversion speed, etc., to reduce power consumption, reduce the number of clock cycles, The effect of increasing conversion speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The preferred embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

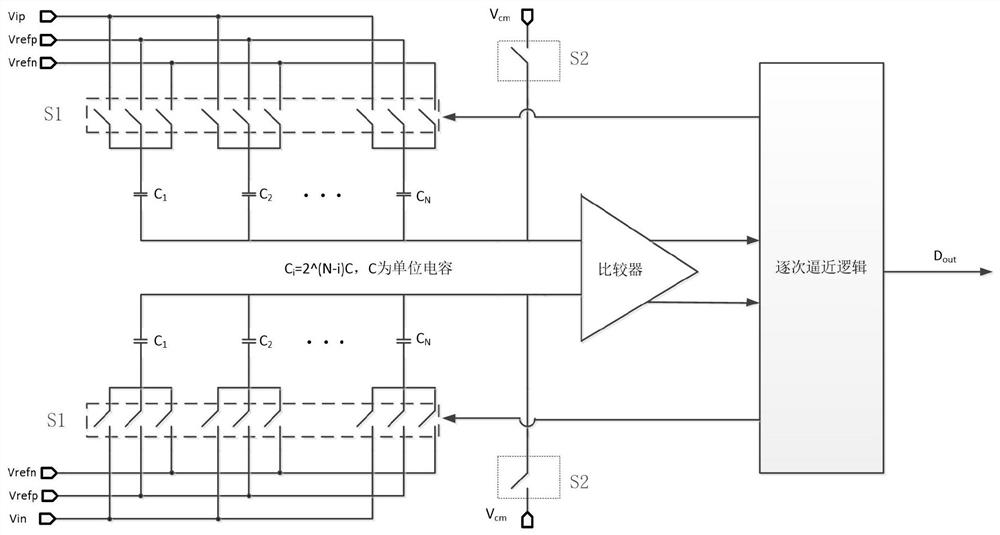

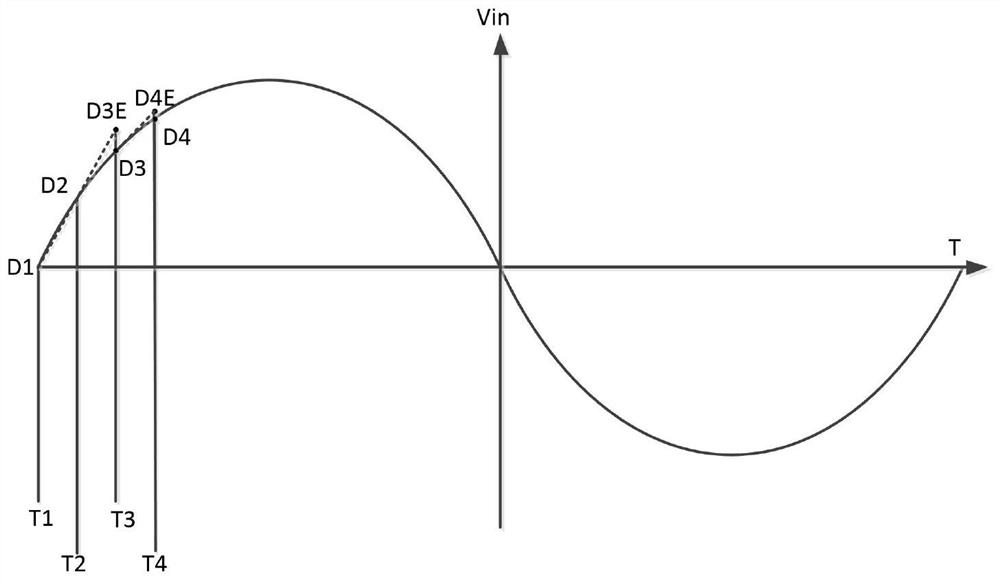

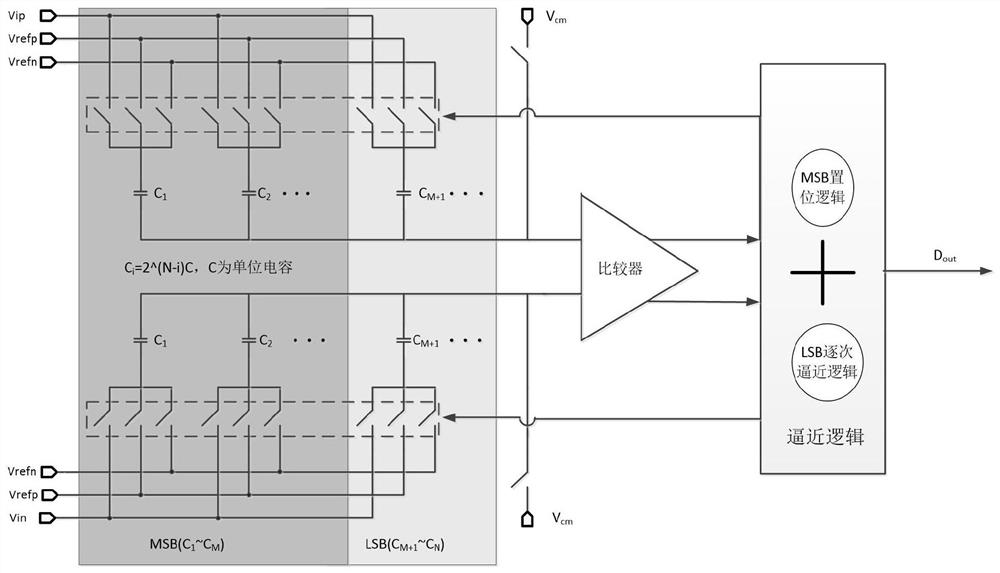

[0019] figure 1 It is a traditional N-bit successive approximation ADC; many SARADCs in the industry have a high oversampling rate. Compared with the sampling period, the input signal can be equivalent to a very slowly changing signal, and the digital code at the next conversion point In fact, the value can be roughly estimated based on the digital codes of the previous cycles. The principle is as follows: figure 2 As shown, there are two cases. When the input signal frequency is low, the oversampling rate is high. If the digital code values D1 and D2 at T1 and T2 are known, in the case of first-order approximation, the digital at T3 An approximation of the code is expressed as:

[0020] D3E=2*D2-D1

[0021] According to the estimated value D3E, the judgment result of the high-order capacitor is obtained. The high-order bit is direc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More