Clock-controlled D flip-flop based on FinFET device

A trigger and device technology, applied in electrical components, electrical pulse generator circuits, pulse generation, etc., can solve the problems of large power consumption delay product, large power consumption, large area, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

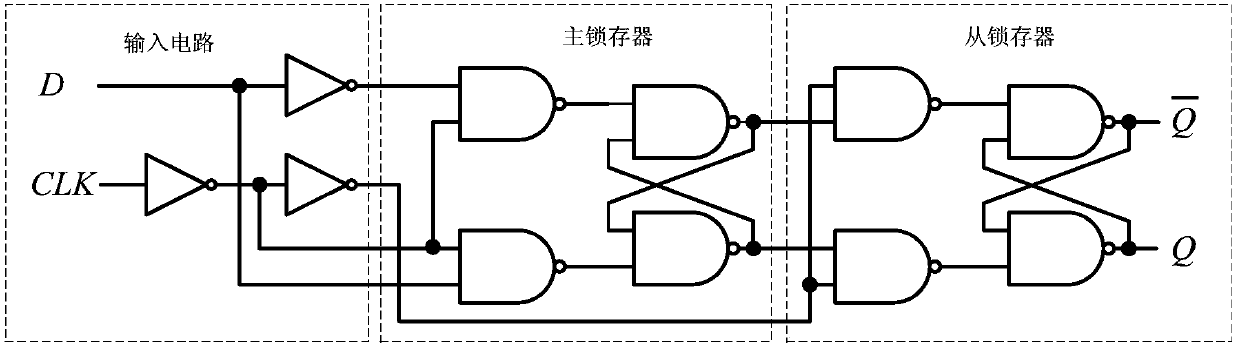

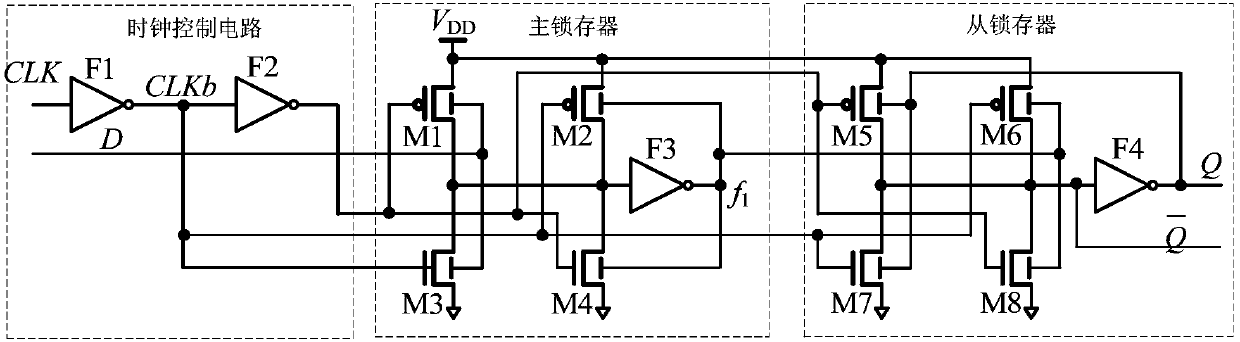

[0015] Embodiment one: if figure 2 As shown, a clocked D flip-flop based on a FinFET device includes a master latch and a slave latch. The clocked D flip-flop also includes a clock control circuit, and the clock control circuit includes a first inverter F1 and a second inverter F1. Inverter F2, the input terminal of the first inverter F1 is the clock input terminal of the clock control circuit for accessing the clock signal CLK, the output terminal of the first inverter F1 and the input terminal of the second inverter F2 connected and its connection end is the inverting clock output end of the clock control circuit, the inversion signal CLKb of the output clock signal CLK, the output end of the second inverter F2 is the clock output end of the clock control circuit; the main latch includes the first A FinFET tube M1, a second FinFET tube M2, a third FinFET tube M3, a fourth FinFET tube M4 and a third inverter F3, the first FinFET tube M1 and the second FinFET tube M2 are P-ty...

Embodiment 2

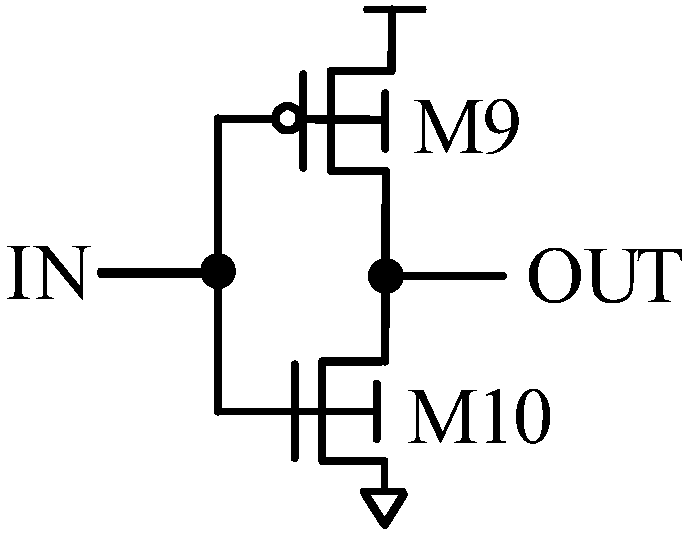

[0016] Embodiment 2: This embodiment is basically the same as Embodiment 1, the only difference is that in this embodiment, the first inverter F1 includes a ninth FinFET tube M9 and a tenth FinFET tube M10, and the ninth FinFET tube M9 is a P-type FinFET The tenth FinFET tube M10 is an N-type FinFET tube, the number of fins in the ninth FinFET tube M9 is 2, and the number of fins in the tenth FinFET tube M10 is 1; the source of the ninth FinFET tube M9 is connected to the power supply VDD, and the ninth FinFET tube M9 has The front gate of the FinFET tube M9, the back gate of the ninth FinFET tube M9, the front gate of the tenth FinFET tube M10, and the back gate of the tenth FinFET tube M10 are connected, and the connection terminal is the input terminal of the first inverter F1, and the connection terminal of the tenth FinFET tube M10 is connected to the input terminal of the first inverter F1. The drain of the ninth FinFET tube M9 is connected to the drain of the tenth FinFE...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More