A five-stage three-level inverter svpwm modulation algorithm

A technology of three-level inverter and modulation algorithm, which is applied in the direction of electrical components, AC power input conversion to DC power output, output power conversion devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0077] The specific implementation manners of the present invention will be further described below in conjunction with the accompanying drawings and technical solutions.

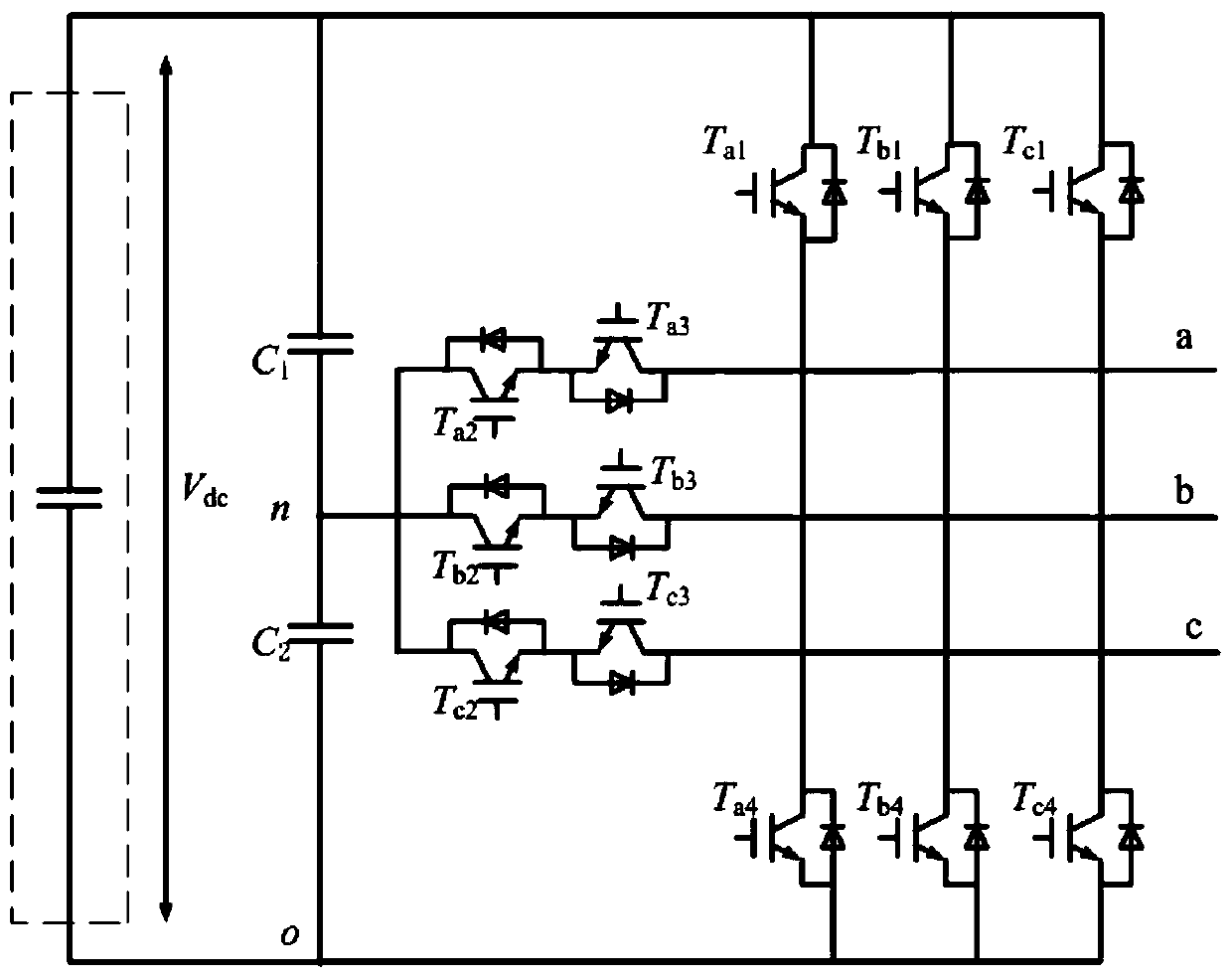

[0078] figure 1 , each phase of the inverter can output U according to different switch combinations dc / 2, 0, -U dc / 2 three levels. The switching states corresponding to the three output levels are called P, O, and N, respectively. Taking phase A as an example, the P state means that the switch state of this phase is [1 1 00], and the output voltage corresponds to the DC side capacitor C 1 voltage, that is, the output voltage is U dc / 2; O state means that the switch state of this phase is [0 1 10], the output voltage corresponds to point O on the DC side, that is, the output voltage is 0; N state means that the phase switch state is [0 0 1 1], and the output voltage corresponds to the DC side Capacitance C 2 voltage, that is, the output voltage is U dc / 2.

[0079] The three-phase voltages differ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More