Semiconductor packaging structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, which is applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device parts, etc., can solve the problems of affecting the results and difficult control of etching depth, so as to simplify the process, improve production efficiency and The effect of yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

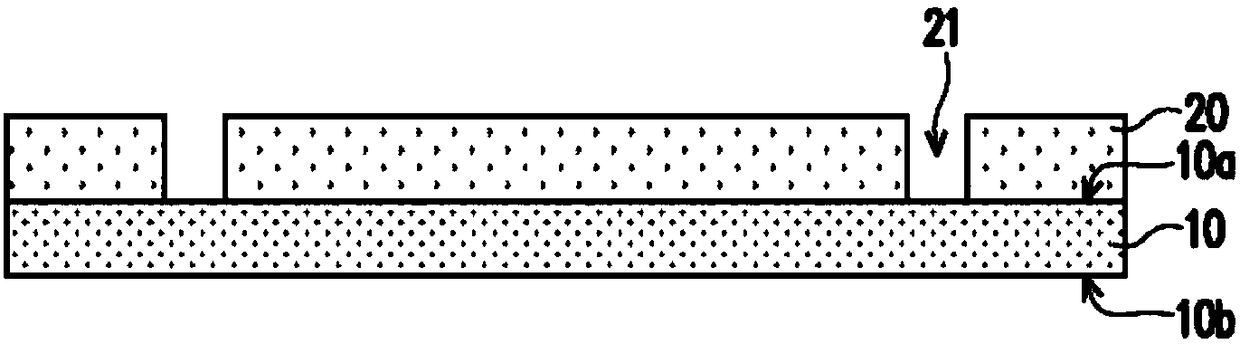

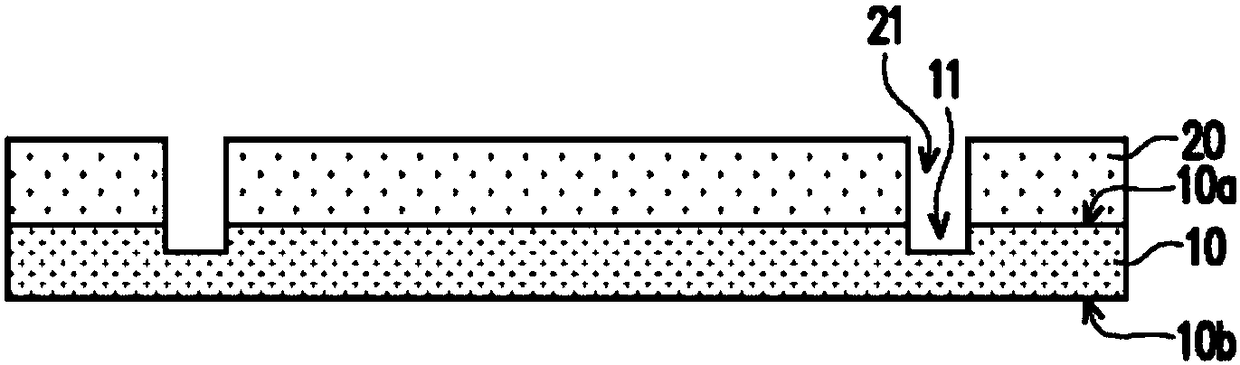

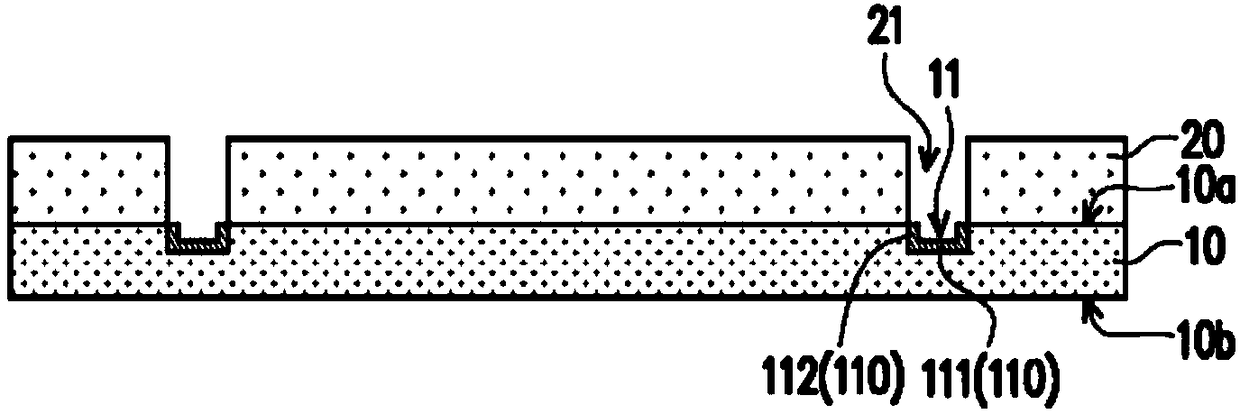

[0041] Figure 1A to Figure 1I is a schematic cross-sectional view of the manufacturing process of the semiconductor package structure according to an embodiment of the present invention. The manufacturing method of the semiconductor package structure 100 of the present embodiment comprises the following steps: first, please refer to Figure 1A , providing a substrate 10, wherein the substrate 10 has a first surface 10a and a second surface 10b opposite to each other. Next, a mask layer 20 is formed on the first surface 10a of the substrate 10, wherein the mask layer 20 has a plurality of openings 21, and these openings 21 expose part of the first surface 10a, and the shape of these openings can be circular or square, but the invention is not limited thereto. In this embodiment, the material of the substrate 10 may be copper or other conductive metals.

[0042] On the other hand, the mask layer 20 may be a patterned photoresist layer formed by a photolithography process. As ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More