Method for judging IDDQ test by using current difference value

A technology of current difference and current value, applied in the field of screening and testing of integrated circuit chips, can solve the problems of poor IDDQ test ability and deviation of processing technology.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

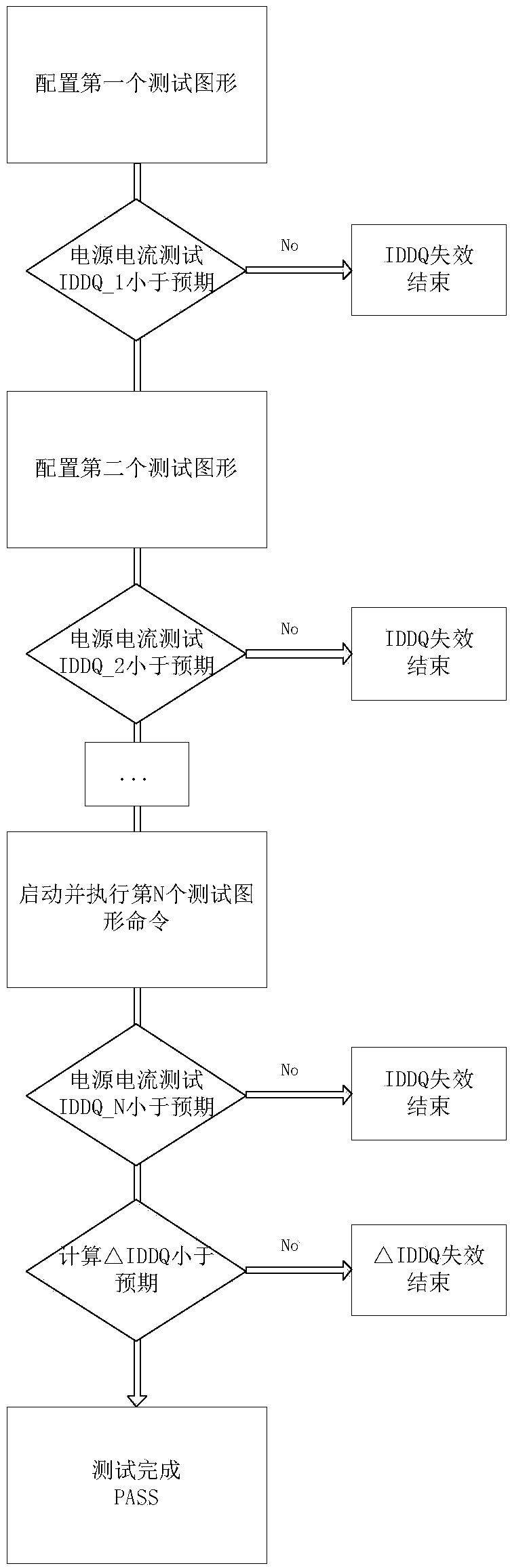

[0015] The test of IDDQ can be summarized as figure 1 The flow chart shown.

[0016] First configure the digital part of the chip to meet the first test pattern. Then test the power supply current of the chip, mark it as IDDQ_1, and judge whether the test result is within the SPEC range. In the test, the upper limit and lower limit of the test will be given according to each test item in the test specification, that is, to judge whether it is within the scope of the test SPEC.

[0017] It is recommended here that the average value of the entire wafer test for the FF biased wafer + 3 times Σ be used as the upper limit of the test. The average value -3 times Σ of the whole piece of the SS pull-off wafer is used as the lower limit of the test. The SPEC obtained in this way can ensure the stability of mass production. At the same time, record...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More