CMOS image sensor and its manufacturing method

A technology of an image sensor and a manufacturing method, which is applied to semiconductor devices, electric solid-state devices, radiation control devices, etc., can solve problems such as increasing costs, and achieve cost-saving effects.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

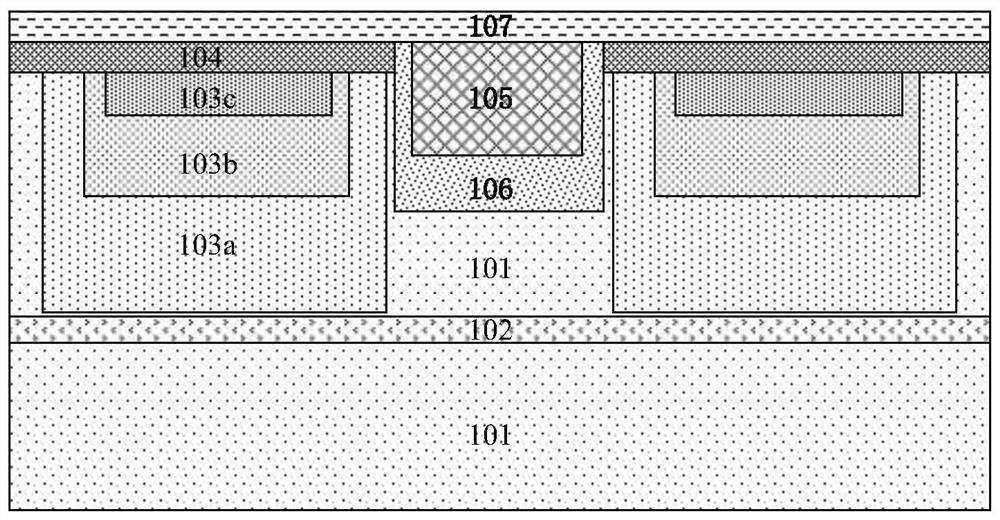

[0045] Such as Figure 4 Shown is a schematic structural diagram of photosensitive diodes of each pixel unit of the CMOS image sensor of the embodiment of the present invention. The CMOS image sensor of the embodiment of the present invention is formed on a P-type semiconductor substrate 1 and includes a plurality of pixel units.

[0046] Each of the pixel units includes a surface clamped photodiode, and the clamped photodiode includes an N-type buried layer formed in the P-type semiconductor substrate 1 and a surface P+ layer 4 formed on the surface of the N-type buried layer. And the clamping photodiode is formed by stacking the P-type semiconductor substrate 1 , the N-type buried layer and the surface P+ layer 4 .

[0047] In the embodiment of the present invention, the N-type buried layer includes a deep N well 3a, an N well 3b and a surface N-type layer 3c, the junction depth of the deep N well 3a is greater than the junction depth of the N well 3b and the N The well 3b ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More