Design method of standard cell library circuit

A standard cell library and circuit design technology, applied in CAD circuit design, calculation, electrical and digital data processing, etc., can solve the problems of low efficiency, need more, easy to make mistakes, etc., to improve work efficiency, reduce error rate, realize The effect of automated design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

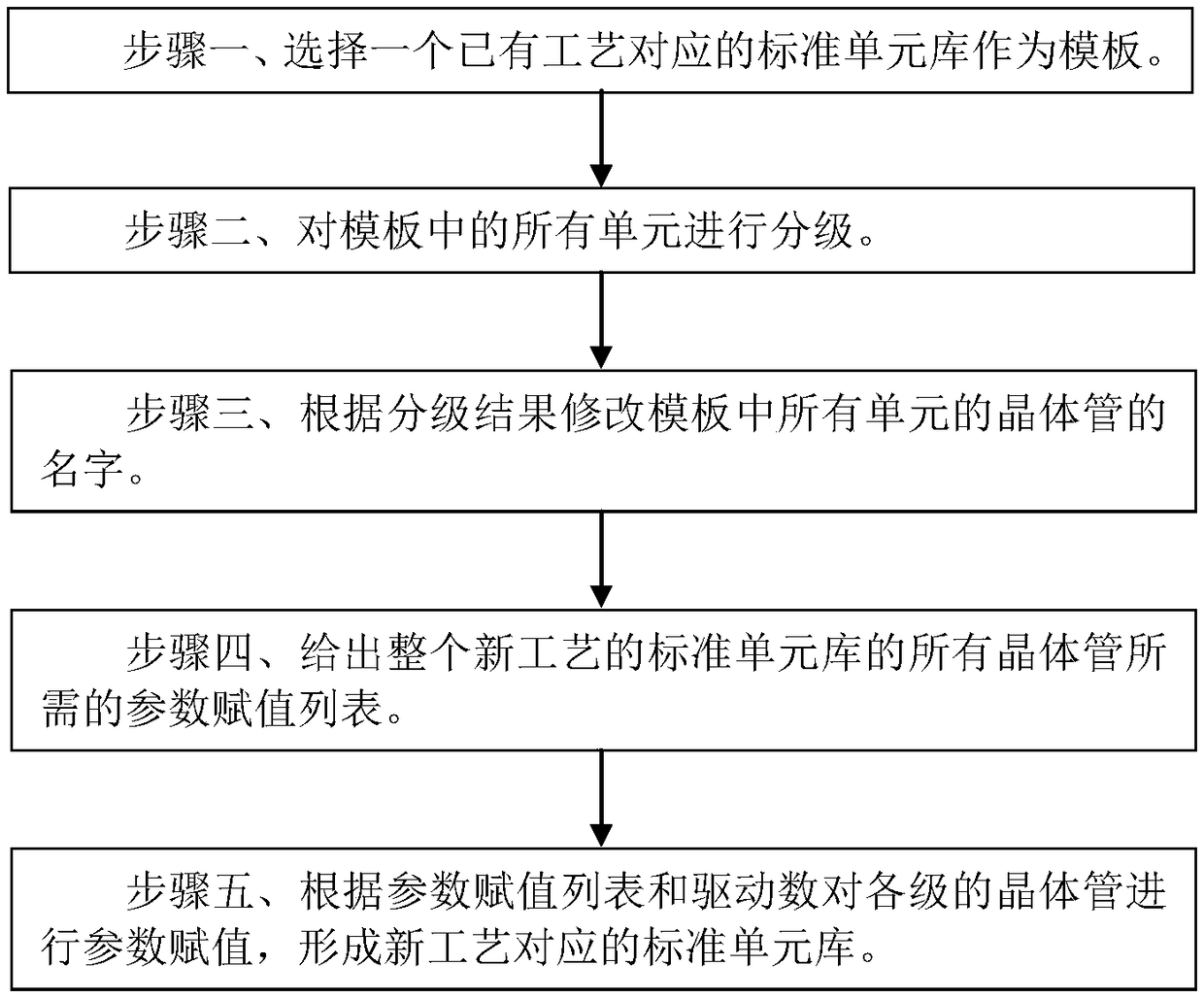

[0043] Such as figure 1 As shown, it is a flow chart of the standard cell library circuit design method of the embodiment of the present invention, and the standard cell library circuit design method of the embodiment of the present invention includes the following steps:

[0044] Step 1. Select a standard cell library corresponding to an existing process as a template.

[0045] Step 2: Grading all units in the template.

[0046] Grading takes place from the output stage to the input stage of each of the units.

[0047] The maximum number of stages in each unit is 5 stages.

[0048] The units include inverters, buffers, AND gates, NAND gates, OR gates, NOR gates, AND-OR gates, AND-NOR, OR-AND, OR-NO, exclusive-NOR, adders, selectors, Latches, flip flops, clock gating.

[0049] The grading method is:

[0050] The output stage is the first stage, and one stage deeper into the circuit is the second stage. By analogy, the embodiment of the present invention is divided into fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More