Semiconductor structure and operation method thereof

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] The present invention will be described more fully with reference to the accompanying drawings of this embodiment. However, the present invention can also be embodied in various forms and should not be limited to the embodiments described herein. In the drawings, the thicknesses of layers and regions may be exaggerated for clarity. The same or similar symbols represent the same or similar elements, and the following paragraphs will not repeat them one by one.

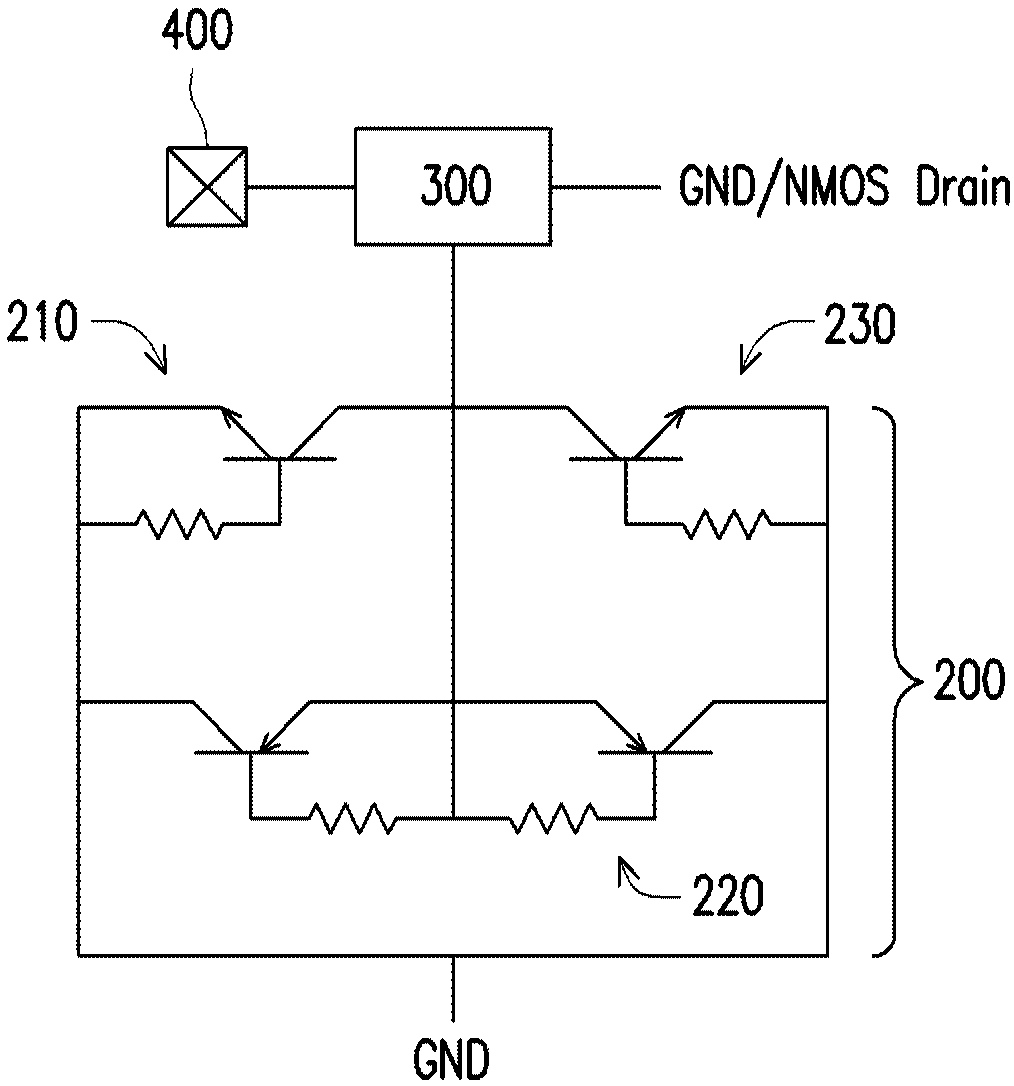

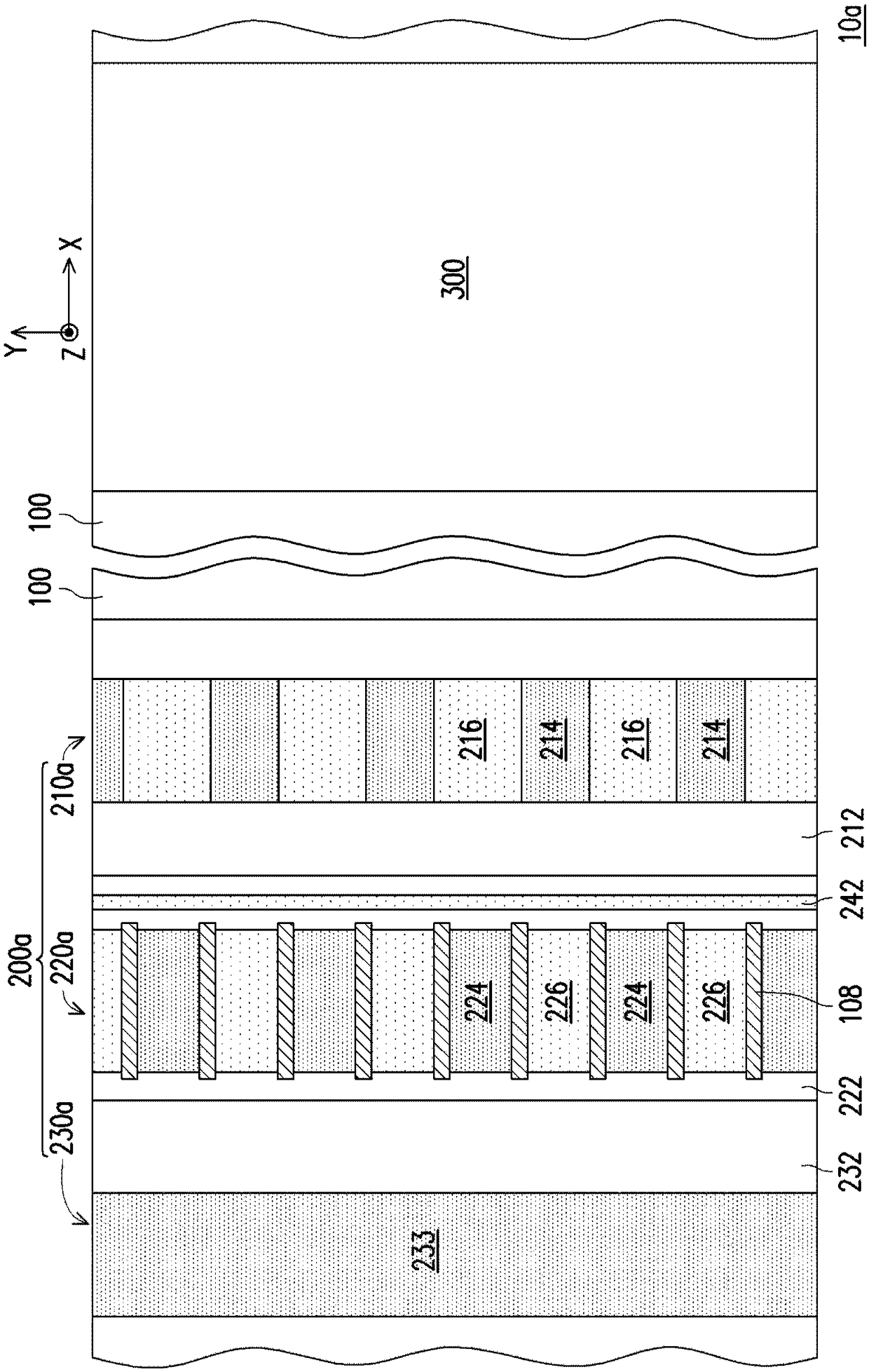

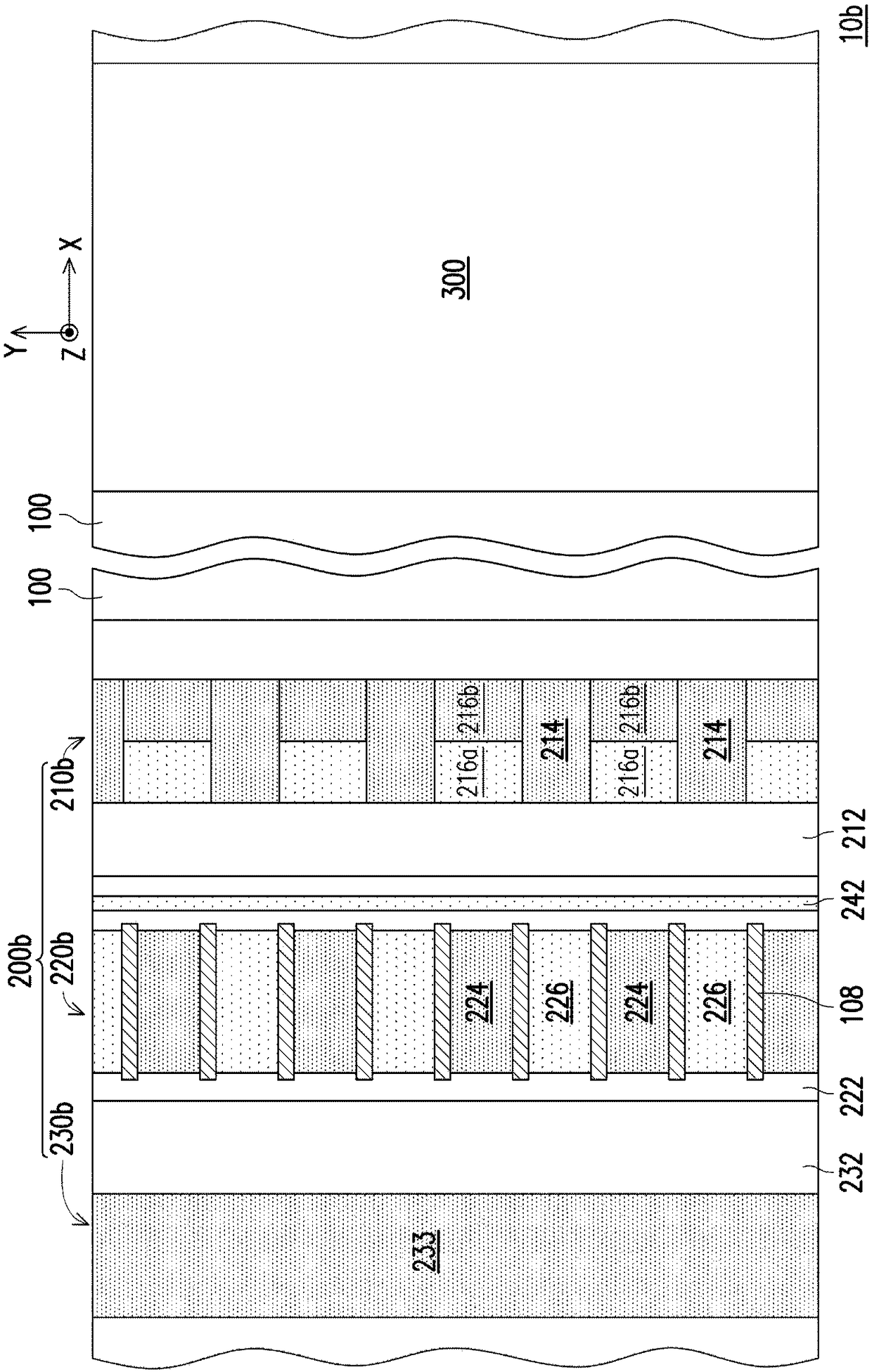

[0053] figure 1 is an equivalent circuit diagram of a semiconductor structure according to an embodiment of the present invention.

[0054] Please refer to figure 1 , the present embodiment provides a semiconductor structure 1 including an ESD protection element 200 and a semiconductor element 300 . The ESD protection device 200 is located between the semiconductor device 300 and a ground terminal GND. In detail, the ESD protection element 200 includes a first guard ring 210 , a second guard ring 220 and a t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com