Semiconductor structure, memory structure and manufacturing method thereof

A memory and semiconductor technology, applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electric solid-state devices, etc., can solve the problems of easy offset of conductive plugs, high contact resistance of conductive plugs, and small effective contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

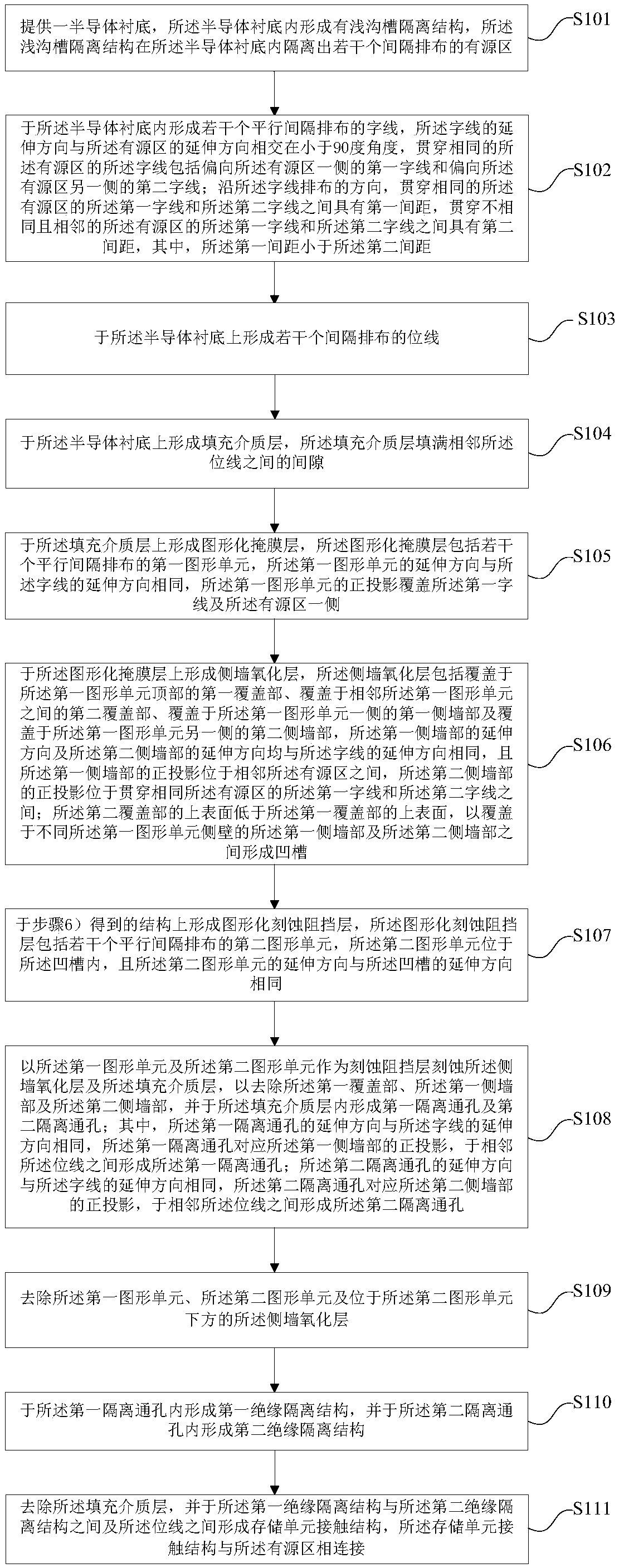

[0244] Such as figure 1 Shown, the present invention provides a kind of preparation method of memory structure, and the preparation method of described memory structure comprises the following steps:

[0245] 1) A semiconductor substrate is provided, and a shallow trench isolation structure is formed in the semiconductor substrate, and the shallow trench isolation structure isolates several active regions arranged at intervals in the semiconductor substrate;

[0246] 2) A plurality of word lines arranged in parallel and at intervals are formed in the semiconductor substrate, the extension direction of the word lines intersects with the extension direction of the active region at an angle less than 90 degrees, and runs through the same active region. The word lines in the region include a first word line biased to one side of the active region and a second word line biased to the other side of the active region; along the direction in which the word lines are arranged, the same...

Embodiment 2

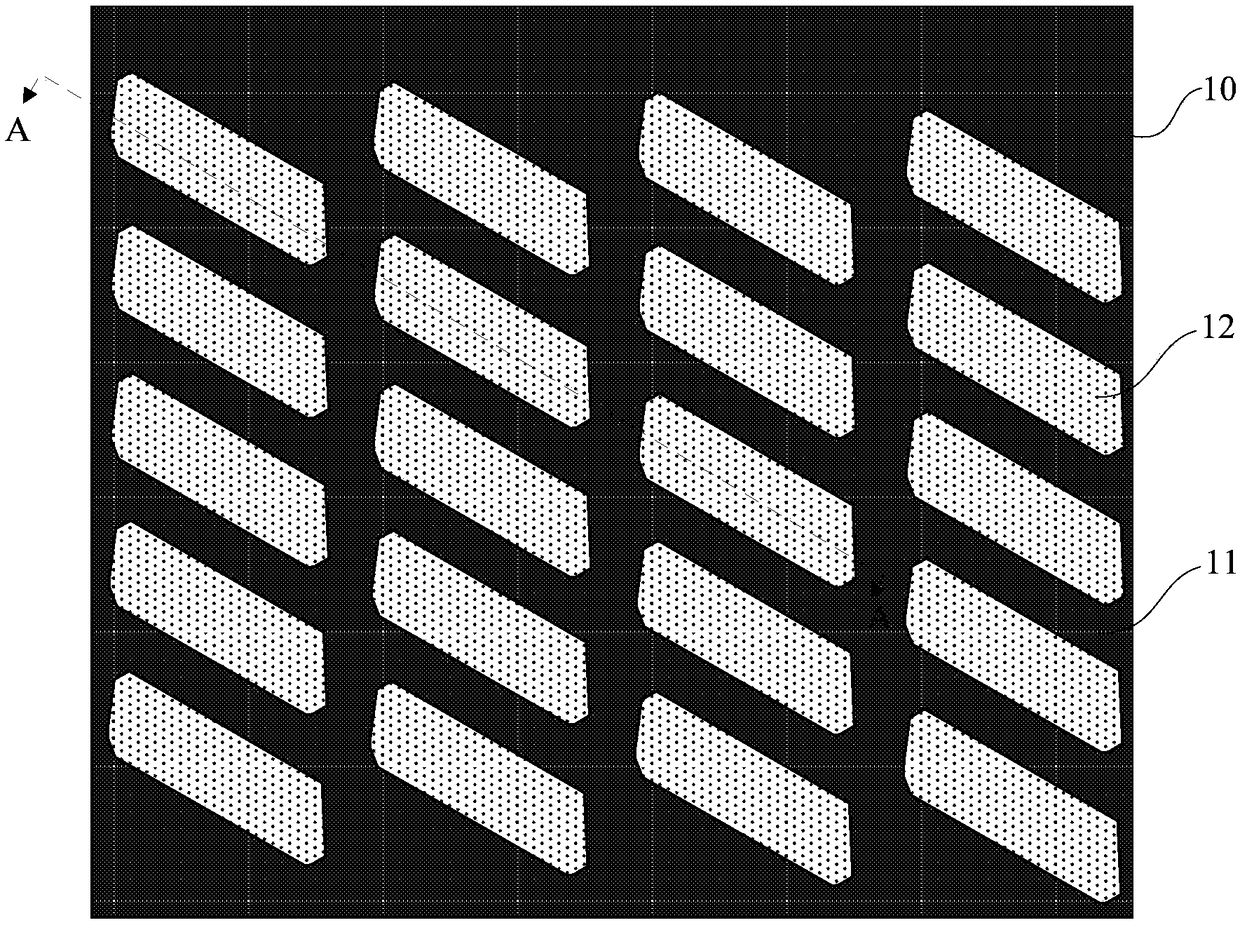

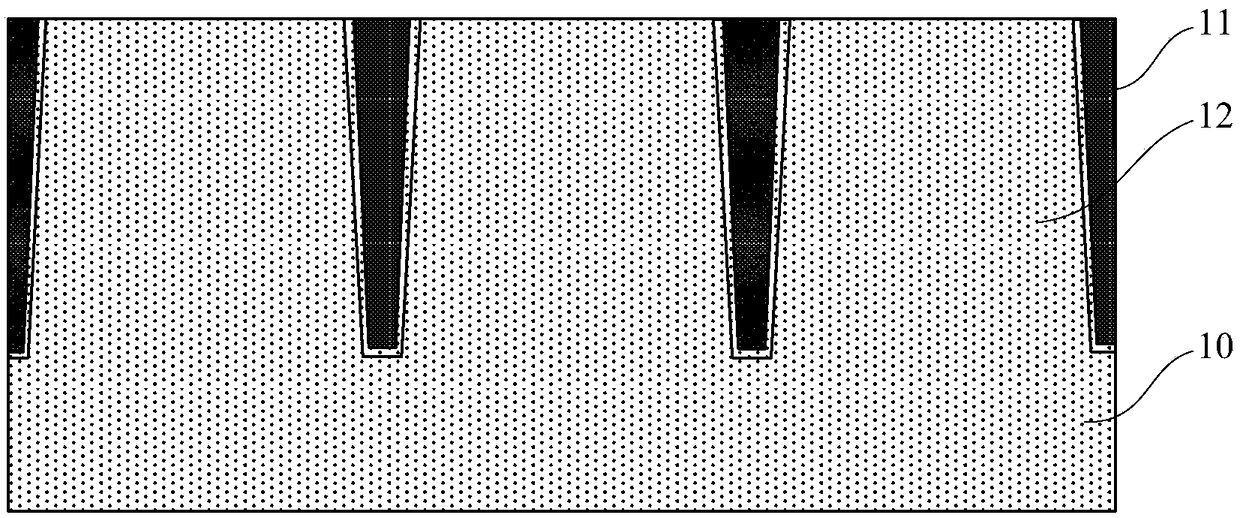

[0319] Please combine Figure 2 to Figure 24 read on Figure 25 to Figure 26 The present invention also provides a memory structure, which includes: a semiconductor substrate 10, a shallow trench isolation structure 11 is formed in the semiconductor substrate 10, and the shallow trench isolation structure 11 is formed on the semiconductor substrate Several active regions 12 arranged at intervals are isolated in the bottom 10; several word lines 13 are arranged at intervals in parallel, and the word lines 13 are located in the semiconductor substrate 10, and the extending direction of the word lines 13 is in line with that of the semiconductor substrate 10. The extending directions of the active regions 12 intersect at an angle of less than 90 degrees; the word lines 13 running through the same active region 12 include the first word lines 13a biased to one side of the active region 12 and the second word line 13b biased to the other side of the active region 12; along the dir...

Embodiment 3

[0339] see Figure 27 , the present invention also provides a method for preparing a semiconductor structure, the method for preparing a semiconductor structure comprising the following steps:

[0340] 1) providing a semiconductor substrate, a shallow trench isolation structure is formed in the semiconductor substrate, and the shallow trench isolation structure isolates several active regions arranged at intervals in the semiconductor substrate;

[0341] 2) forming several parallel and spaced protruding structures on the semiconductor substrate, the upper surface of the protruding structures is higher than the upper surface of the semiconductor substrate; the extension direction of the bit line is the same as the active the directions of extension of the zones intersect at a first angle less than 90 degrees;

[0342] 3) forming a side wall structure on the side wall of the bit line, and the side wall structure covers the outer wall of the bit line;

[0343] 4) forming a fill...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More