Fully isolated laterally diffused metal oxide semiconductor structure and manufacturing method

A technology of oxide semiconductors and manufacturing methods, applied in the field of LDMOS, can solve problems such as limited improvement effect, difficulty in realizing high-voltage applications, and increasing P-type substrates

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

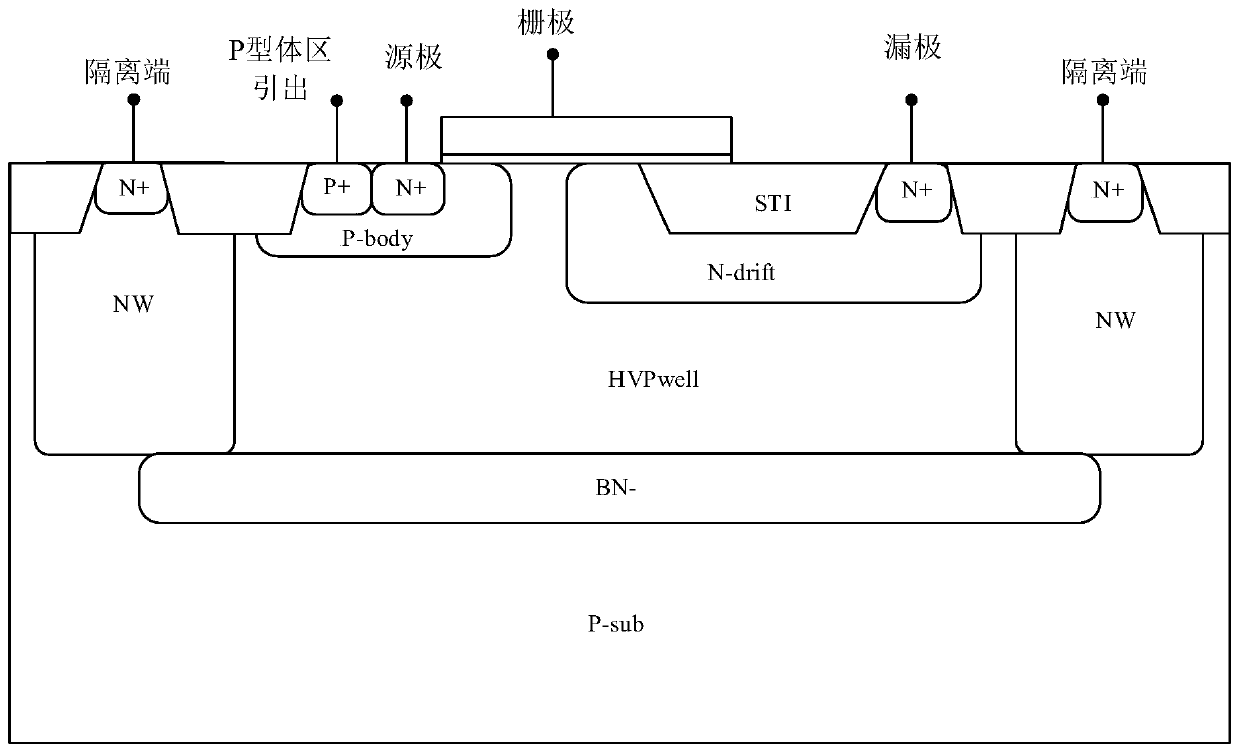

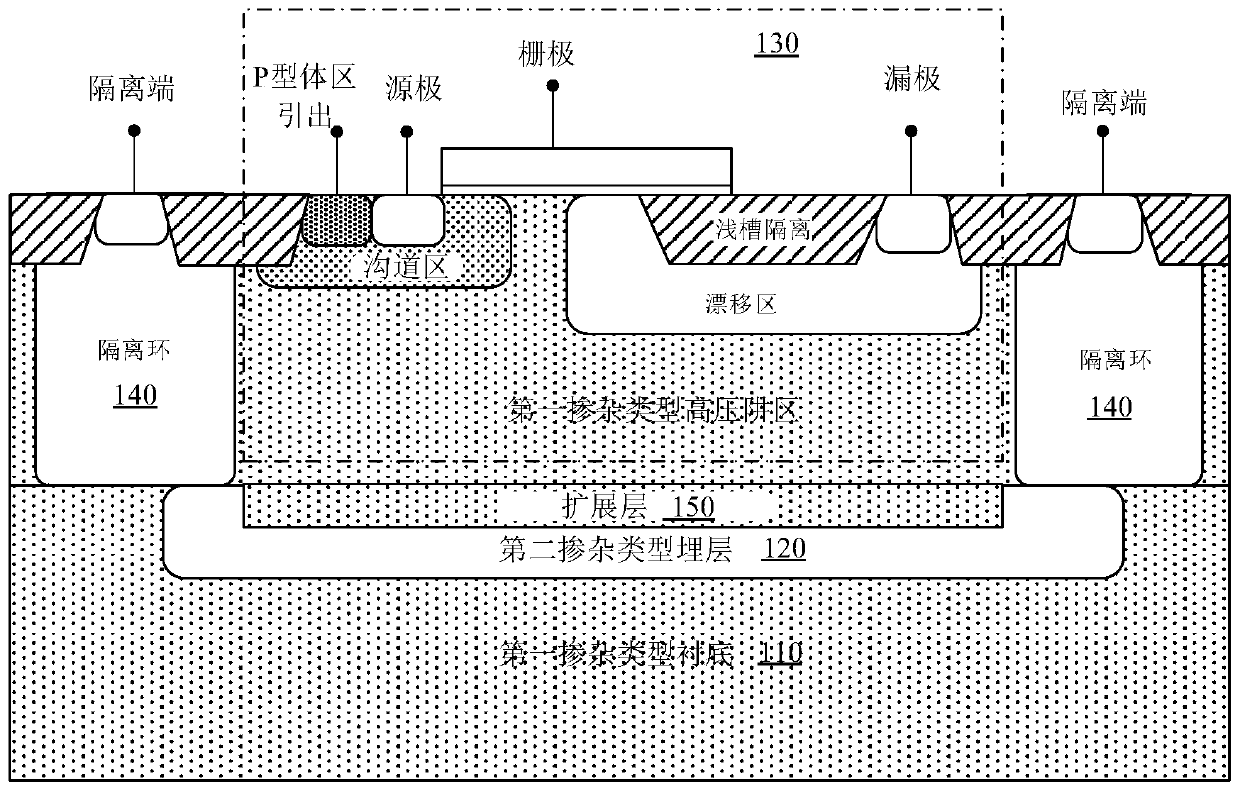

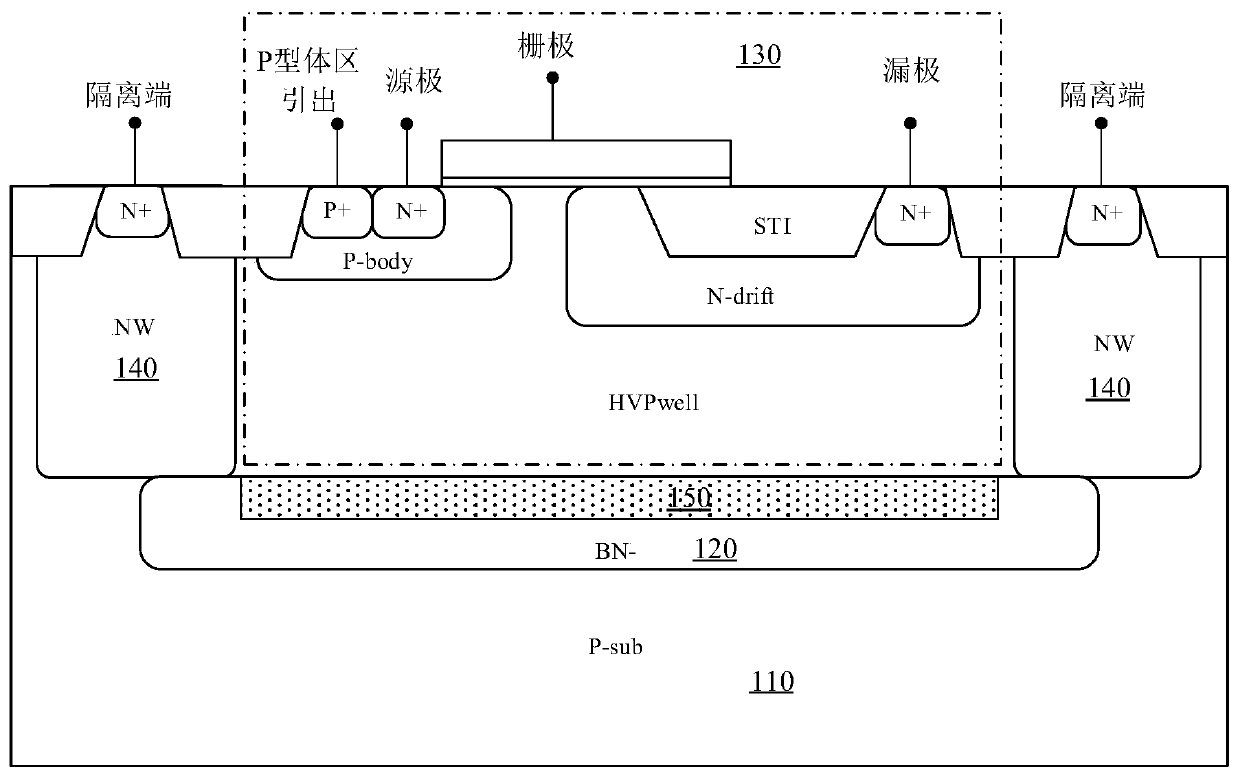

[0032] figure 2 It is a fully isolated laterally diffused metal-oxide-semiconductor structure in an embodiment. The semiconductor structure includes a substrate 110 of a first doping type, a buried layer 120 of a second doping type placed in the substrate 110 of the first doping type, and a buried layer 120 of the second doping type formed on the buried layer 120 of the second doping type. The main structure 130 in the epitaxial layer and the isolation ring 140 arranged around the main structure 130 . The buried layer 120 of the second doping type and the isolation ring 140 isolate the main stru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More