Fabrication method of frontal emitter junction tunneling oxidation passivation battery base on single crystal PERC

A technology of tunneling oxidation and emitter junction, applied in circuits, electrical components, final product manufacturing, etc., can solve the problems of unsatisfactory battery preparation method, poor repeatability, and high equipment cost, and achieve the effect of improving battery Voc

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

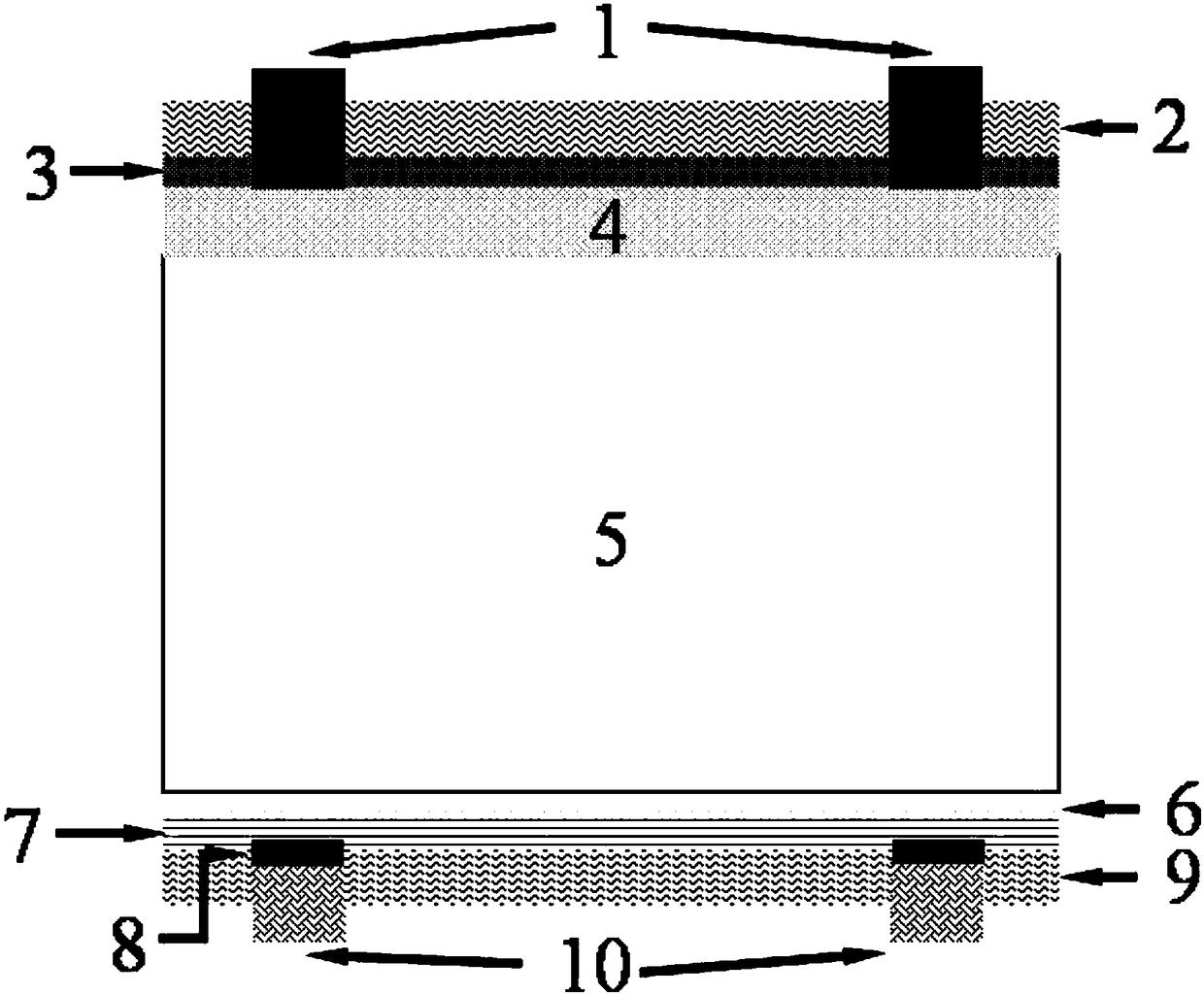

Image

Examples

Embodiment 1

[0031] A method for preparing a front emitter junction tunneling oxidation passivation cell based on single crystal PERC technology, using the following steps:

[0032] (1) Remove the damaged layer of the silicon wafer in the alkali texturing tank and perform surface polishing and single-side texturing to form a 3 μm high pyramid textured surface;

[0033] (2) Preparation of ultra-thin tunneling oxide layer SiO on the back of the cell by wet chemical or high temperature thermal oxidation process 2 , with a thickness of 1.8-2nm, a P-doped polysilicon layer with a thickness of 50nm is deposited on the front side of the silicon wafer by CVD. The P-doped polysilicon layer is based on the PECVD method with high-purity SiH 4 The gas source is prepared and formed at 500°C-600°C, and the concentration of doped P is 5×10 20 cm -3 ;

[0034] (3) The back of the battery is selectively etched by a wet process. The wet selective etching uses a commonly used polycrystalline etching solut...

Embodiment 2

[0044] Based on the preparation method of monocrystalline PERC front emitter junction tunneling oxidation passivation cell, the following steps are adopted:

[0045] (1) Remove the damaged layer of the silicon wafer in the alkali texturing tank and perform surface polishing and single-side texturing to form a 1 μm high pyramid textured surface;

[0046] (2) Preparation of ultra-thin tunnel oxide layer SiO on the textured surface of silicon wafer 2 and P-doped polysilicon layer to form N + For the emitter junction, this embodiment uses a wet chemical process to prepare an ultra-thin tunneling oxide layer, the temperature is controlled at 50°C, the solution used is a pure nitric acid solution with a concentration of 69 wt%, and the reaction time of the silicon wafer in the solution is controlled at 50 minutes , the fabricated ultra-thin tunnel oxide SiO 2 The thickness of the doped polysilicon layer is 0.5nm, and the P-doped polysilicon layer is based on the PECVD method. The ...

Embodiment 3

[0055] Based on the preparation method of monocrystalline PERC front emitter junction tunneling oxidation passivation cell, the following steps are adopted:

[0056] (1) Remove the damaged layer of the silicon wafer in the alkali texturing tank and perform surface polishing and single-side texturing to form a 2 μm high pyramid textured surface;

[0057] (2) Preparation of ultra-thin tunnel oxide layer SiO on the textured surface of silicon wafer 2 and P-doped polysilicon layer to form N + For the emitter junction, this embodiment uses a wet chemical process to prepare an ultra-thin tunneling oxide layer, the temperature is controlled at 120°C, the solution used is a pure nitric acid solution with a concentration of 69 wt%, and the reaction time of the silicon wafer in the solution is controlled at 30 minutes , the fabricated ultra-thin tunnel oxide SiO 2 The thickness of the doped polysilicon layer is 1nm, and the P-doped polysilicon layer is based on the PECVD method. CVD e...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More