NMOS (N-channel Metal Oxide Semiconductor) tube and manufacturing method thereof

A manufacturing method and dummy gate technology, applied in semiconductor/solid-state device manufacturing, transistors, electrical components, etc., can solve problems such as the influence of device performance stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

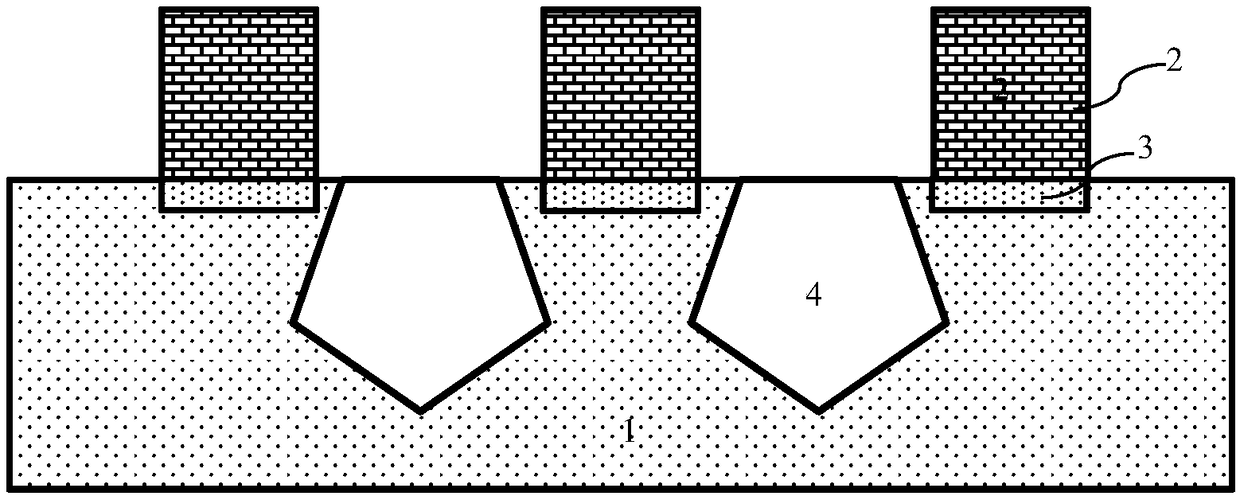

[0045] The manufacturing method of the existing NMOS tube:

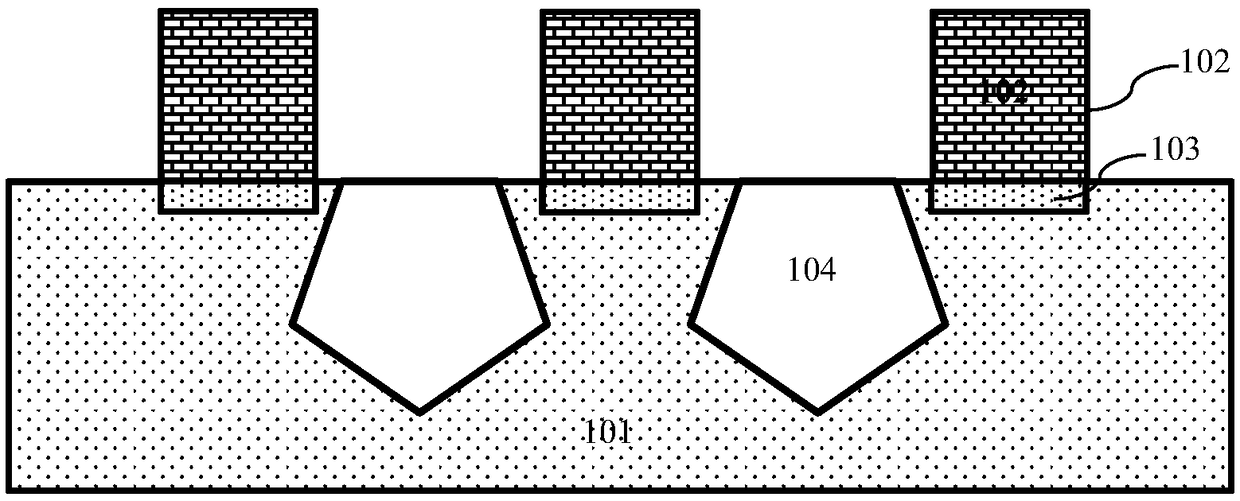

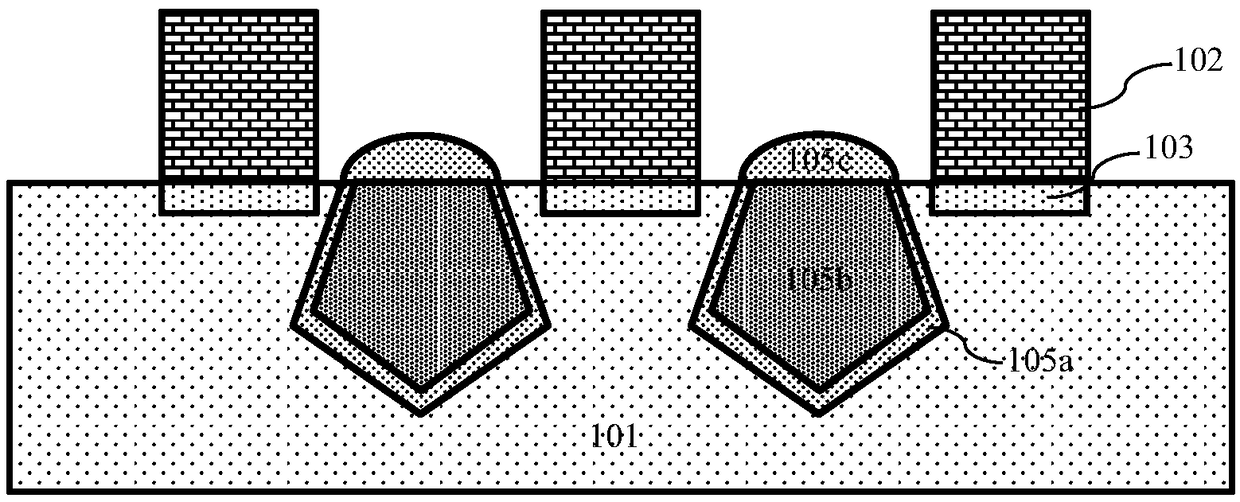

[0046] Before introducing the embodiment of the present invention in detail, introduce the manufacturing method of the existing NMOS tube, such as Figure 1A to Figure 1B Shown is a device structure diagram in each step of the manufacturing method of the existing NMOS tube; the manufacturing method of the existing NMOS tube includes the following steps:

[0047] Step one, such as Figure 1A As shown, a silicon substrate with a P well 101 formed on its surface is provided, a dummy gate structure is formed on the surface of the P well 101 , and a channel 103 is formed on the surface of the P well 101 covered by the dummy gate structure.

[0048] The dummy gate structure includes a first gate dielectric layer and a polysilicon dummy gate 102 formed on the surface of the P well 101 .

[0049] Silicon nitride spacers are formed on both sides of the dummy gate structure.

[0050] Step two, such as Figure 1A As shown, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More