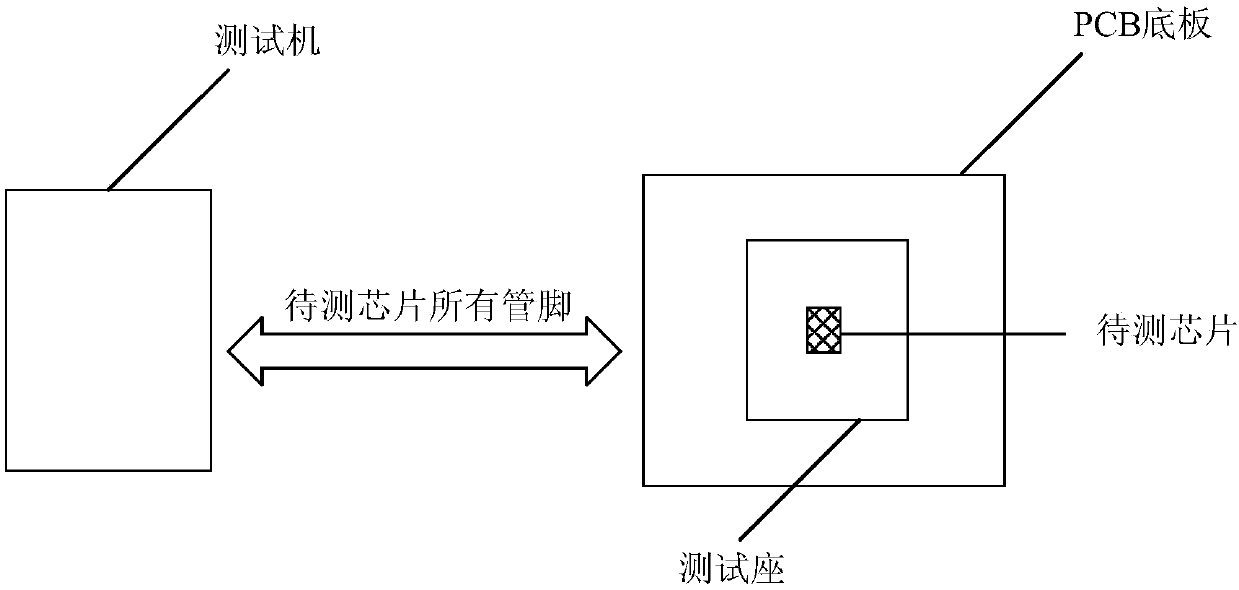

Chip test method based on FPGA/MCU

A chip testing and chip technology, applied in the field of chip testing based on FPGA/MCU, can solve the problems of long time period, high cost of returning to the factory, difficult to implement, etc., and achieve the effect of good real-time performance and convenient after-sales maintenance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

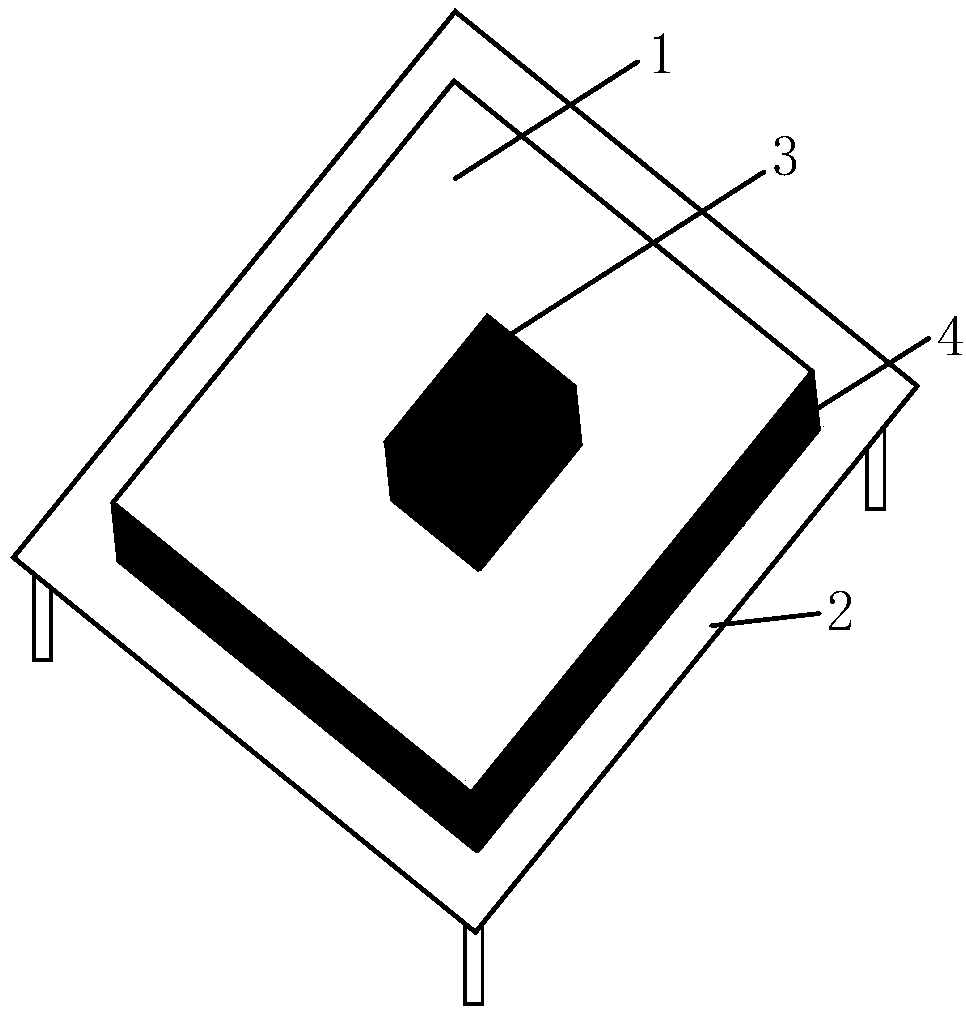

[0076] The embodiments of the present invention further describe the chip testing method of the present invention by taking a CPLD chip as an example on the basis of the above-mentioned embodiments.

[0077] Step 1: Place the CPLD chip to be tested in the test seat 3 , wherein the test seat 3 is located on the daughter board 1 .

[0078] Step 2: Connect the pins of the CPLD chip to be tested with the I / O pins of the FPGA chip 5 on the test board through pin headers.

[0079] The pins of the CPLD chip to be tested correspond to the I / O pins of the FPGA chip one by one.

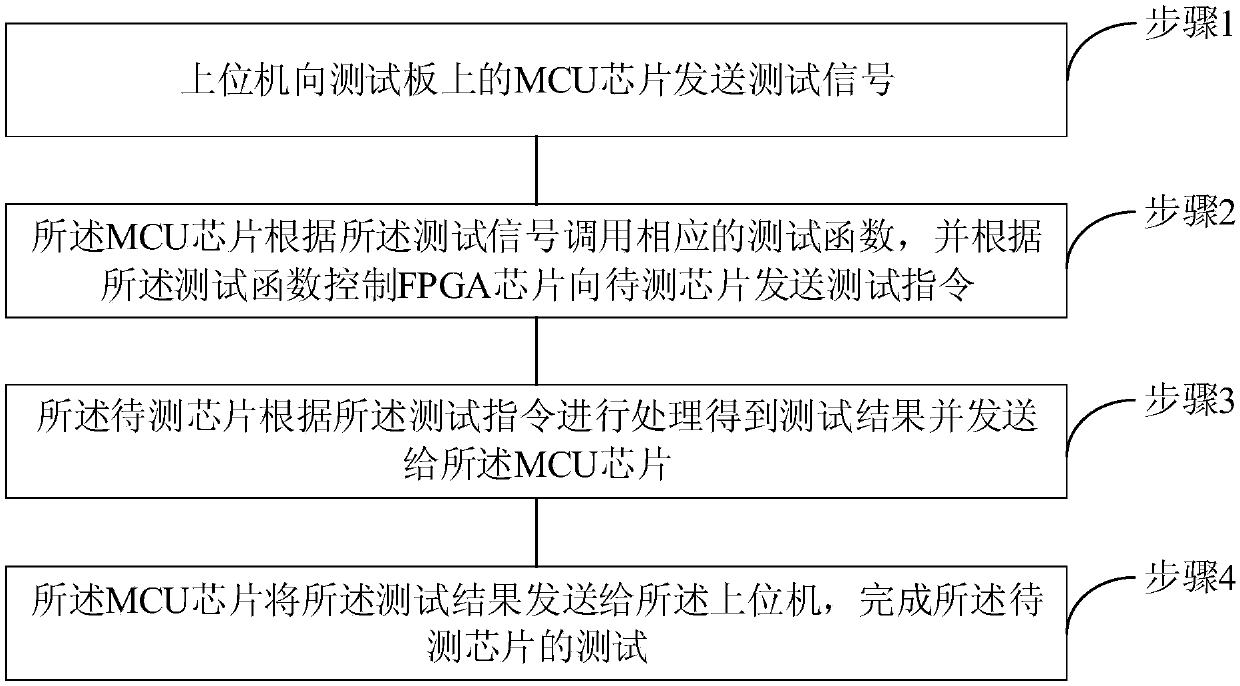

[0080] Step 3: The host computer 7 sends a test signal to the MCU chip 6 on the test board.

[0081] Step 4: The MCU chip 6 calls a corresponding test function according to the test signal, and controls the FPGA chip 5 to send a test command to the CPLD chip to be tested according to the test function.

[0082] Step 5: The CPLD chip to be tested performs processing according to the test instruction to obtain ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com