A wide XOR circuit optimization method

An optimization method and circuit technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., to achieve the effect of reducing the running time, area and delay of logic synthesis

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

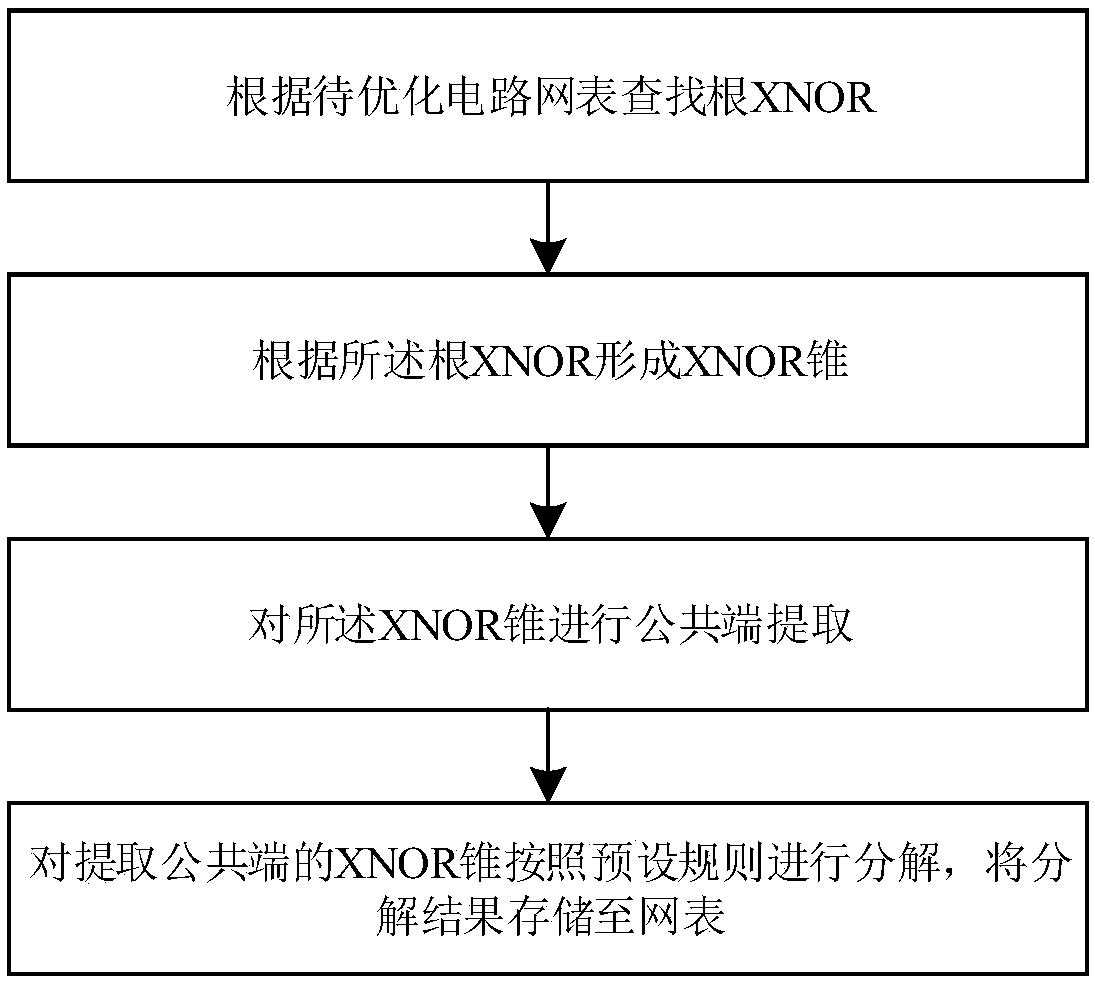

[0044] figure 1 A flow chart of a broadband or circuit optimization method provided by an embodiment of the present invention, including:

[0045] Find the root XNOR according to the netlist of the circuit to be optimized;

[0046] forming an XNOR cone from said root XNOR;

[0047] Carry out common end extraction to described XNOR cone;

[0048] Decompose the XNOR cone according to the preset rules, and store the decomposition results in the netlist.

[0049] In the logic synthesis system, XNOR optimization is specially treated separately, and the general combinational logic optimization (two-level logic optimization and multi-level logic optimization) for general combinational logic, such as AND gate and OR gate, is not processed.

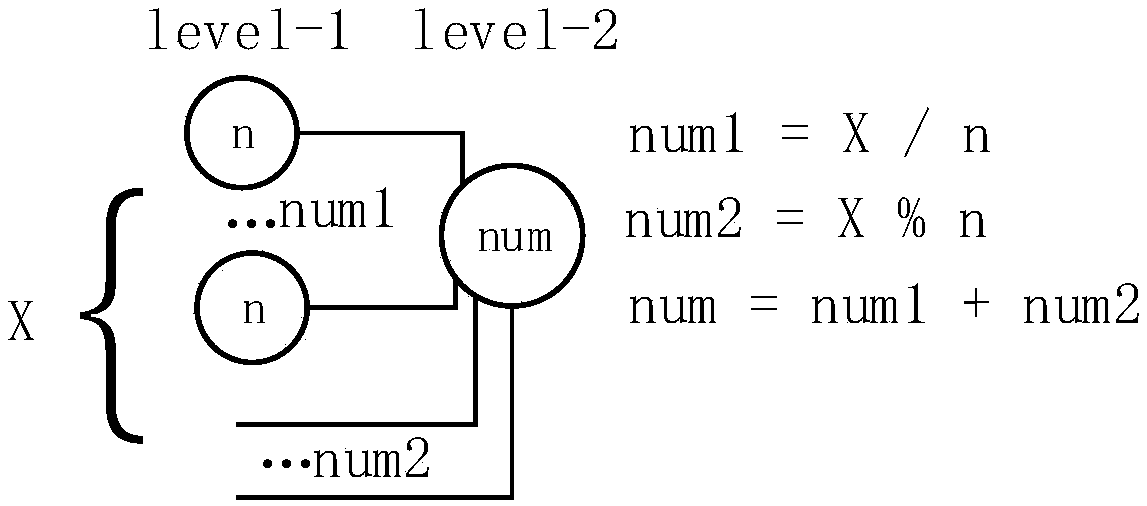

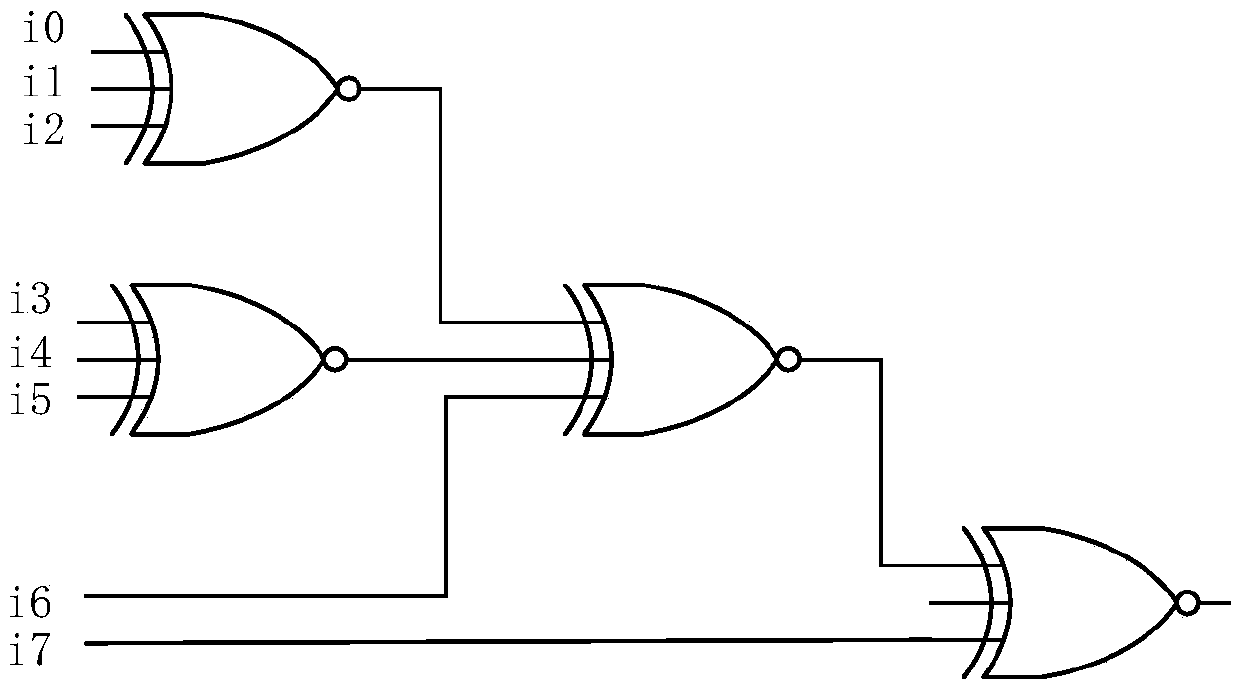

[0050] XNOR optimization is divided into two parts in the process, which run at the beginning and end of combinatorial logic optimization respectively. At the beginning of logic optimization, related XNOR gates are grouped, and the grouped res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More