Chip packaging method and chip packaging structure

A chip packaging structure and chip packaging technology, applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve problems such as chip stacking bottlenecks, and achieve the effects of easy operation, reduced adverse effects, and avoid warping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

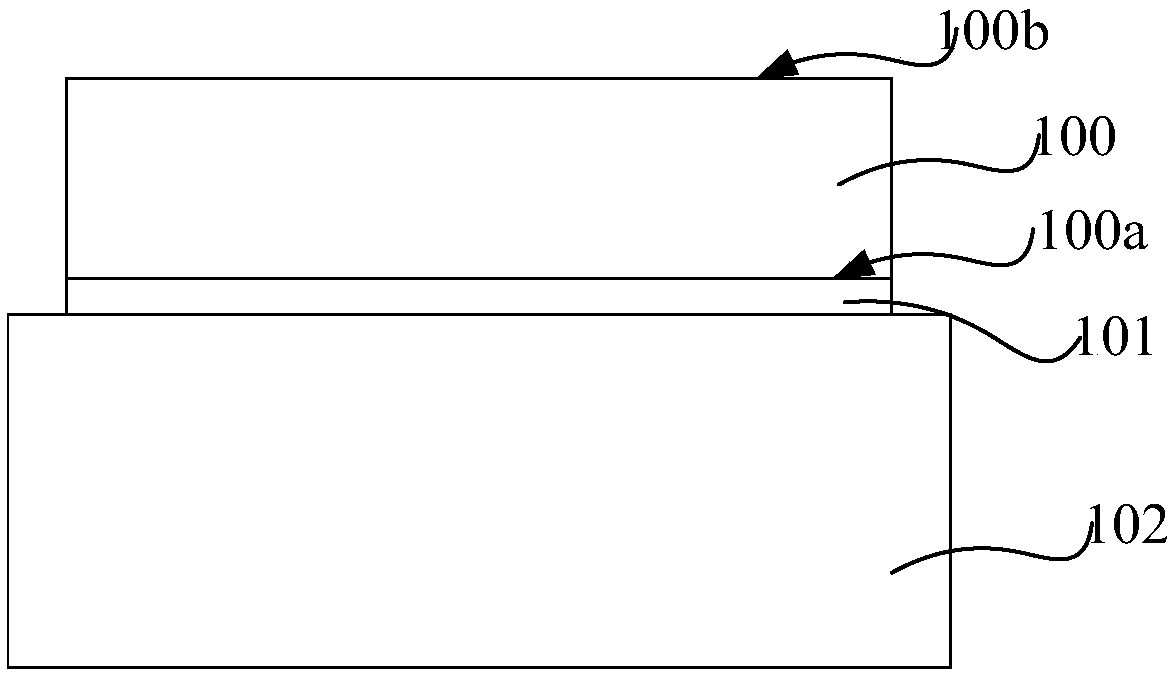

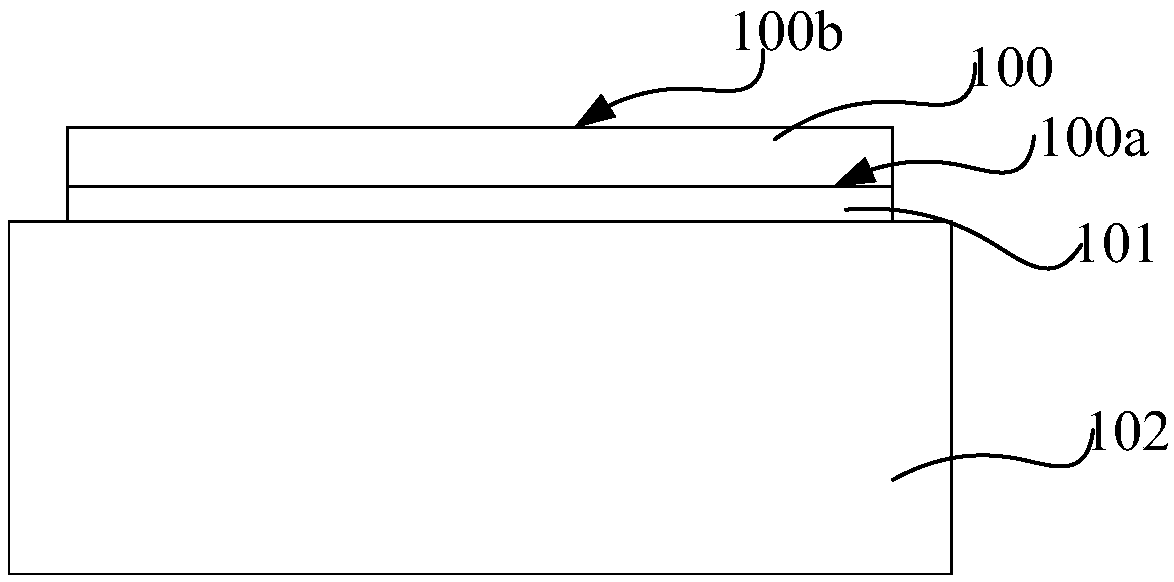

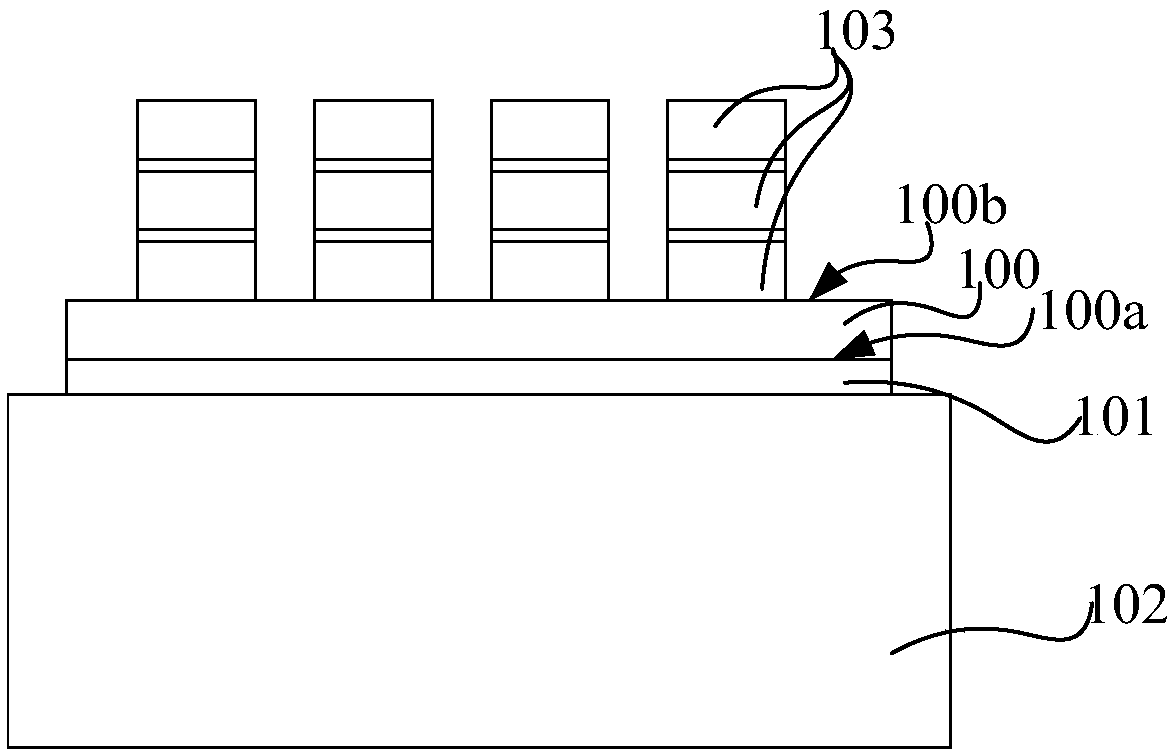

[0037] At present, the key processes in CoW packaging technology include Device Wafer Backside Grinding, Die Stacking and Die Saw. Auxiliary structures commonly used in thinning and wafer stacking processes are usually pasted on the front of the component wafer as a support for back thinning, or pasted on the front or back of the back-thinned component wafer for chip stacking support. Please refer to Figures 1A to 1C , a CoW encapsulation process includes:

[0038] First, please refer to Figure 1A , affixing the front side 100a of the element wafer 100 to a carrier 102 through a thermal tape (Thermal tape) 101, for supporting the element wafer 100 in subsequent processes;

[0039] Then, refer to Figure 1B , the back side 100b of the component wafer 100 is thinned by using a chemical mechanical polishing (CMP) process, so as to expose through silicon vias (Through Silicon Vias) in the component wafer 100 from the back side 100b of the component wafer 100 Via, TSV) and o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More