Low-voltage-difference linear voltage regulator system

A low-dropout linear and voltage regulator technology, applied in the electrical field, can solve the problems of weakening product endurance, low conversion efficiency of LDO circuits, and limited use.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] The low dropout linear voltage regulator system of the present invention will be further described in detail below in conjunction with the accompanying drawings.

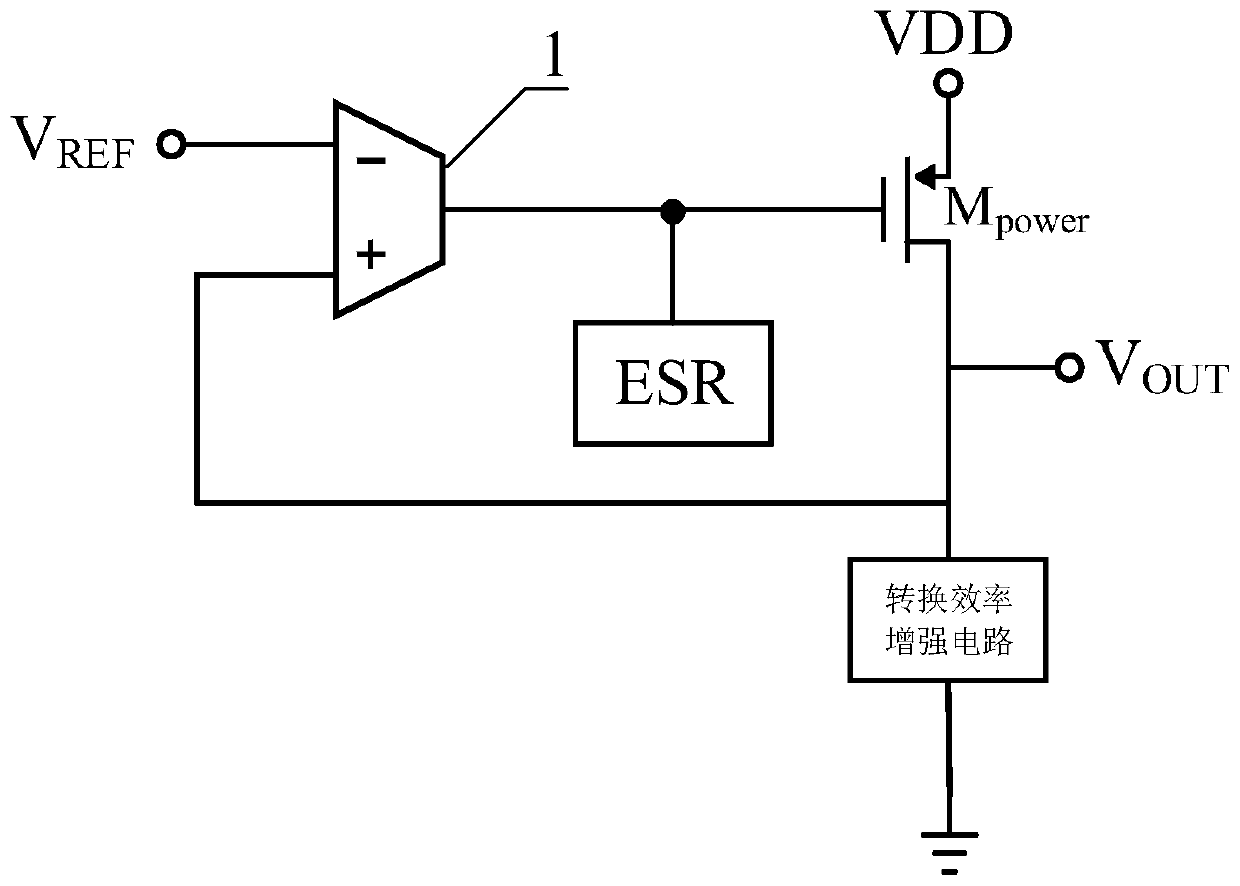

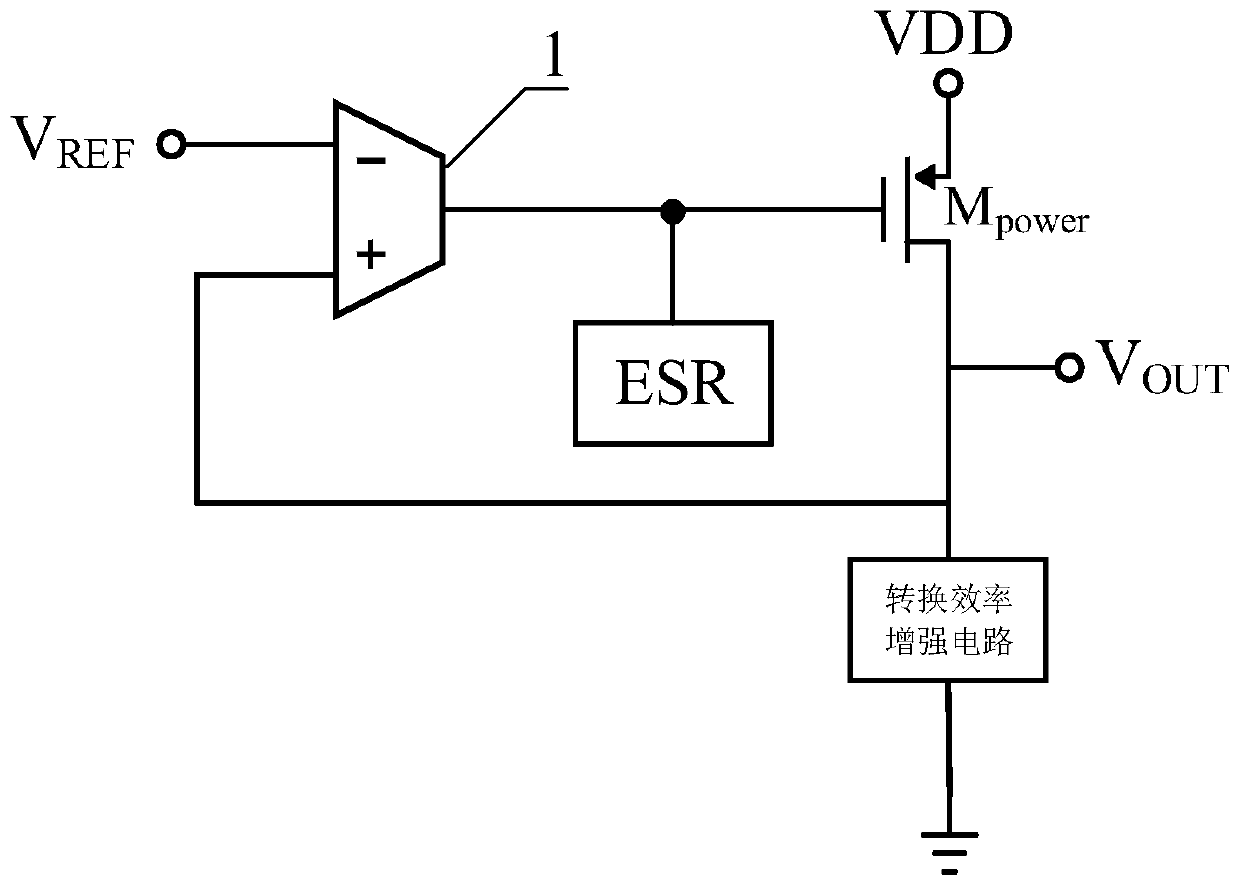

[0061] Such as figure 1 , figure 2 As shown, the system consists of error amplifier 1, slew rate enhancement circuit (ESR circuit), conversion efficiency enhancement circuit, power tube M power composition. V REF It is the reference voltage provided by other modules, often provided by the bandgap reference circuit, VDD is the input power supply voltage signal, which can be provided by the battery or the voltage signal generated after the DC-DC conversion circuit, V OUT It is the output signal of LDO, which is used to provide power supply voltage signal to other circuits.

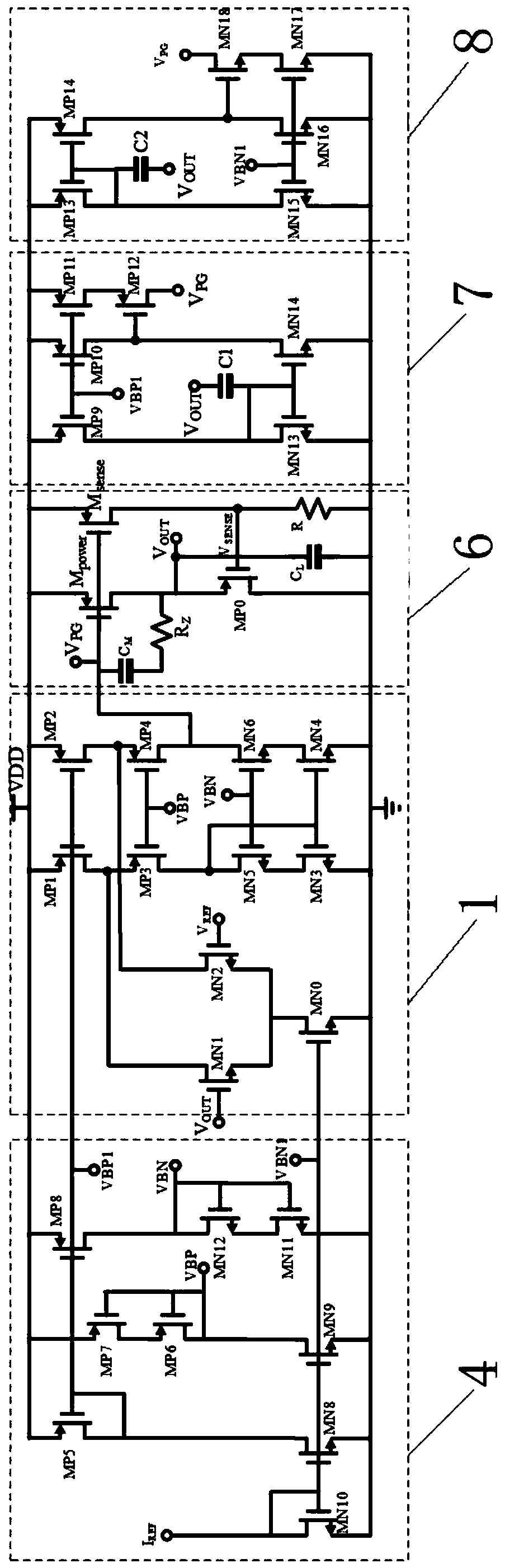

[0062] Specific examples of this design figure 2 shown, but not limited to figure 2 form. figure 2 The embodiment is composed of a module bias circuit 4 , an error amplifier 1 , an output power tube and a current efficiency enhan...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More