Fabrication method of asymmetric surface channel field effect transistor and power device

An asymmetric, transistor-based technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as low breakdown voltage, achieve the effect of increasing breakdown voltage and operating voltage, and increasing power density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to make the technical problems, technical solutions and beneficial effects to be solved by the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0045] Please also refer to Figure 1 to Figure 5 , the preparation method of the asymmetric surface channel field effect transistor provided by the present invention will now be described. The preparation method of the asymmetric surface channel field effect transistor comprises the following steps:

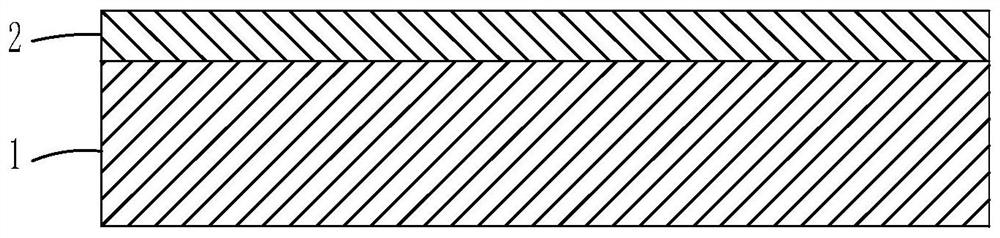

[0046] A metal mask layer 2 is deposited on the surface channel epitaxial layer 1, see figure 1 ;

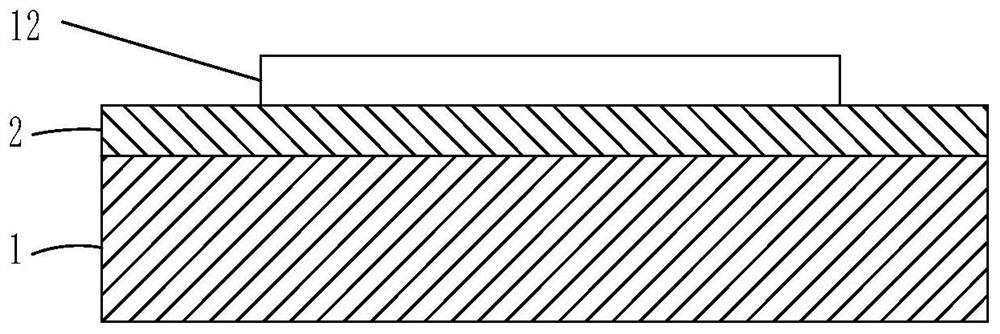

[0047] Prepare the first photoresist layer 12 on the metal mask layer 2, see figure 2 ;

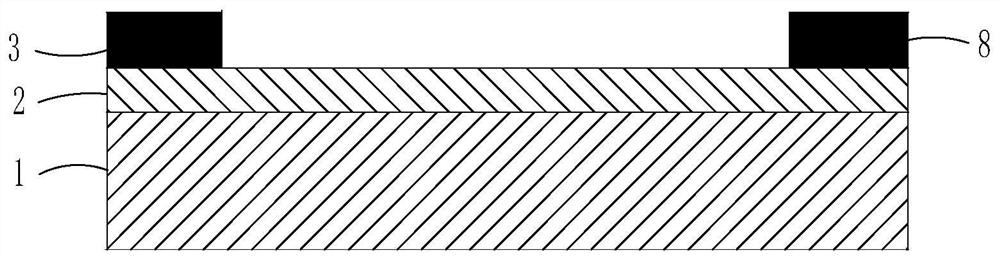

[0048] Exposure, development, forming source region graphics and drain ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More