TEC(thermoelectric cooler)-free uncooled infrared focal plane array reading circuit

A focal plane array and uncooled infrared technology, which is applied in the field of uncooled infrared focal plane array, can solve the problems that the output bias point cannot be automatically determined, noise, and the blind element resistance of the pixel are not equal, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0053] Such as figure 2 The circuit block diagram shown discloses a TEC-free uncooled infrared focal plane array readout circuit, including a bias voltage generation circuit 2, a column-level analog front-end circuit 3 and a row-level circuit 1; the bias voltage generation circuit 2 is connected to the The column-level analog front-end circuit 3 is connected to the row-level circuit 1;

[0054] The row-level circuit 1 includes a row-level image pixel and a row selection switch; the row-level circuit 1 is controlled by the row selection switch and can output a third bias voltage;

[0055] The input terminal of the bias voltage generating circuit 2 is connected to the output terminal of the row-level circuit 1, and is used to generate and output the first bias voltage and the second bias voltage together with the third bias voltage when there is a constant voltage input Voltage;

[0056] The input end of the column-level analog front-end circuit 3 is connected to the...

Embodiment 2

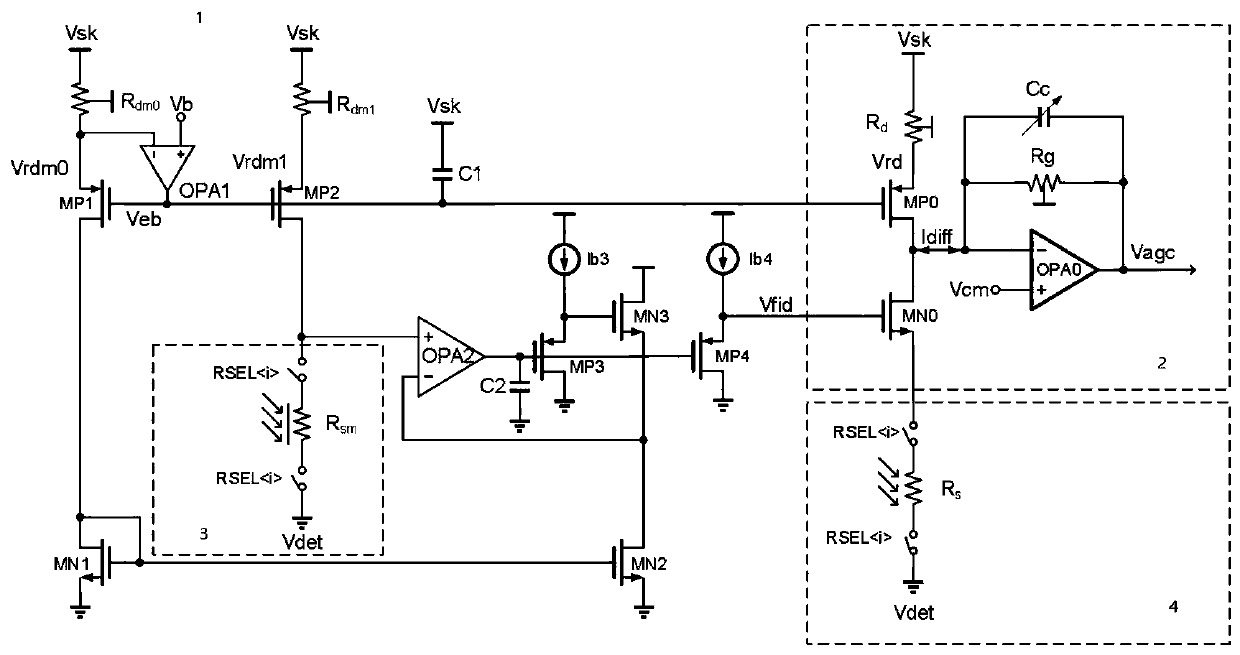

[0086] In one embodiment of the present invention, it is disclosed as image 3 The schematic diagram of the circuit structure shown; includes a bias generating circuit 1, a column-level analog front-end circuit 2, a row-level circuit 3 and a pixel-level circuit 4; wherein, the bias generating circuit 1 includes at least a first bias generating sub-circuit and a second A bias voltage generation subcircuit; the first bias voltage generation subcircuit and the second bias voltage generation subcircuit respectively output the first bias voltage and the second bias voltage;

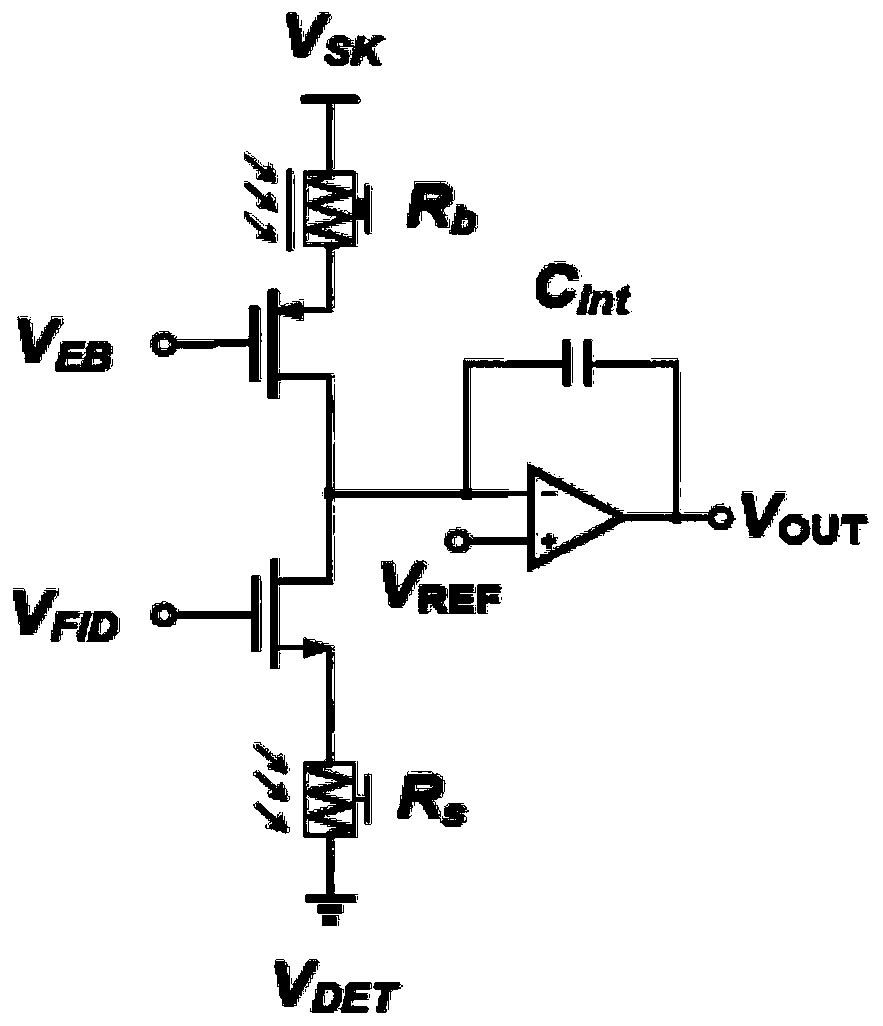

[0087] Wherein, the first bias voltage generation sub-circuit may include a first PMOS transistor MP1, a second PMOS transistor MP2, a first NMOS transistor MN1, a second NMOS transistor MN2, a first operational amplifier OPA1, a second operational amplifier OPA2, a first mirror image Blind element R dm0 , the second mirror blind element R dm1 , decoupling capacitor C1 and power supply Vsk; it should ...

Embodiment 3

[0186] In another embodiment of the present invention, disclosed as Image 6 The schematic diagram of the circuit structure shown; includes a bias generating circuit 1, a column-level analog front-end circuit 2, a row-level circuit 3 and a pixel-level circuit 4; wherein, the bias generating circuit 1 includes at least a first bias generating sub-circuit and a second A bias voltage generation subcircuit, the first bias voltage generation subcircuit and the second bias voltage generation subcircuit respectively output the first bias voltage and the second bias voltage;

[0187] Wherein, the first bias generation sub-circuit may include a first NMOS transistor MN1, a second NMOS transistor MN2, a third NMOS transistor MN3, a fourth NMOS transistor MN4, a first operational amplifier OPA1, a second operational amplifier OPA2, a first mirror Blind element R dm0 and the second mirror blind element R dm1 ; It should be noted that the first image blind element R dm0 , the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More