Memory and preparation method thereof

A memory and control gate technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of difficult filling of intermediate insulating dielectric layers, low CG-FG coupling capacitance, thick stacking thickness, etc., to achieve filling insulating dielectric Easy layering, improved yield and reliability, and increased effective contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only some structures related to the present invention are shown in the drawings but not all structures.

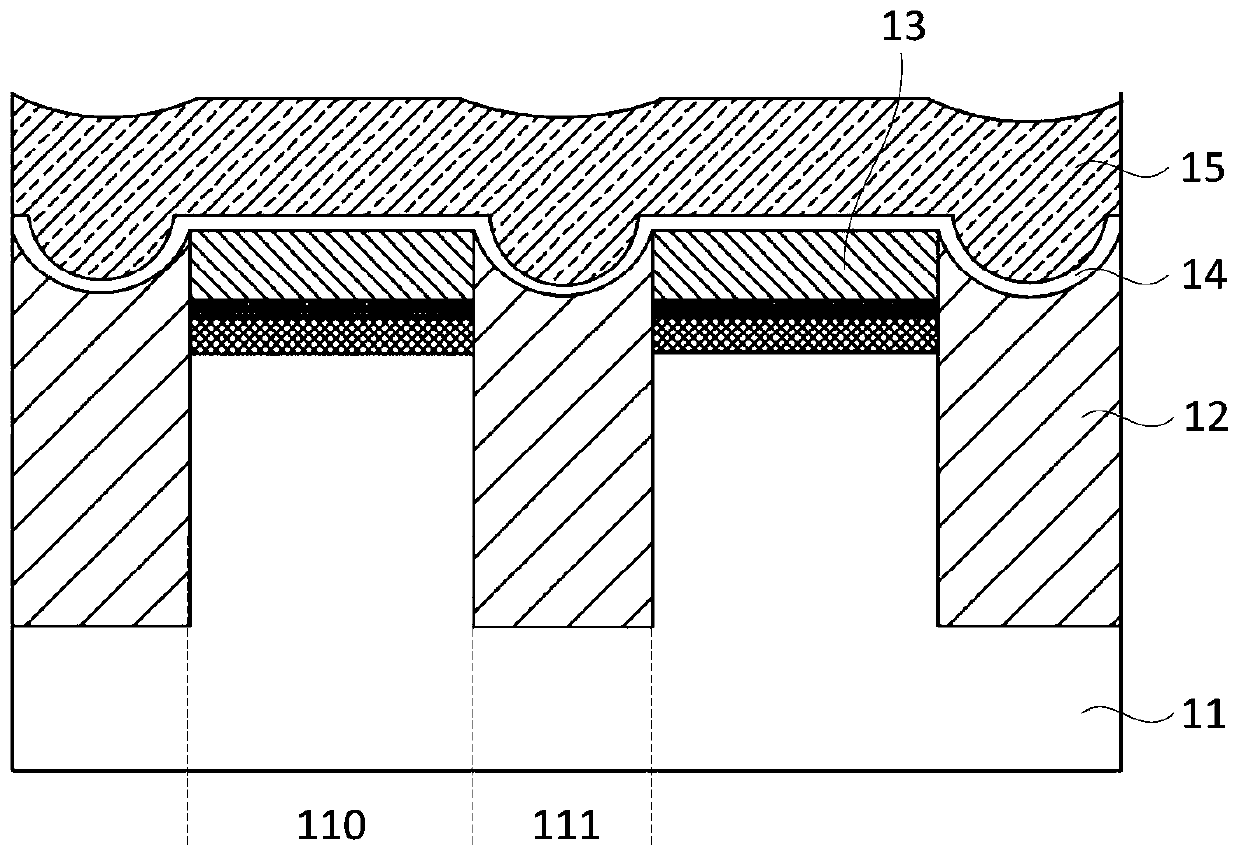

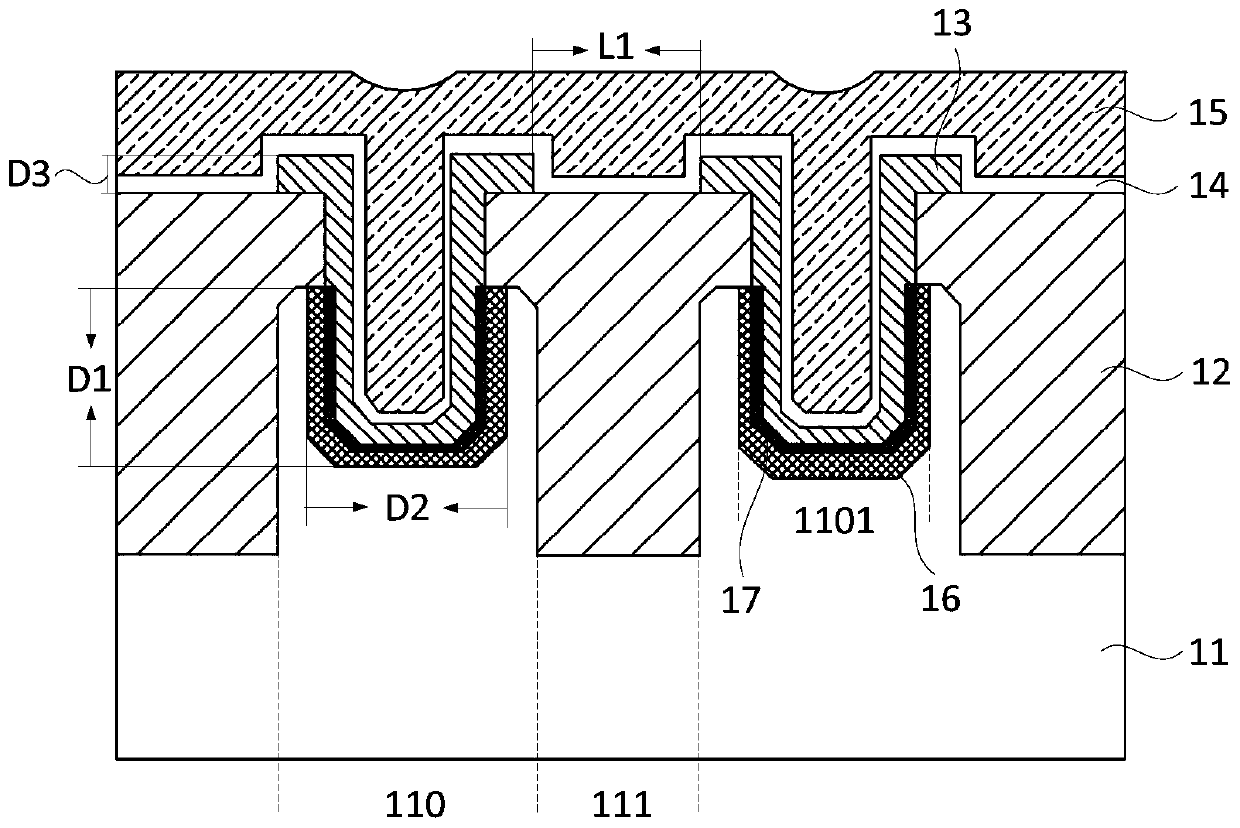

[0045] figure 1 It is a structural schematic diagram of an existing memory. see figure 1 , the memory includes: a base substrate 11, the base substrate 11 includes a plurality of active regions 110 and a plurality of shallow trench isolation regions 111, and the active regions 110 and the shallow trench isolation regions 111 are arranged at intervals. The memory also includes an isolation layer 12 filling the shallow trench isolation region 111, a floating gate 13 on the active region 110, a dielectric layer 14 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More