Probe card, preparation method and chip testing method

A probe card and probe technology, used in semiconductor/solid-state device testing/measurement, electrical components, electrical solid-state devices, etc., can solve the problem of electrode pitch reduction, probe alignment difficulties, and difficulty in ensuring accuracy problems, to ensure effective contact, achieve batch testing, and ensure the effect of testing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to make the purpose, technical solutions and advantages of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the embodiments of the present invention. Obviously, the described embodiments are part of the implementation of the present invention. example, not all examples. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention. In the case of no conflict, the following embodiments and features in the embodiments can be combined with each other.

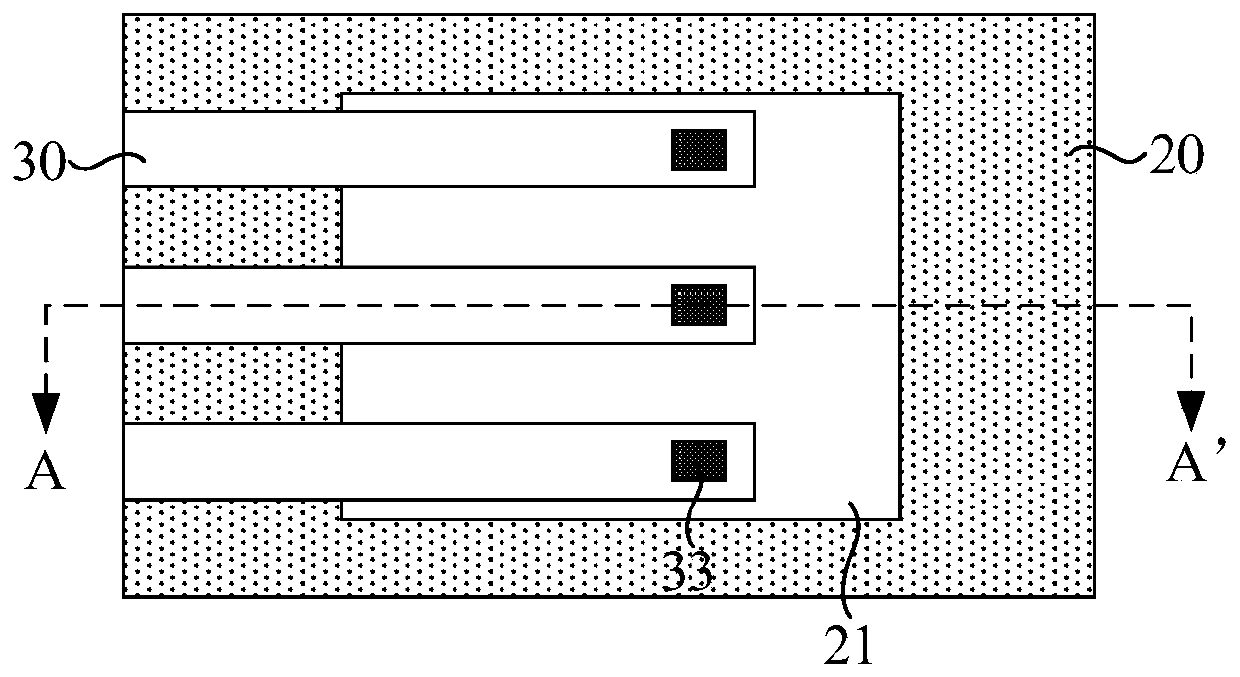

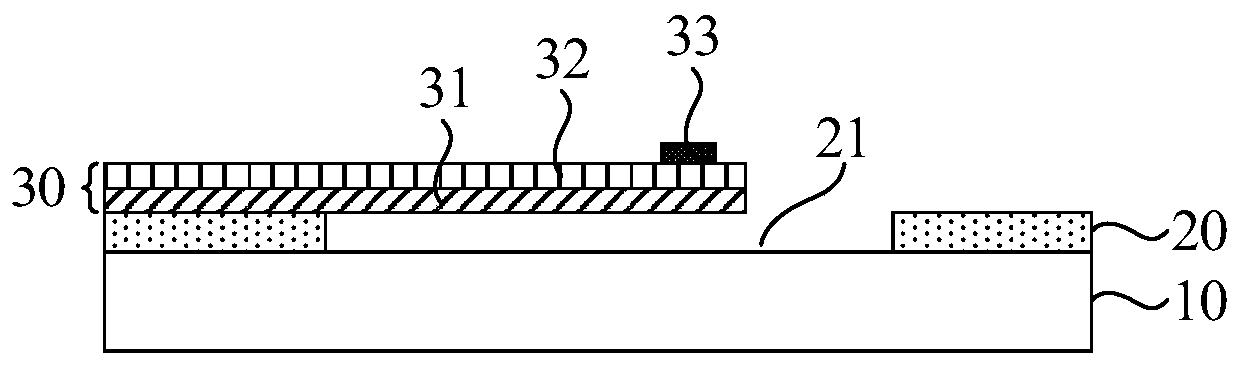

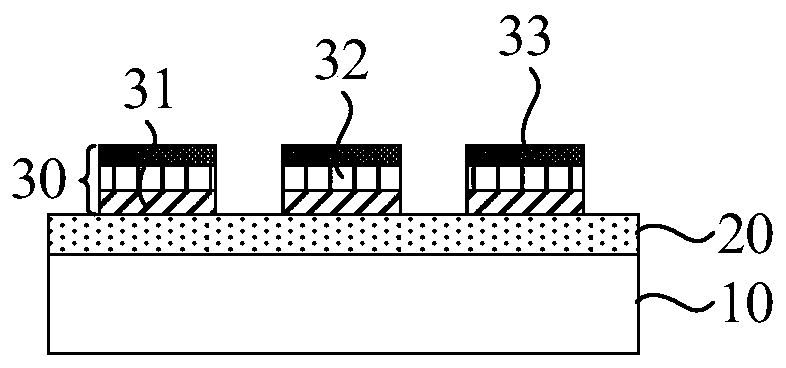

[0045] As mentioned in the background, the test accuracy of the probe card in the prior art cannot meet the test of the existing miniaturized chip. As the chip size becomes smaller, the surface structure of the chip becomes more complex, and it is easy t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More