A method and system for accelerated computing of integrated circuits based on convolutional neural network algorithm

A convolutional neural network and integrated circuit technology, which is applied to the integrated circuit accelerated computing system. The integrated circuit accelerated computing field based on the convolutional neural network algorithm can solve the problem of difficult real-time operation, large amount of operation, and difficult to achieve by the processor. requirements and other issues, to achieve the effect of improving unit utilization, fewer reading times, and reducing the number of times

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

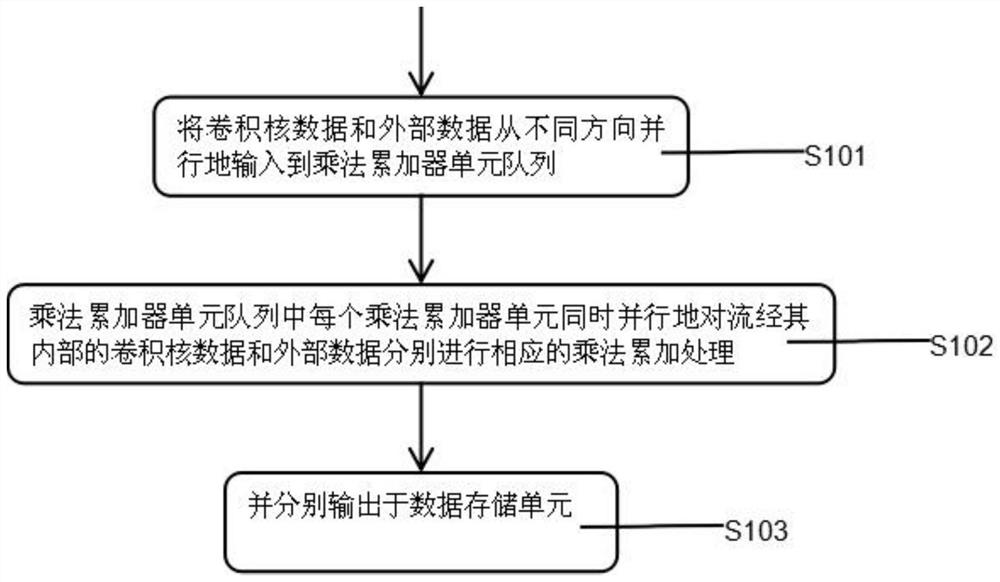

[0109] Embodiment one: if figure 1 As shown, a method for accelerated calculation of an integrated circuit based on a convolutional neural network algorithm includes: inputting convolution kernel data and external data into the multiplication accumulator unit queue S101 in parallel from different directions; A multiplication accumulator unit carries out corresponding multiplication and accumulation processing S102 on the convolution kernel data and external data flowing through it in parallel at the same time, and outputs them to the data storage unit S103 respectively;

[0110] Since the convolution kernel data and external data are input to the multiplication accumulator unit queue in parallel from different directions; each multiplication accumulator unit in the multiplication accumulator unit queue simultaneously parallelizes the convolution kernel data and external data flowing through it Carry out corresponding multiplication and accumulation processing respectively, and...

Embodiment 2

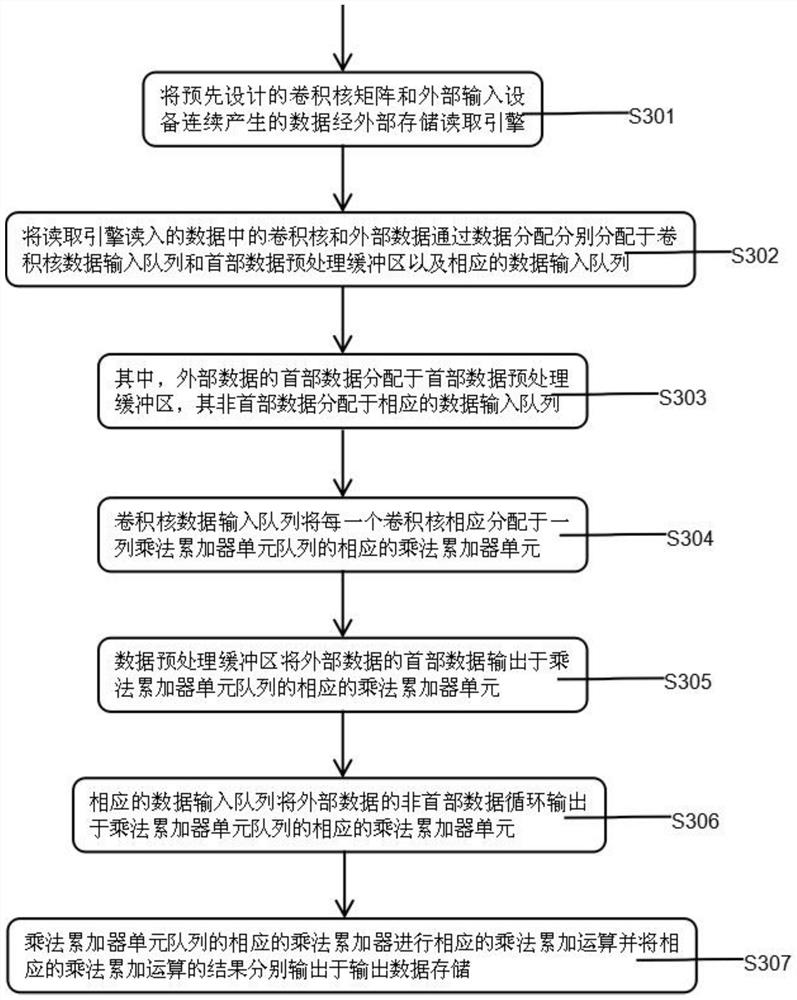

[0179] The following uses image processing as an example to illustrate a method and system for accelerated computing of integrated circuits based on convolutional neural network algorithms, as follows:

[0180] Step 1: Assume that the convolution kernel data matrix is N*N, and the sliding step size is M. For example: N=3, M=1;

[0181] The pre-designed convolution kernel data matrix is put into the external memory. E.g:

[0182] Convolution kernel data 1 Convolution kernel data 4 Convolution kernel data 7 Convolution kernel data 2 Convolution kernel data 5 Convolution kernel data 8 Convolution kernel data 3 Convolution kernel data 6 Convolution kernel data 9

[0183] Step 2: Process the image data continuously output by the camera, subtract the pixels of adjacent images to generate more zeros, compress the sparse matrix, and put it into the external memory. For example, the camera outputs an image, which is the first 3 columns of data...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More