Isolation structure and method for fabricating same

An isolation structure and trench technology, which is used in the manufacture/processing of electromagnetic devices, semiconductor/solid-state device manufacturing, and magnetic field-controlled resistors, etc., can solve problems such as large size, reduce spacing size, maintain isolation effect, and improve The effect of the isolation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

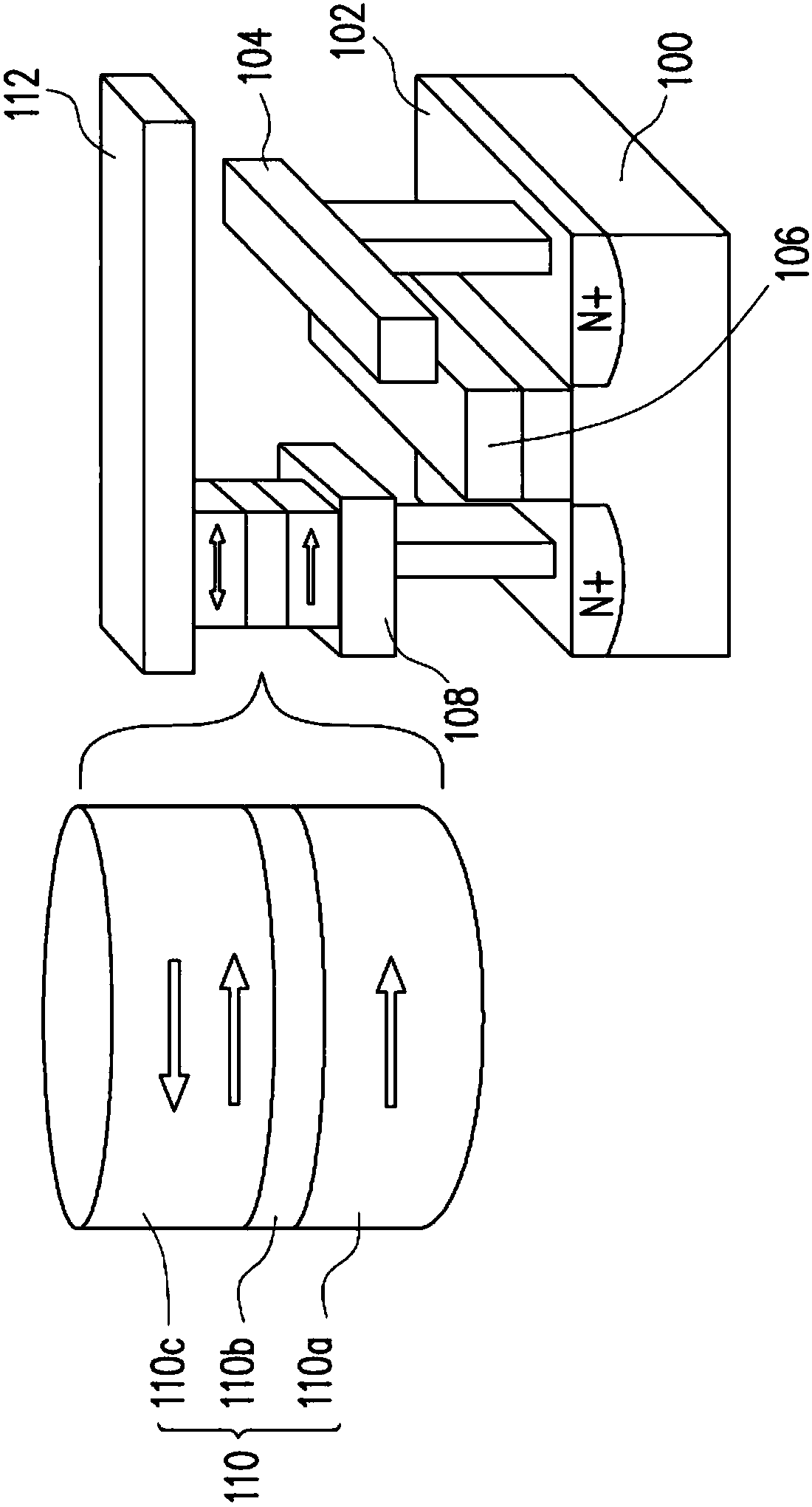

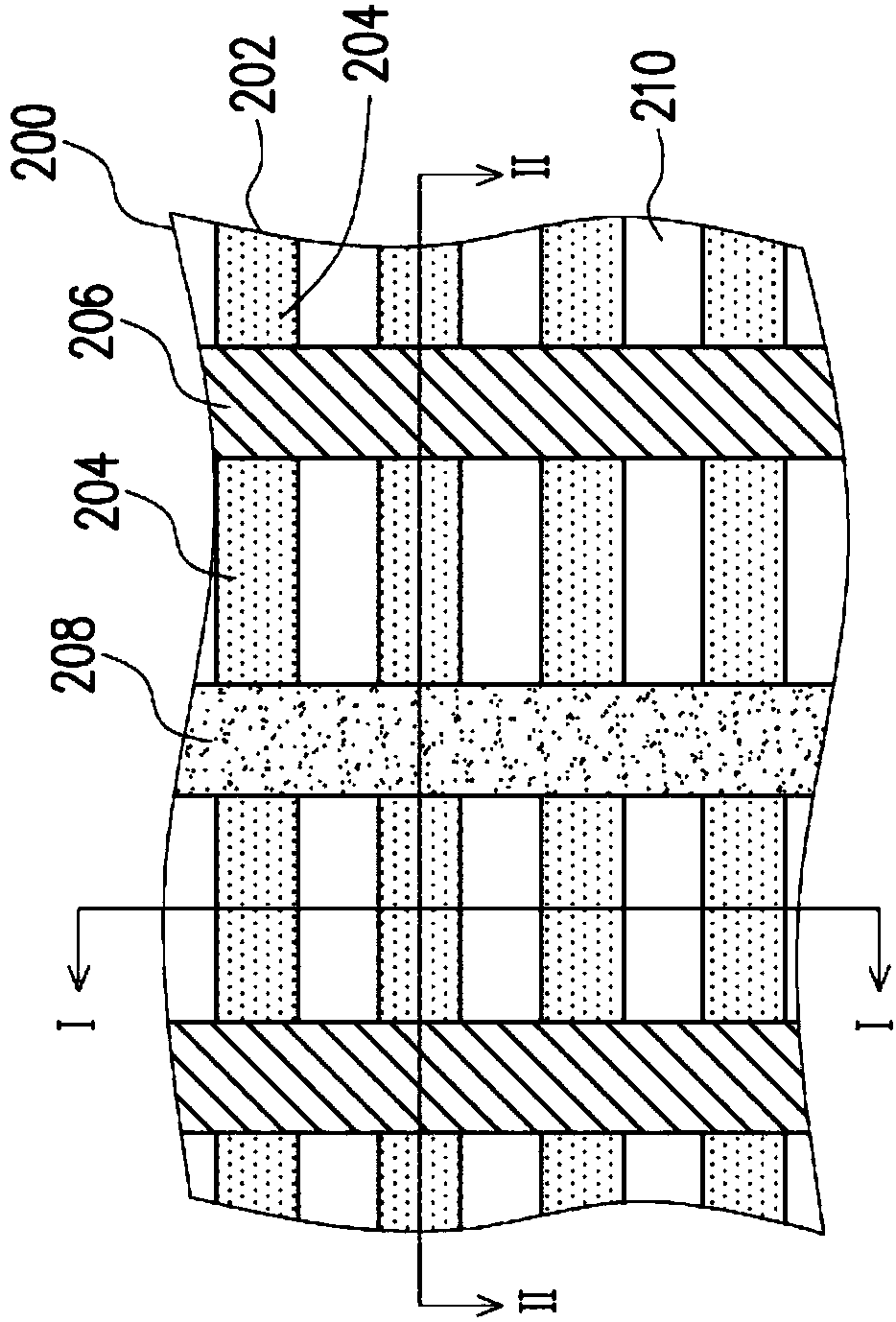

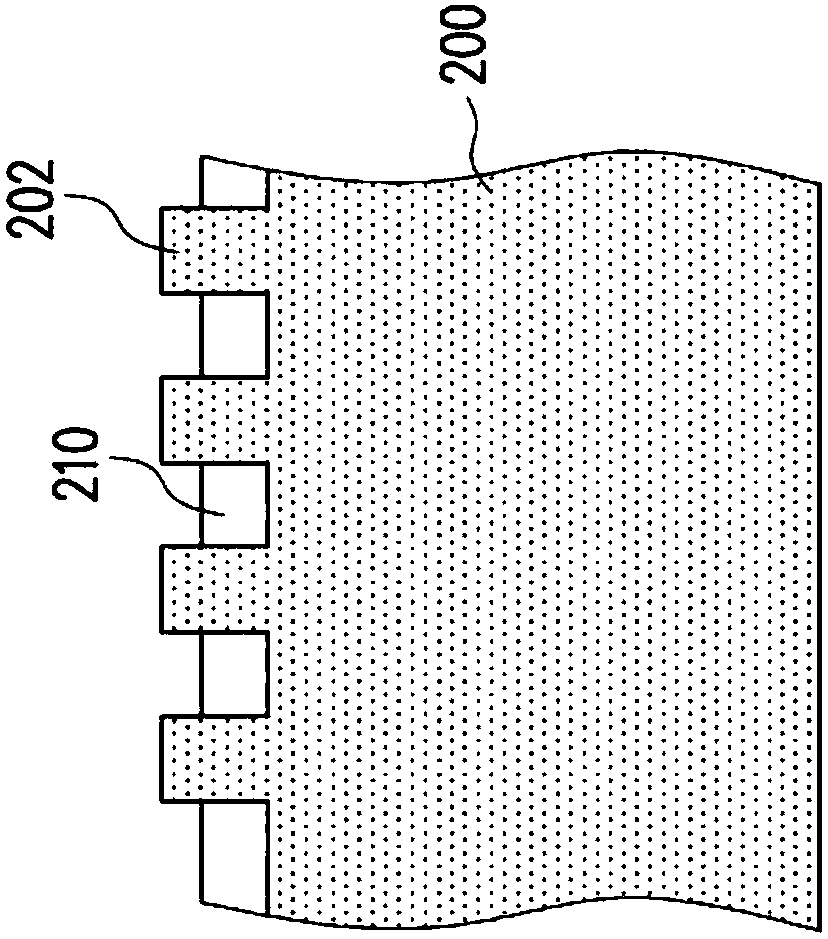

[0062] The present invention relates to isolation techniques for transistors in memory cells of a magnetic random access memory.

[0063] A memory cell at least includes a magnetic tunnel junction (Magnetic Tunnel Junction, MTJ) storage layer and a control transistor. One end of the magnetic tunnel junction storage layer is connected to the drain terminal of the control transistor, and the other end is connected to the bit line. The gate terminal of the control transistor is connected to the word line, and the source terminal is connected to the selection line. Isolation is required between control transistors.

[0064] figure 1 According to an embodiment of the present invention, a schematic diagram of a memory cell structure of a general magnetic random access memory is shown. refer to figure 1, the basic structure of the memory cell of the magnetic random access memory, including the control transistor, which is formed on the substrate 100 . The gate terminal 106 of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More