Heterogeneous multi-core microprocessor based on multi-layer bus

A core microprocessor and bus technology, applied in the field of heterogeneous multi-core microprocessors, can solve problems such as poor scalability, complex hardware structure, and large software changes, so as to enhance processing efficiency, reduce communication delay, and improve computing performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

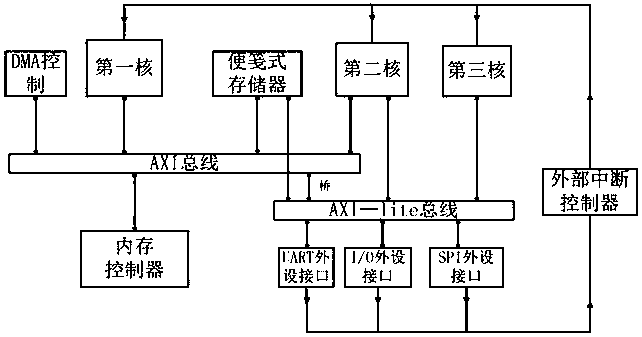

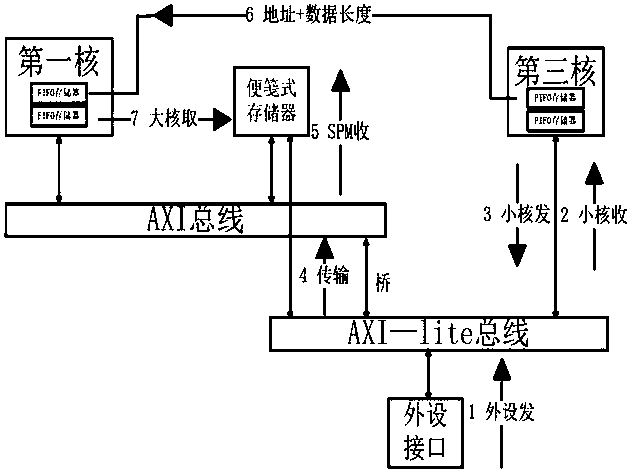

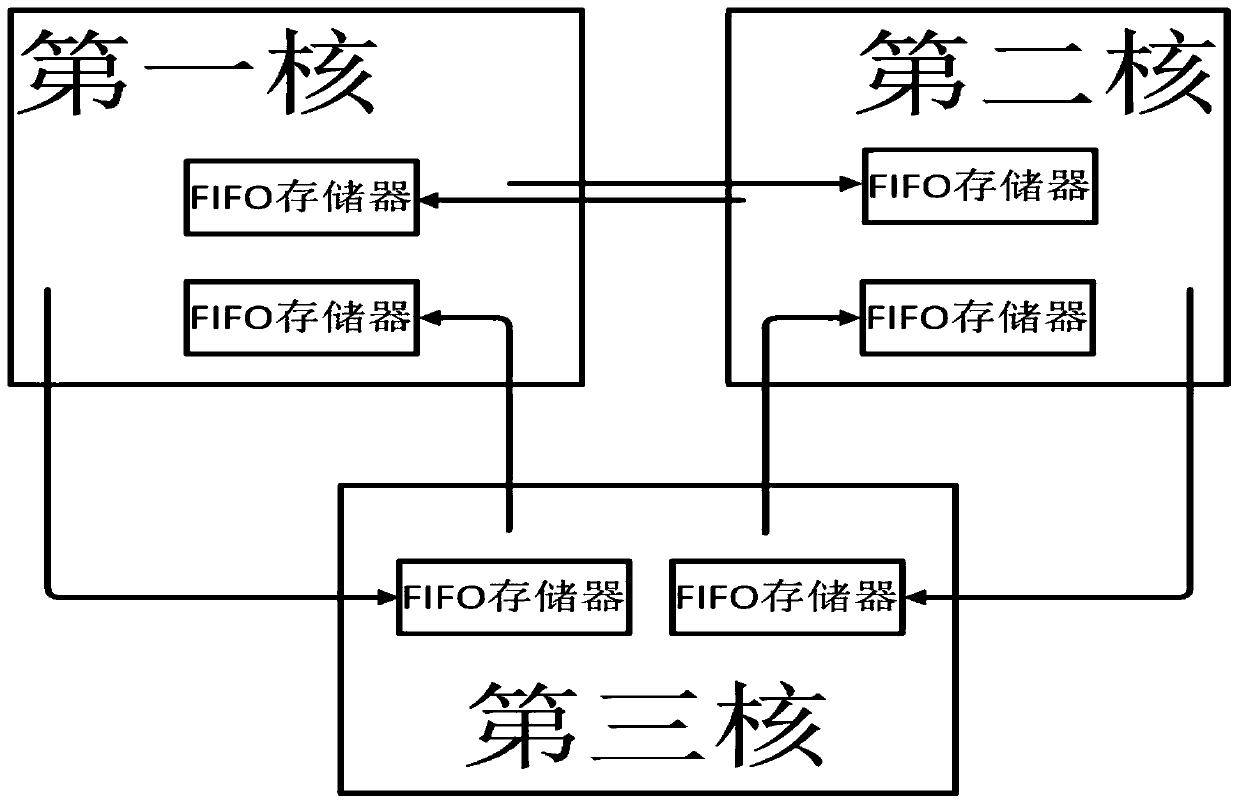

[0023] A kind of heterogeneous multi-core microprocessor based on the multi-layer bus of the present invention uses 3 32-bit RISC-CPUs as heterogeneous processor cores: the first core, the second core, and the third core are examples for specific structures Description: if figure 1 Shown, a kind of heterogeneous multi-core microprocessor based on multi-layer bus of the present invention comprises the processing core of a plurality of uniform addressing, and a plurality of processing cores has different pipeline structures, and between a plurality of processing cores is passed through the AXI with bridging Bus connection, AXI bus with a bridge is connected to a pad memory, and data packets are sent and stored in the process of reading through the pad memory between every two processing cores, and each two processing cores are directly sent Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More