Etching method of semiconductor device and three-dimensional memory

A semiconductor and memory technology, applied in the field of semiconductor devices and their manufacturing, can solve the problems that the spacing cannot be further reduced, the device yield rate is reduced, and the layout of the three-dimensional memory array area is hindered, so as to improve the yield rate and work stability, and avoid offset Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

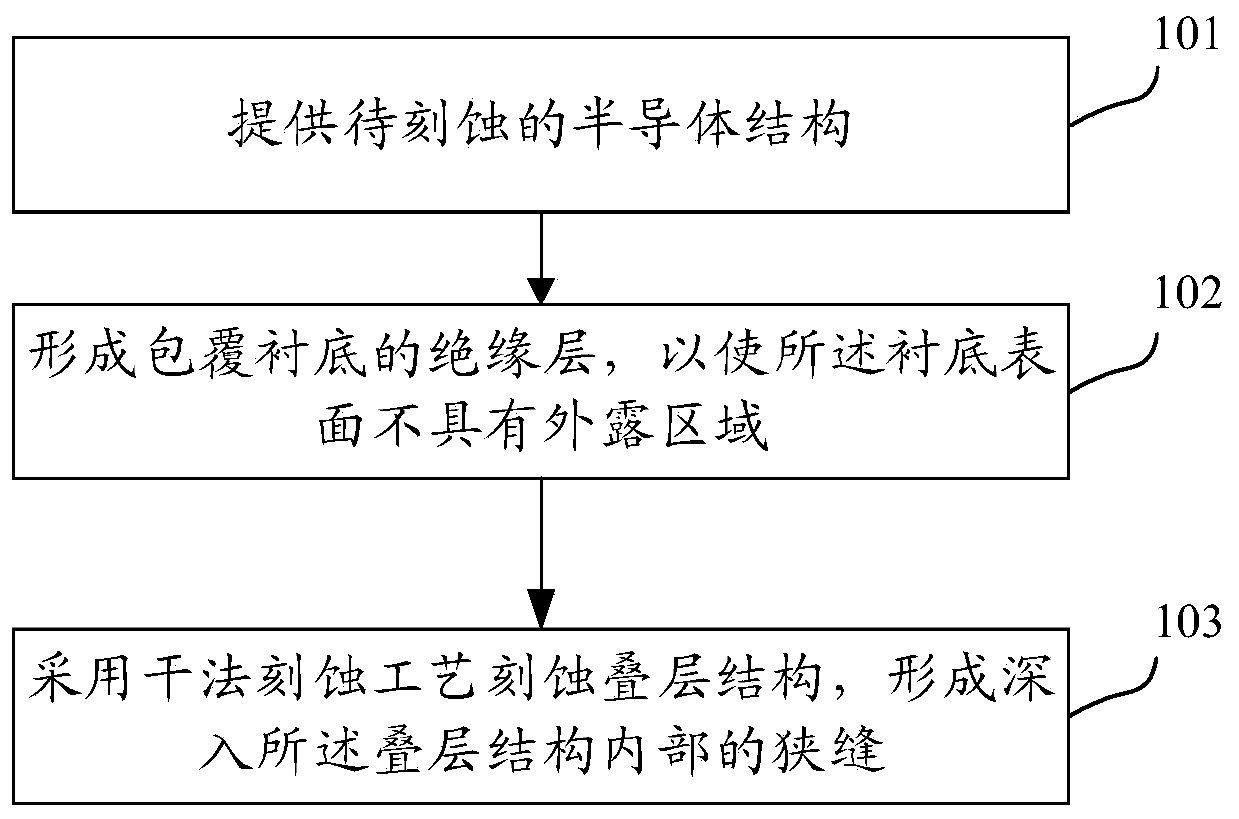

[0047] This embodiment provides an etching method for a semiconductor device; for details, please refer to the attached figure 2 . As shown, the method includes the following steps:

[0048] Step 101, provide a semiconductor structure to be etched, the semiconductor structure at least includes a semiconductor substrate, a stacked structure on the semiconductor substrate, and a first conductive column inside the stacked structure, the first The conductive pillar is electrically connected to the semiconductor substrate;

[0049] Step 102, forming an insulating layer covering the semiconductor substrate, so that the surface of the semiconductor substrate has no exposed area;

[0050] Step 103: Etching the stacked structure by using a dry etching process to form a slit deep inside the stacked structure.

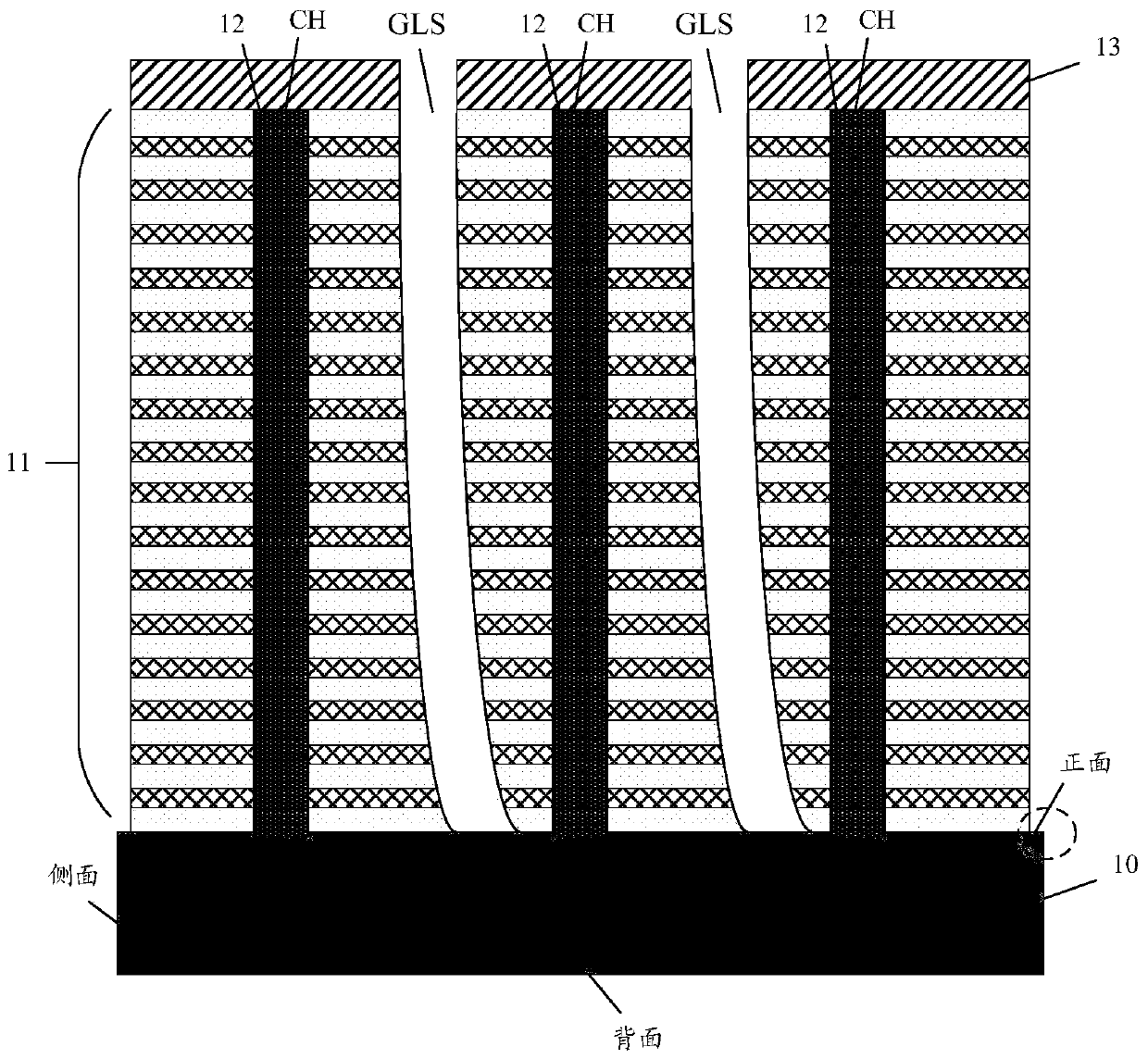

[0051] It should be understood that the technical solution of the present invention is not limited to solving the offset problem generated when etching GLS in a three-dimensi...

Embodiment 2

[0073] This embodiment provides a method for manufacturing a three-dimensional memory, including the semiconductor device etching method described in any of the foregoing embodiments; for details, please refer to the attached Figure 5 . As shown, the method includes the following steps:

[0074] Step 201, providing a semiconductor substrate, and forming a stacked structure on the semiconductor substrate;

[0075] Step 202: Etching the stacked structure to form a channel via hole penetrating through the stacked structure, forming a channel structure inside the channel via hole, the channel structure at least includes a channel layer, the The channel layer is electrically connected to the semiconductor substrate;

[0076] Step 203, forming an insulating layer covering the semiconductor substrate, so that there is no exposed area on the surface of the semiconductor substrate;

[0077] Step 204 , etching the stacked structure by using a dry etching process to form a gate slit ...

Embodiment 3

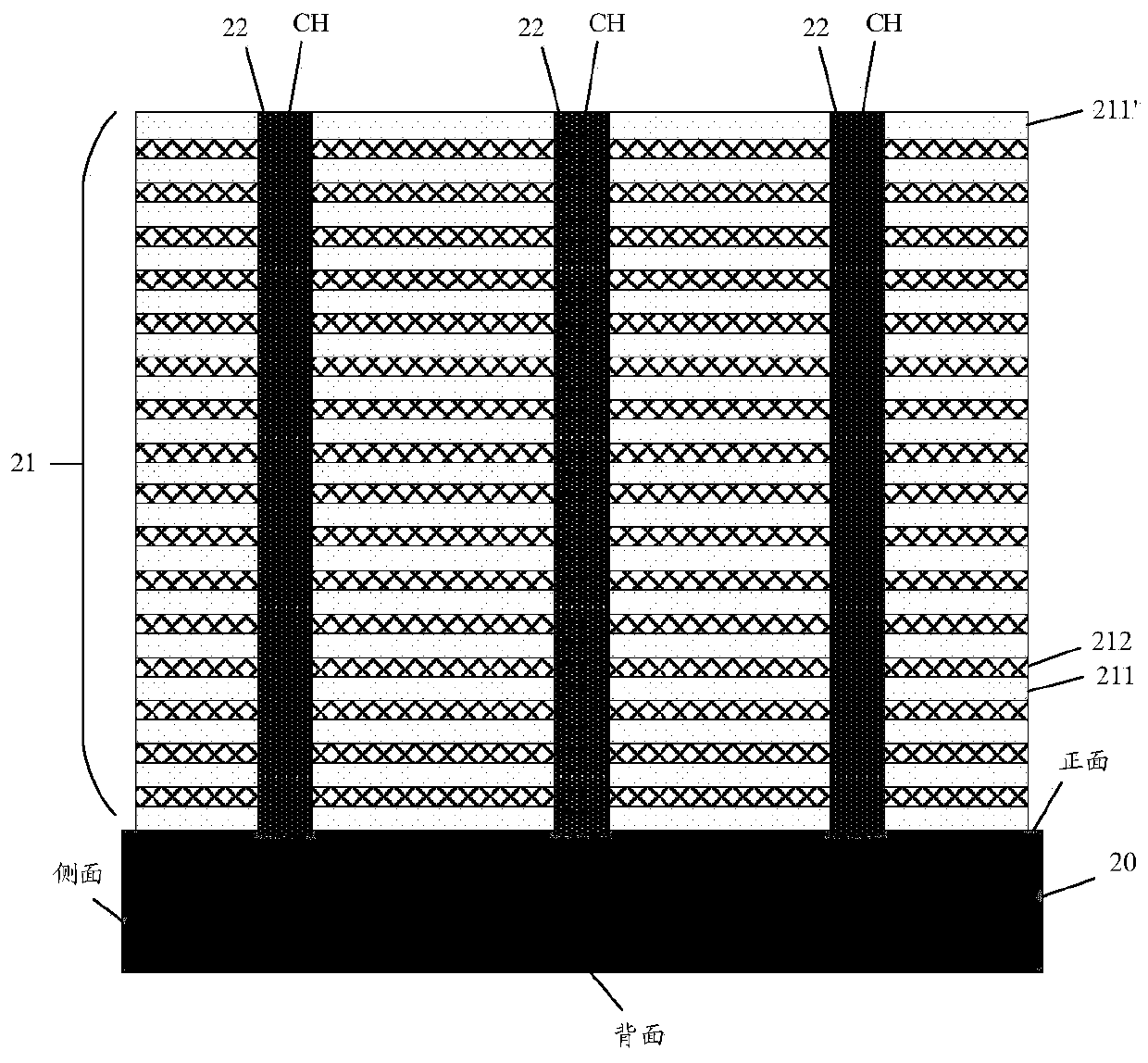

[0080] This embodiment provides a three-dimensional memory, for details, please refer to the attached Figure 3d . As shown in the figure, the three-dimensional memory includes: a semiconductor substrate 20, a stacked structure 21 located on the semiconductor substrate 20, and a channel hole CH penetrating through the stacked structure 21; the inside of the CH is provided with channel layer 22, the channel layer 22 is electrically connected to the semiconductor substrate 20; the three-dimensional memory also includes an insulating layer 24 covering the semiconductor substrate 20, so that the surface of the semiconductor substrate 20 is not have exposed areas.

[0081] In a specific embodiment, the laminated structure 21 includes a plurality of alternately arranged first material layers 211 and second material layers 212 . The first material layer 211 is a dielectric layer; the second material layer 212 is a gate layer or a dummy gate layer.

[0082] In a specific embodiment...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More