Storage system for supporting calculation in storage and calculation method

A storage system and computing technology, applied in information storage, static memory, digital memory information, etc., can solve the problem of no computing memory, and achieve the effect of reducing data transmission, cutting and power consumption wall effect, and reducing time overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

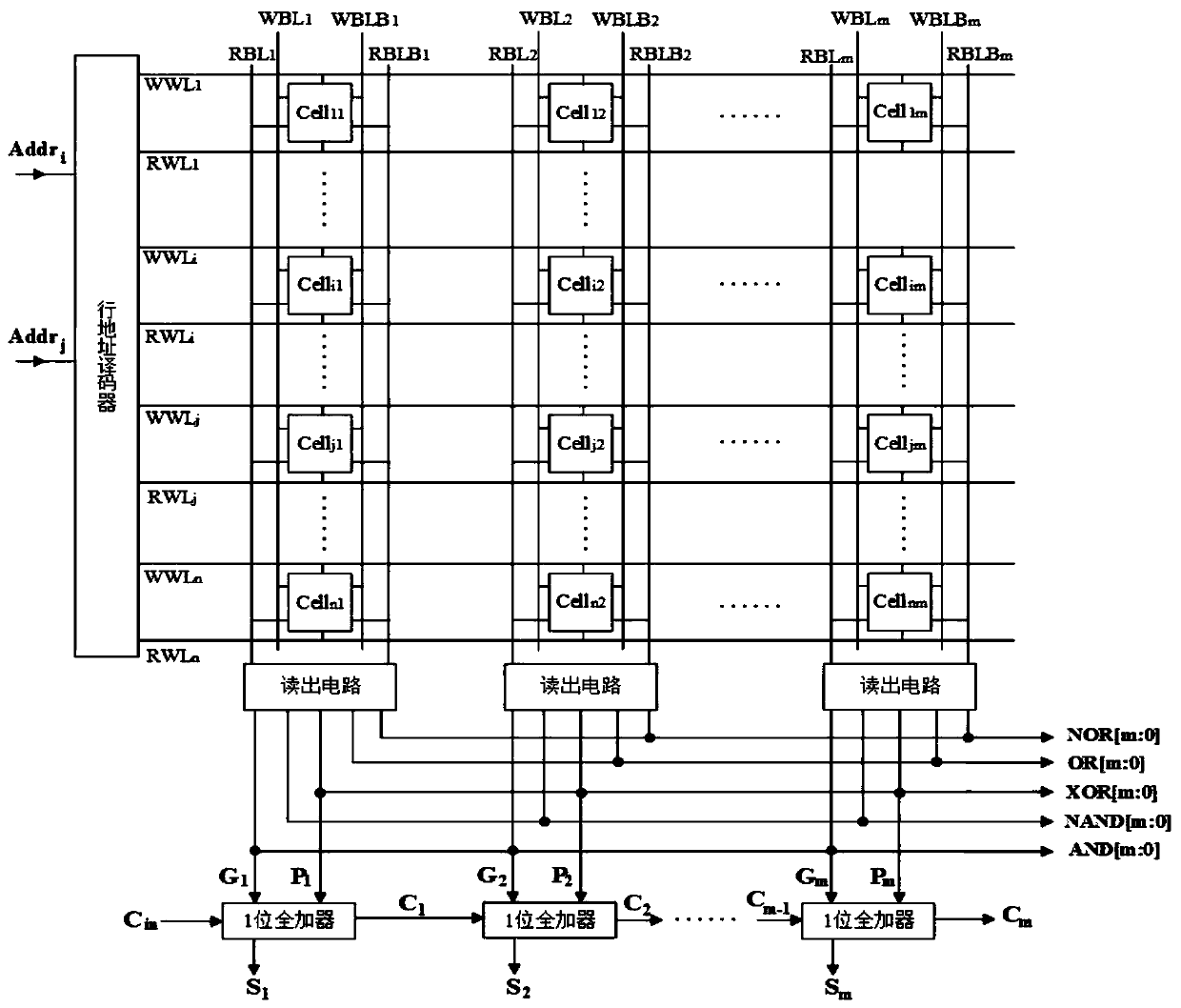

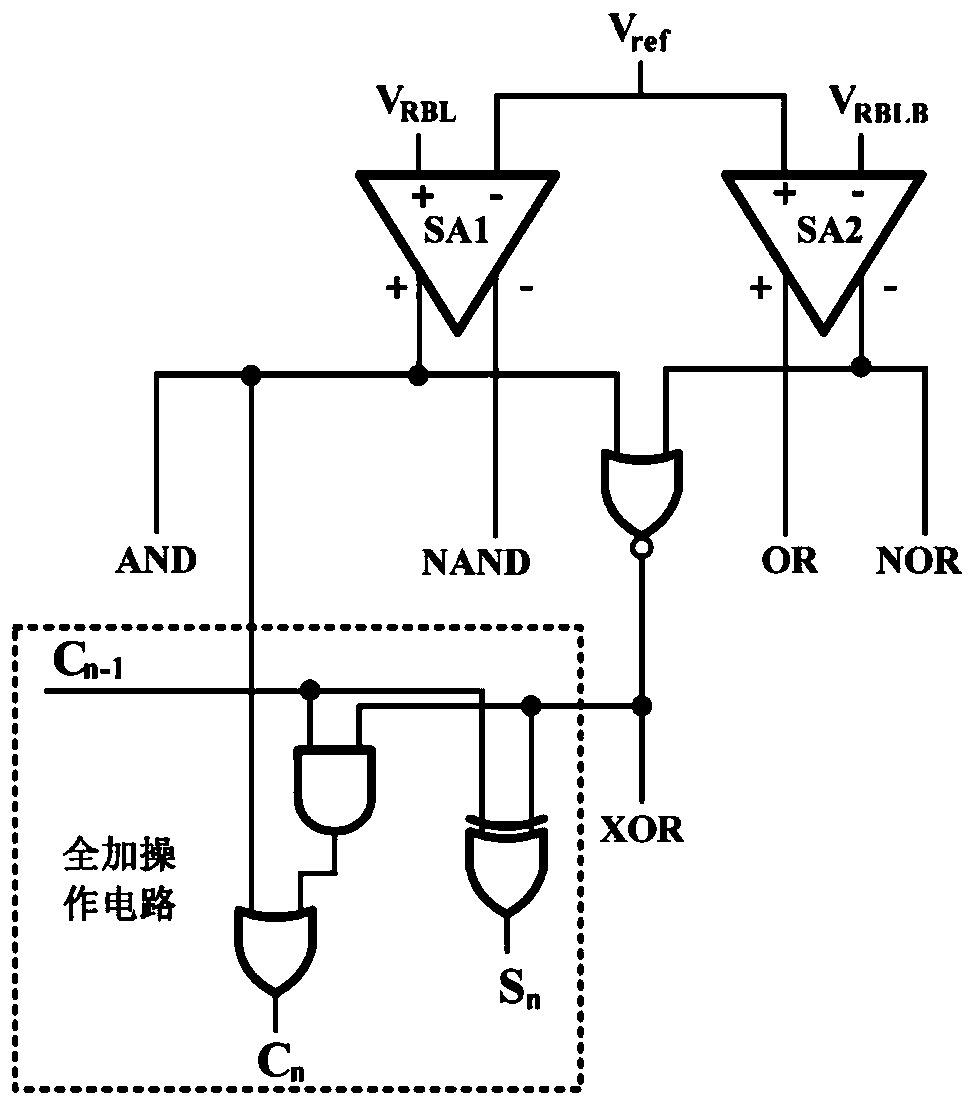

[0040] Such as figure 1 As shown, a storage system supporting calculation in storage includes an SRAM array and m computing modules, the SRAM array includes a row address decoding module and n rows and m columns of SRAM storage units, and the row address decoding module includes Two groups of decoders, each of the calculation modules includes a Boolean logic calculation unit and a full addition calculation unit connected to each other, and each row of SRAM memory cells is connected with the Boolean logic calculation unit by two read bit lines, and the Boolean logic calculation unit and The full-add calculation units are connected, and each of the full-add calculation units is connected in sequence;

[0041] When the SRAM array is performing a read operation, it simultaneously reads the storage data stored by the SRAM cells on the two read word lines, the Boolean logic calculation unit performs Boolean operations on the storage data, and the full addition calculation unit perfo...

Embodiment 2

[0069] Such as Figure 8 As shown, this embodiment provides a computing method supporting in-storage computing, including the steps of writing data and reading data, and the step of reading data specifically includes the following steps:

[0070] S1. Obtain the address information to be read, and simultaneously read the stored data stored in the SRAM cells on the two read word lines according to the address information;

[0071] S2. Perform Boolean operations on the read stored data, and obtain multiple operation results;

[0072] S3. Perform full addition calculation on the stored data according to the operation result.

[0073] The method of this embodiment provides the address Addr of two word lines at a time when reading data i and Addr j , select the SRAM unit that needs to be read out and perform calculation in the storage through the row address decoder, that is, the data of two words is read out and calculated bit by bit at a time. At the same time, the data stored i...

specific Embodiment

[0078] The following combination Figure 1 to Figure 7 The above system and method are explained in detail.

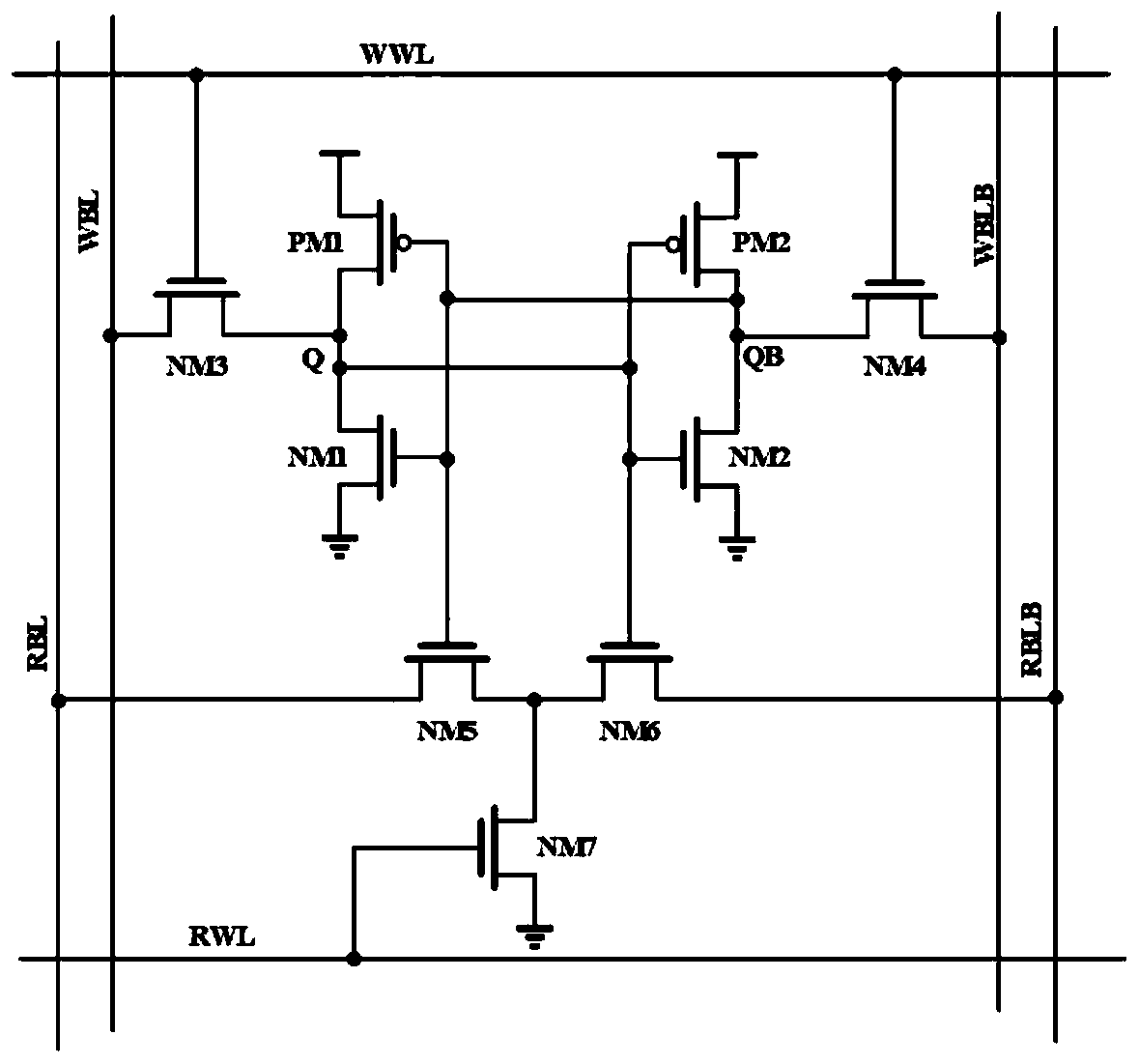

[0079] combine figure 1 As shown, the SRAM computing memory includes n rows and m columns of SRAM storage units, and the main structure is composed of a typical SRAM array structure. The special feature is that two sets of decoders are used at the row address decoder, so that the SRAM array Two word lines can be selected at the same time during the read operation; for figure 2 In the 9T structure SRAM memory cell shown, the word line and the bit line are divided into two groups, that is, the read word line RWL, the write word line WWL, the read bit line RBL and RBLB, and the write bit line WBL and WBLB; A logic circuit is added to realize the in-storage computing function.

[0080] figure 1 The storage unit Cell in figure 2 The 9T structure SRAM storage unit shown in the following combination figure 2 Specifically explain the working principle of the read and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More