A chip self-destruction circuit and a destruction method based on the chip self-destruction circuit

A self-destruction and chip technology, applied in circuits, electrical components, electric solid-state devices, etc., can solve the problems of low destruction efficiency and high hardware cost, and achieve the effect of high destruction efficiency, reduced hardware cost, and reduced resource consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0036] In order to solve the problem of low destruction efficiency and high hardware cost in the prior art in which an external physical destruction circuit or a dedicated physical destruction device is used to destroy a chip, Embodiment 1 of the present application provides a chip self-destruction circuit.

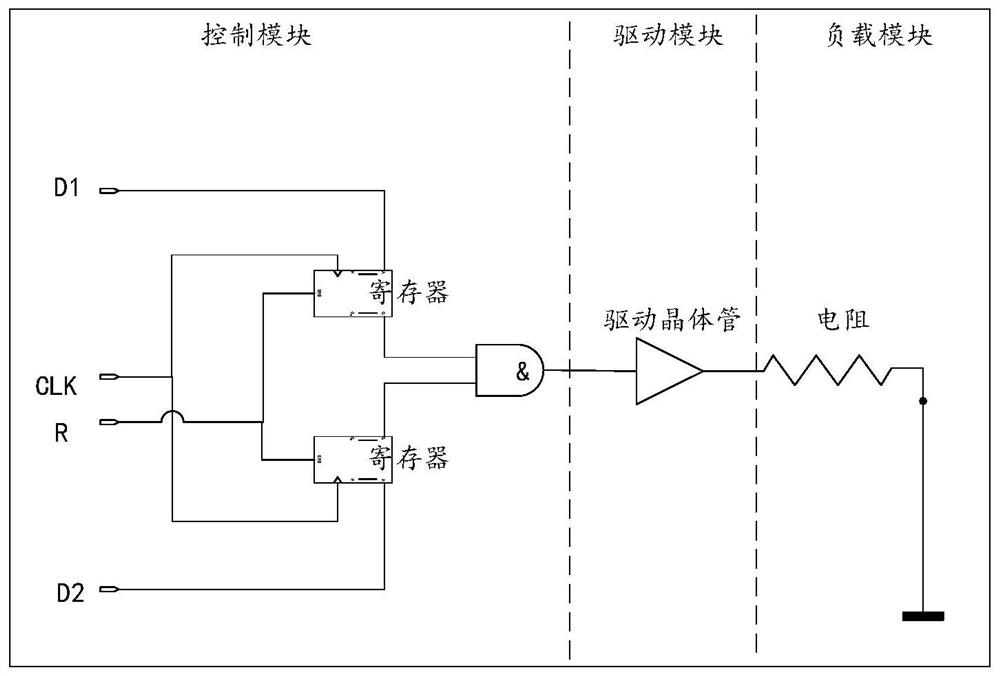

[0037] See the attached figure 1 , figure 1 A schematic structural diagram of a chip self-destruction circuit provided in Embodiment 1 of the present application. The chip self-destruction circuit is applied inside the chip and includes a control module 11, a drive module 12, and a load module 13 connected in sequence. The load module 13 One end is grounded, and the other end is connected to the drive module 12, wherein:

[0038] The control module 11 is used to output a high level, so that the self-destruction circuit of the chip is turned on;

[0039] The drive module 12 is used to burn the chip when the current formed after the chip is turned on from the destruction ...

Embodiment 2

[0058] In order to solve the problem of low destruction efficiency and high hardware cost in the prior art of destroying chips by connecting an external physical destruction circuit or using a special physical destruction device, Embodiment 2 of the present application provides a chip self-destruction circuit-based Destroy method.

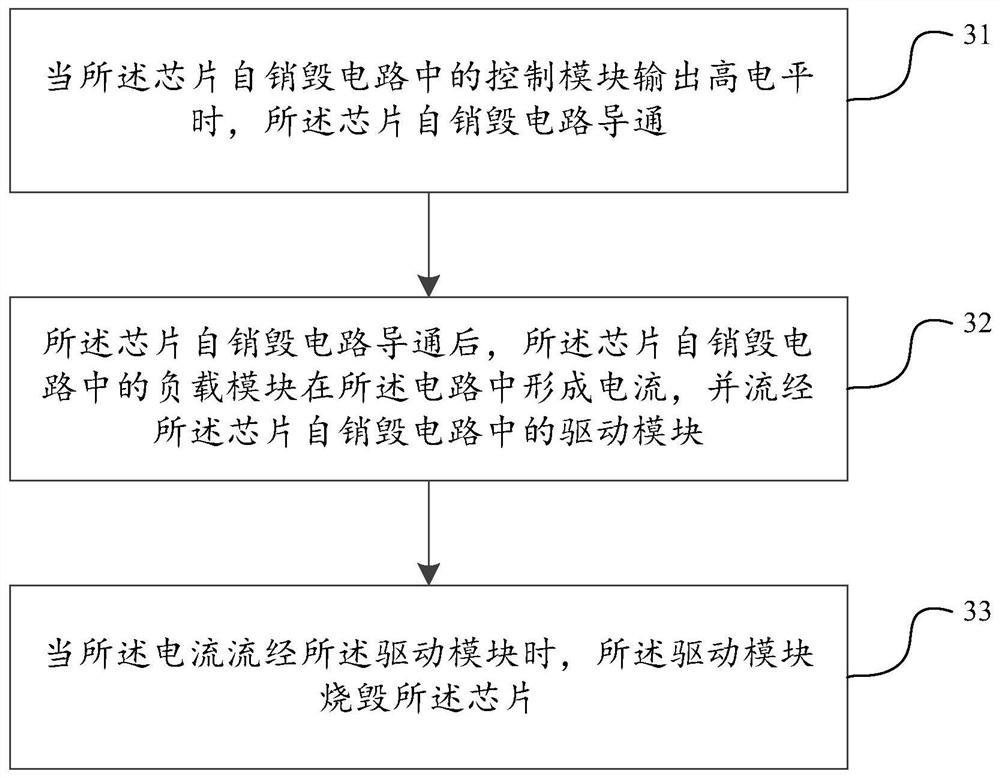

[0059] See attached image 3 , image 3 It is a schematic flow diagram of a destruction method based on a chip self-destruction circuit provided in Embodiment 2 of the present application. The flow specifically includes the following steps:

[0060] Step 31: When the control module in the chip self-destruction circuit outputs a high level, the chip self-destruction circuit is turned on;

[0061] Step 32: After the chip self-destruction circuit is turned on, the load module in the chip self-destruction circuit forms a current in the circuit, and flows through the drive module in the chip self-destruction circuit;

[0062] Step 33: When the curren...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com