Operational amplifier compensation circuit applied to bidirectional open-drain output buffer

A technology of output buffer and compensation circuit, which is applied in the direction of logic circuit coupling/interface and logic circuit connection/interface arrangement using field effect transistors, which can solve the problem of increasing the output voltage switching range, increasing the loop stabilization time, reducing Issues such as transmission signal rate to reduce the possibility of overshoot and oscillation, improve stability and accuracy, and shorten response time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] The specific implementation of the present invention will be described in further detail below in conjunction with the accompanying drawings of the embodiments, so as to make the technical solution of the present invention easier to understand and grasp, so as to define the protection scope of the present invention more clearly.

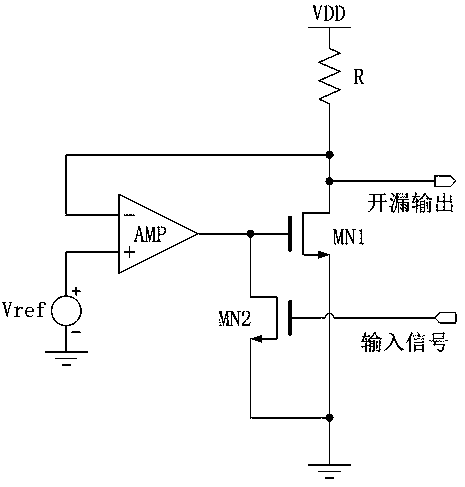

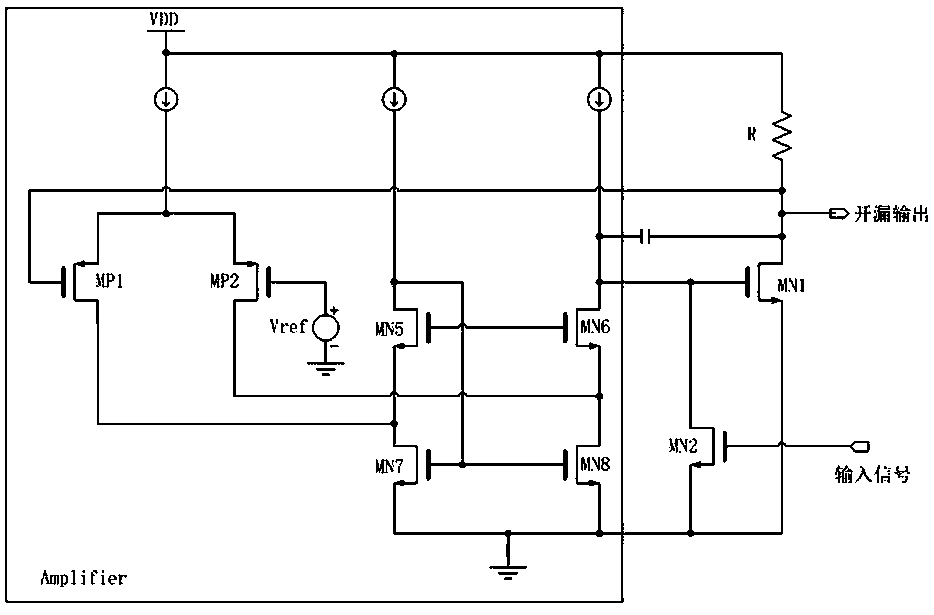

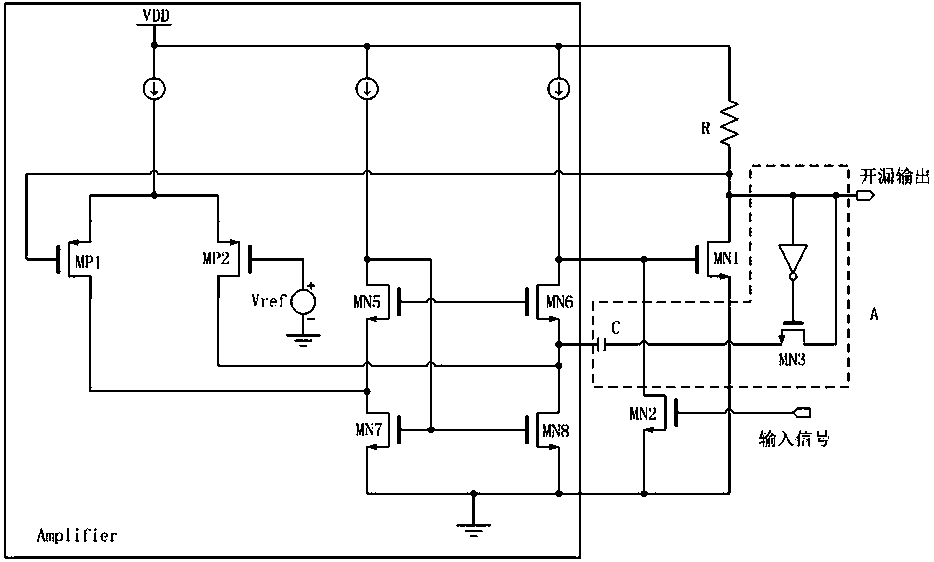

[0013] The designer of the present invention aims at the design of the loop compensation in the bidirectional open-drain output buffer in the prior art. There are problems such as increasing the loop stabilization time, reducing the transmission signal rate and increasing the output voltage signal switching range, and the open-drain output performance cannot meet all requirements. A comprehensive analysis of the circuit structure was carried out for the many deficiencies needed. Combining its own experience and creative work, it is committed to seeking a breakthrough in the all-round optimization of the circuit performance, and innovatively prop...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More