A sample and hold circuit

A technology of sample and hold circuit and resistance, applied in electrical components, electrical signal transmission systems, instruments, etc., can solve the problem of inability to apply low power supply voltage, achieve high bandwidth, and minimize tracking errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The technical solution of the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

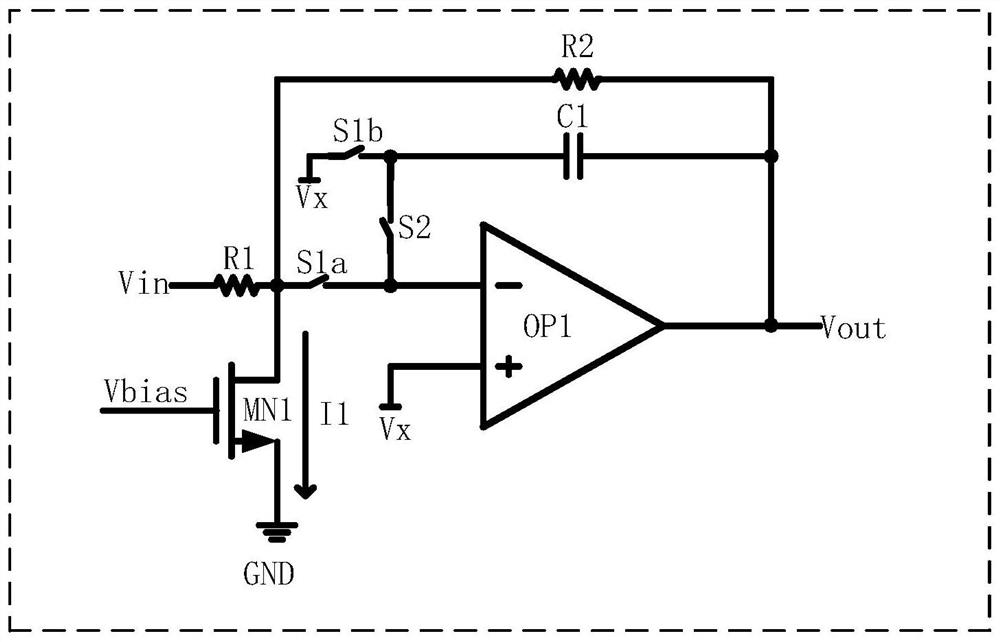

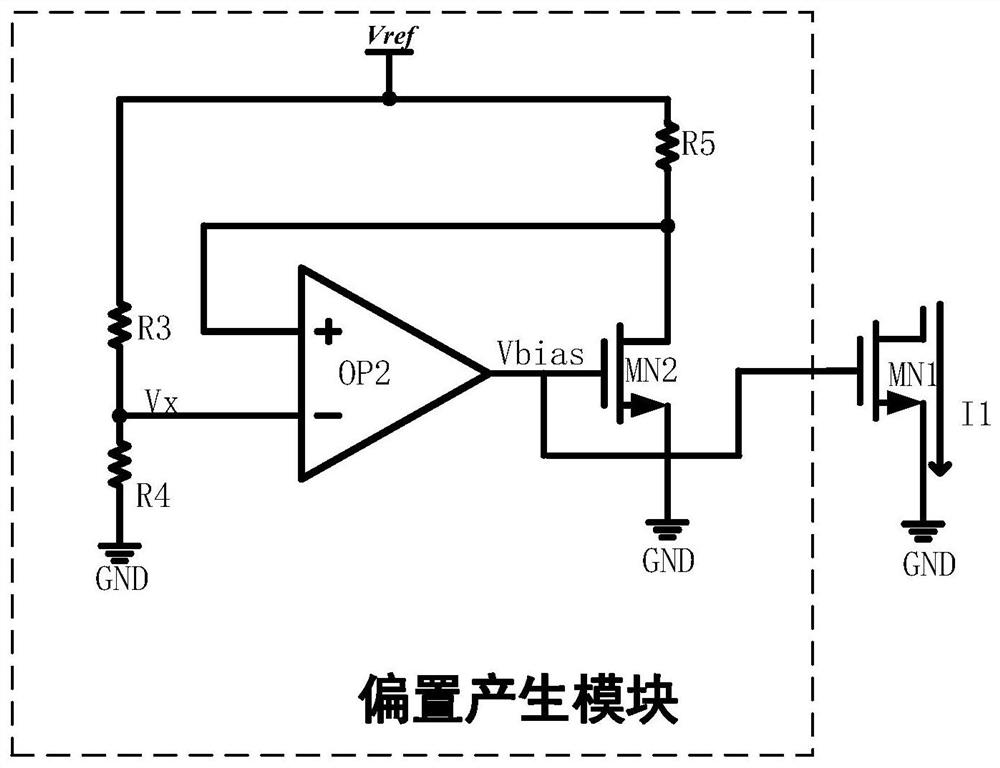

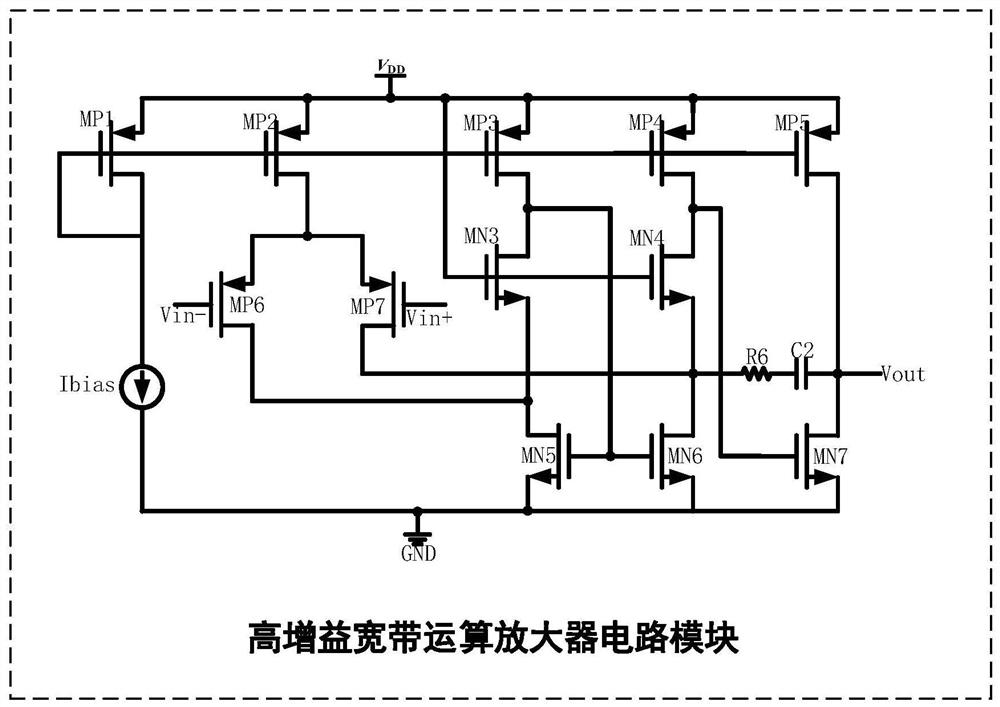

[0028] Such as figure 1 Shown is a sample-and-hold circuit proposed by the present invention, including a first operational amplifier OP1, a first switch S1a, a second switch S1b, a third switch S2, a first resistor R1, a second resistor R2, a first NMOS transistor MN1 and the first capacitor C1, one end of the first resistor R1 is used as the input end of the sample-and-hold circuit, and the other end is connected to the drain of the first NMOS transistor MN1, one end of the first switch S1a, and connected to the first operational amplifier after passing through the second resistor R2 The output end of OP1; the negative input end of the first operational amplifier OP1 is connected to the other end of the first switch S1a and one end of the third switch S2, and its positive input end is connected to one end of the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More