GaN-based PIN diode device structure and preparation method thereof

A PIN diode and device structure technology, which is applied in the field of new PIN diode device structure, can solve the problems of crystal quality degradation, leakage current increase, N-doping overweight, etc., achieve uniform current expansion, ease current congestion, and simple and reliable process Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

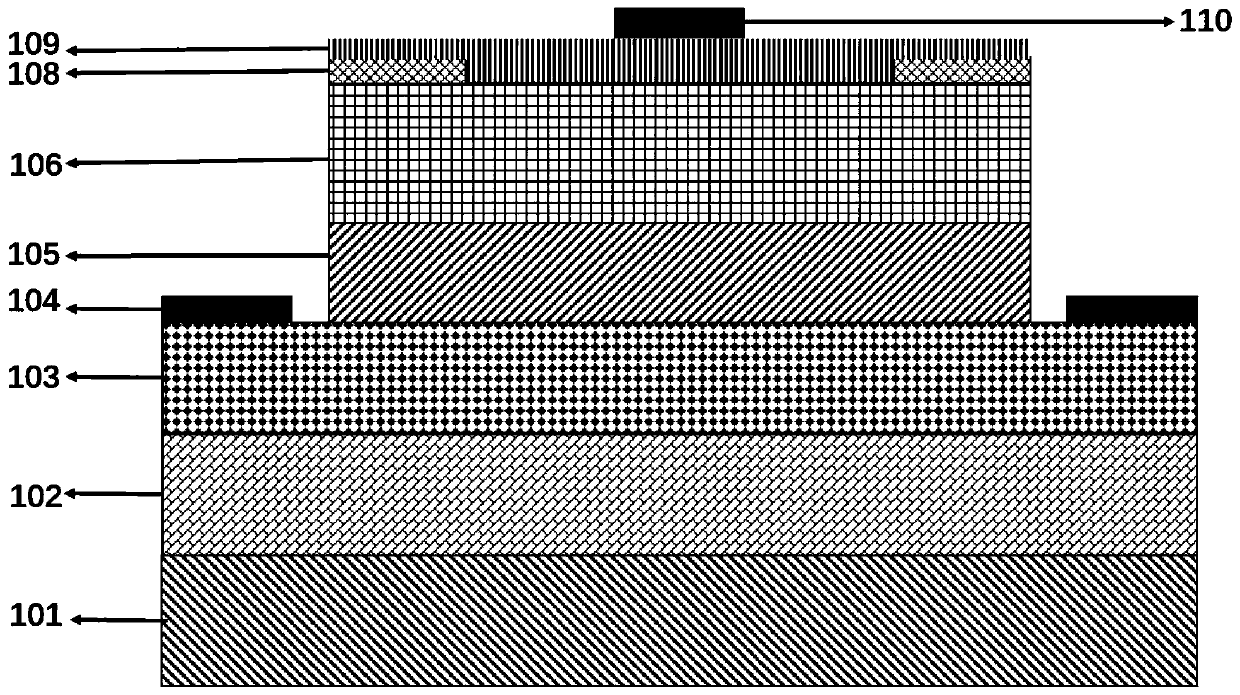

[0067] This embodiment has a PIN diode device structure (the device in this embodiment is cylindrical), and the diode device structure includes in sequence along the epitaxial growth direction: a substrate 101, a buffer layer 102, and an N-type heavily doped semiconductor transport layer 103;

[0068] An N-type intrinsic layer 105 is distributed on the N-type heavily doped semiconductor transport layer 103, the two centers are the same, and the projected area of the N-type intrinsic layer 105 is N-type heavily doped semiconductor transport layer 103 50% of;

[0069] A P-type heavily doped semiconductor transport layer 106 is grown on the N-type intrinsic layer 105, and the top outer ring portion of the P-type heavily doped semiconductor transport layer 106 is an N-type insertion layer 107. The projected area of the N-type insertion layer 107 is 50% of the area of the P-type heavily doped semiconductor transport layer 106;

[0070] The N-type insertion layer 107 is obta...

Embodiment 2

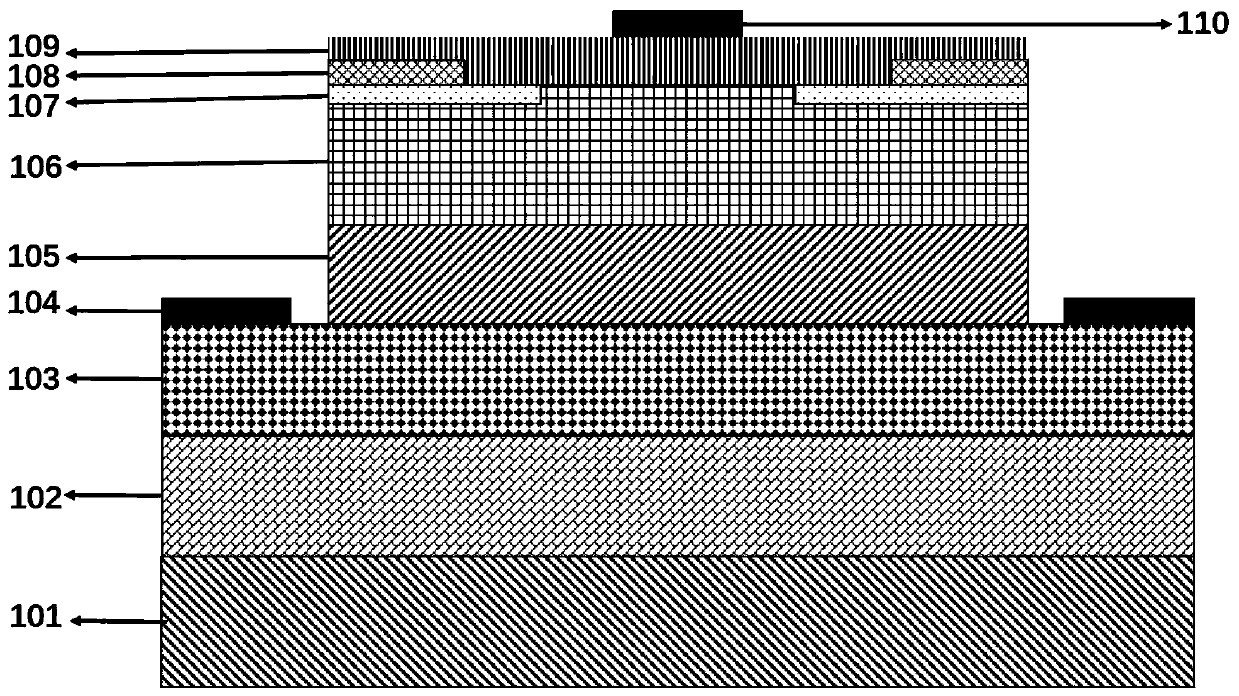

[0089] This embodiment has a vertical PIN diode device structure, which sequentially includes along the epitaxial growth direction: an N-type heavily doped semiconductor transport layer 103; the N-type heavily doped semiconductor transport layer 103 is distributed There is an N-type intrinsic layer 105; a P-type heavily doped semiconductor transport layer 106 is grown on the N-type intrinsic layer 105, and the ring-shaped portion at the top of the P-type heavily doped semiconductor transport layer 106 is N-type insertion layer 107; the N-type insertion layer 107 is obtained by implanting N-type ions into the material of the P-type heavily doped semiconductor transport layer 106, the N-type ions are silicon ions, and the implanted Quantity is 10 18 cm -3 . A ring-shaped insulating layer 108 is grown on the outer edge of the N-type insertion layer 107; the current spreading layer 109 is formed on the insulating layer 108 and the exposed P-type heavily doped semiconductor trans...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More