Formation method of enhanced field effect transistor

A field-effect transistor, enhancement-mode technology, applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve problems such as limiting applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

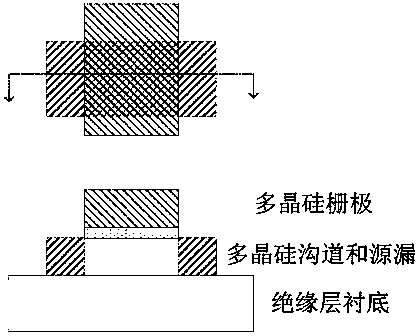

[0015] figure 2 Example 2 of polysilicon channel SOI MOSFET, forming a double-gate device

[0016] figure 2 An example of forming a double-gate polysilicon channel SOI MOSFET is given, which is compatible with figure 1 The difference of the illustrated embodiment is that an N-type doped region is formed on the substrate as the second gate of the device, and other processes are the same as in the first embodiment. The N-type doped region of the substrate can be formed using an existing process.

[0017] Different from the device channel in the existing bulk silicon CMOS process and SOI CMOS process which is monocrystalline silicon, polysilicon channel is used in the present invention, so that the substrate of the device channel can be realized as insulating layer material instead of semiconductor silicon Material.

[0018] 4. Technical effects

[0019] This scheme implements a polysilicon channel SOI MOSFET under the bulk silicon process, and its advantages are that it h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More