Patents

Literature

36 results about "Double polysilicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

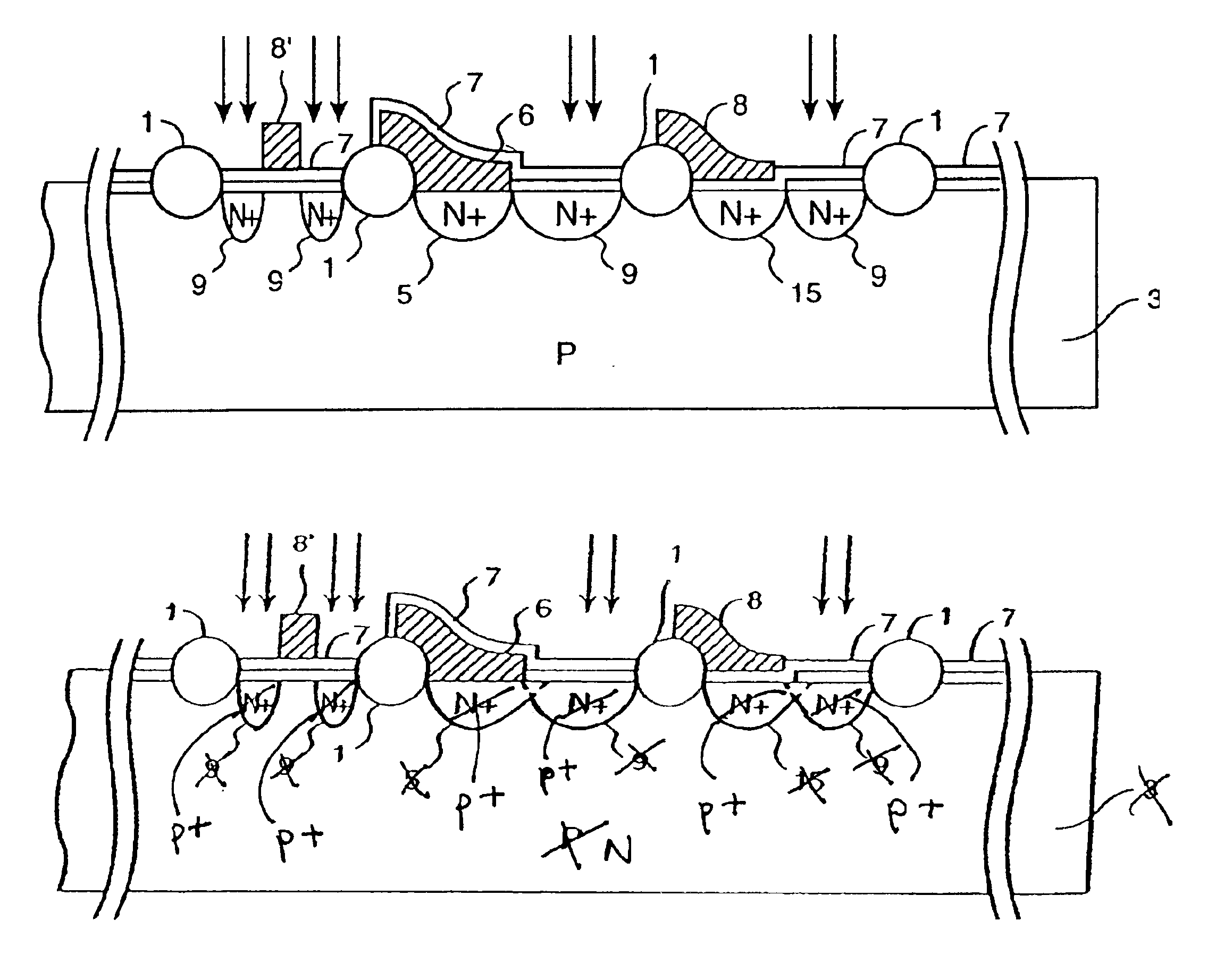

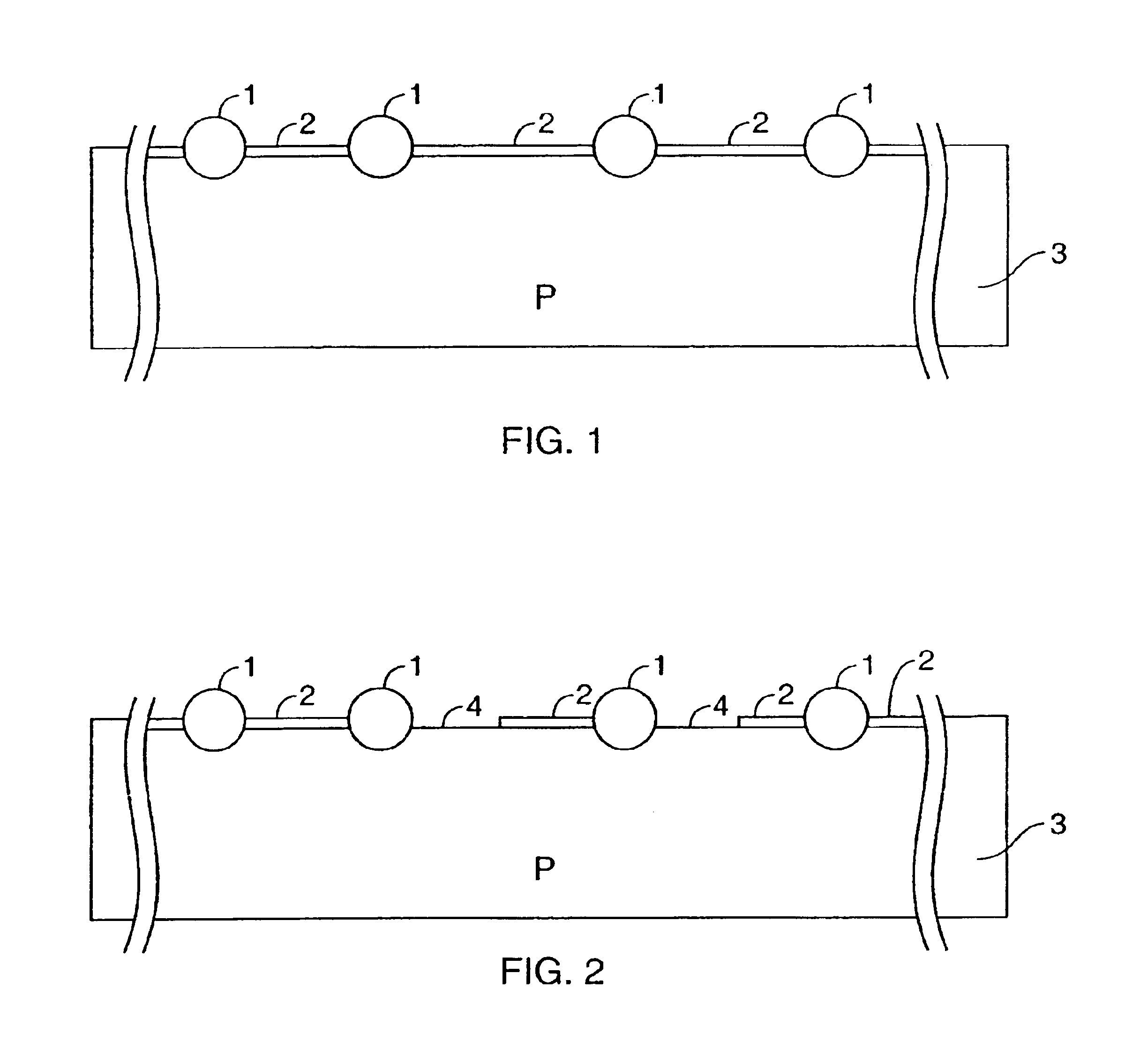

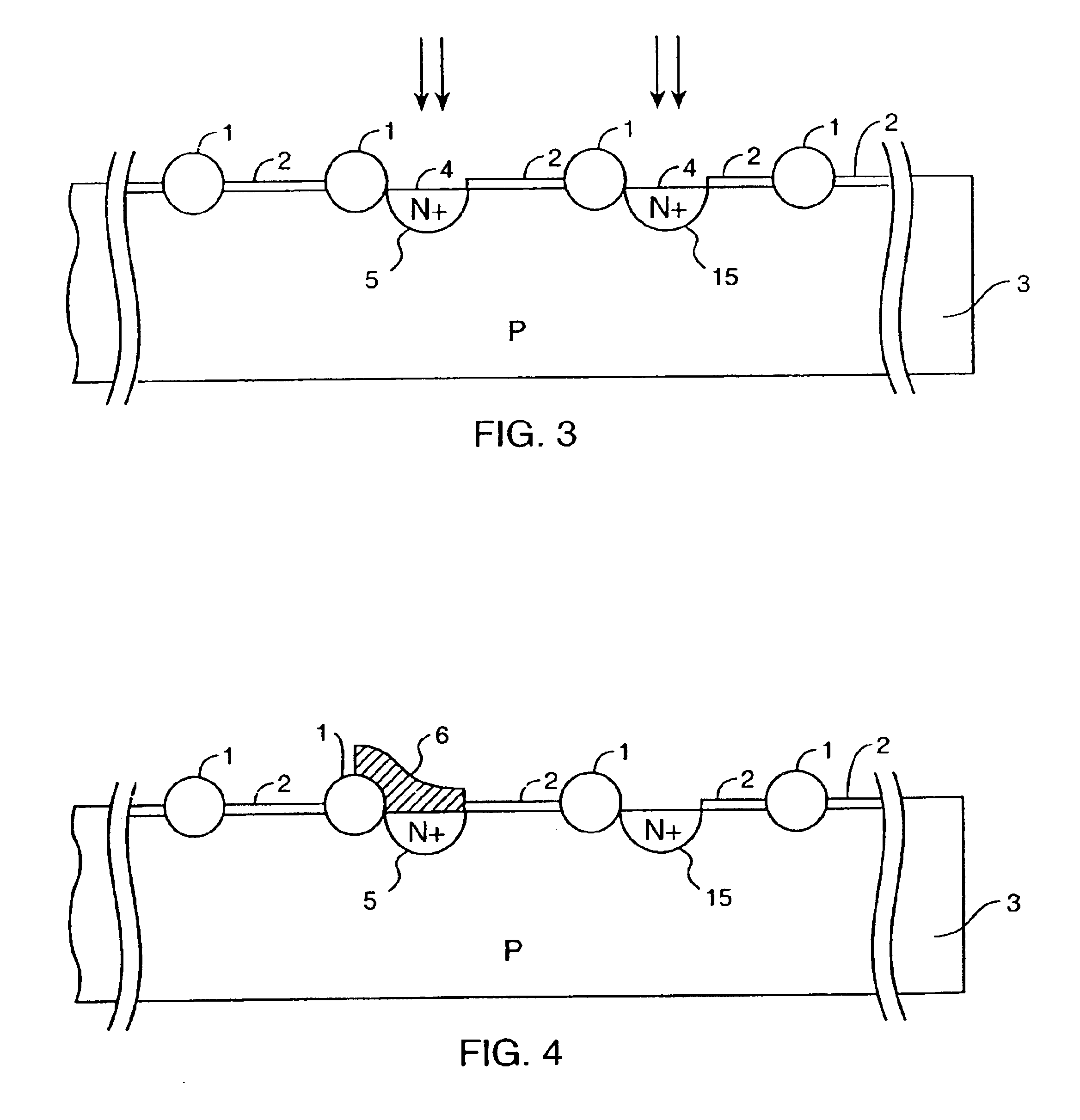

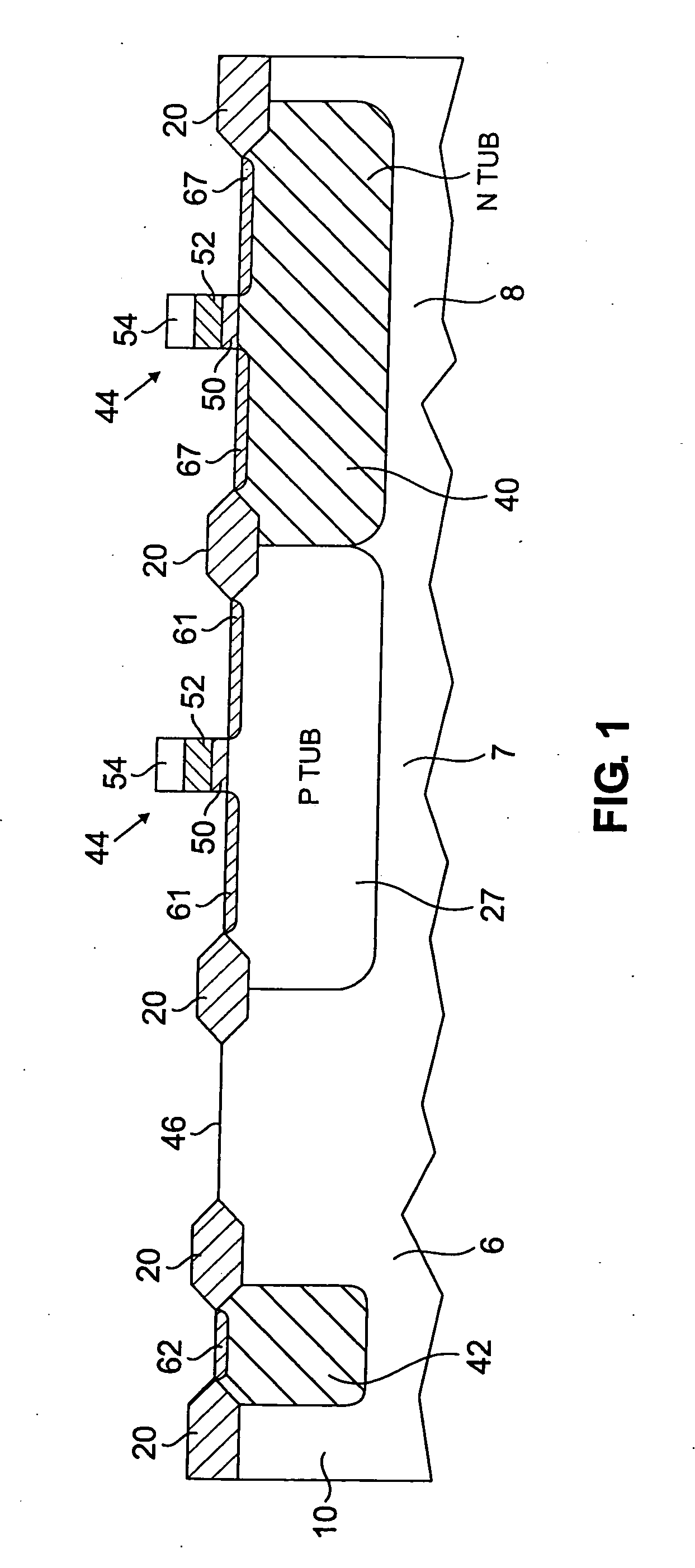

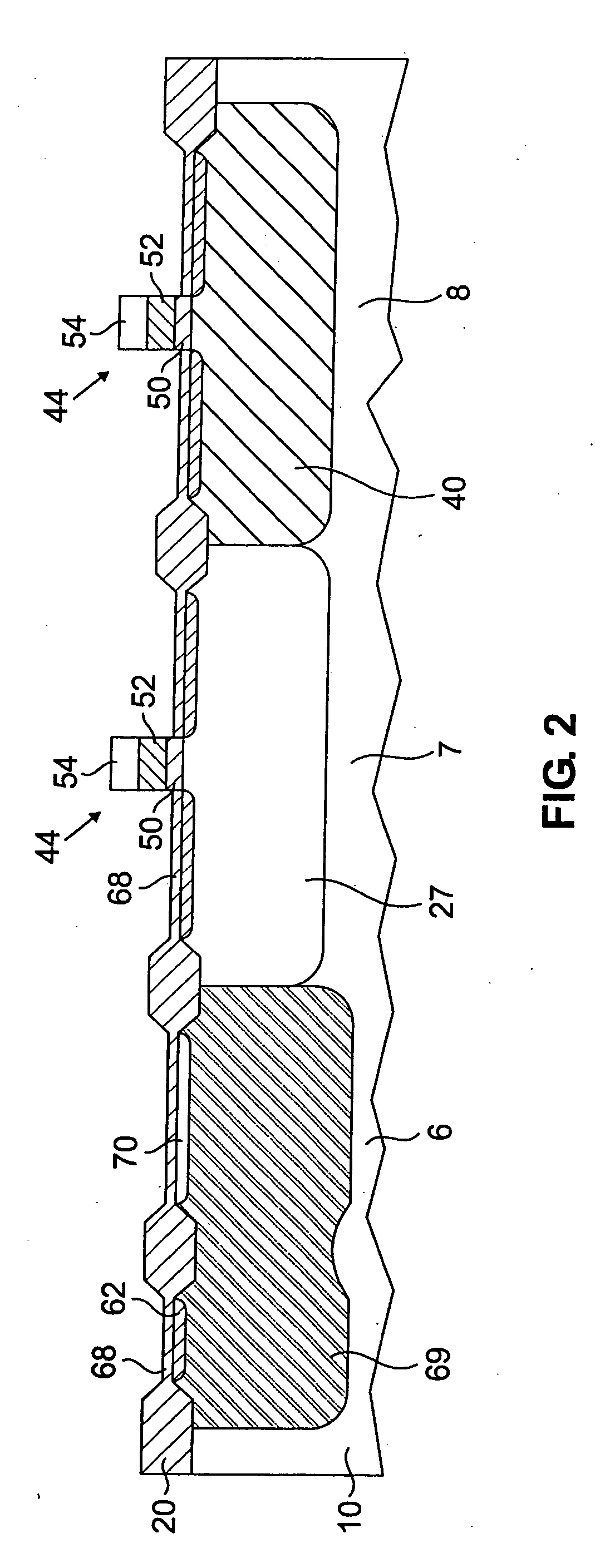

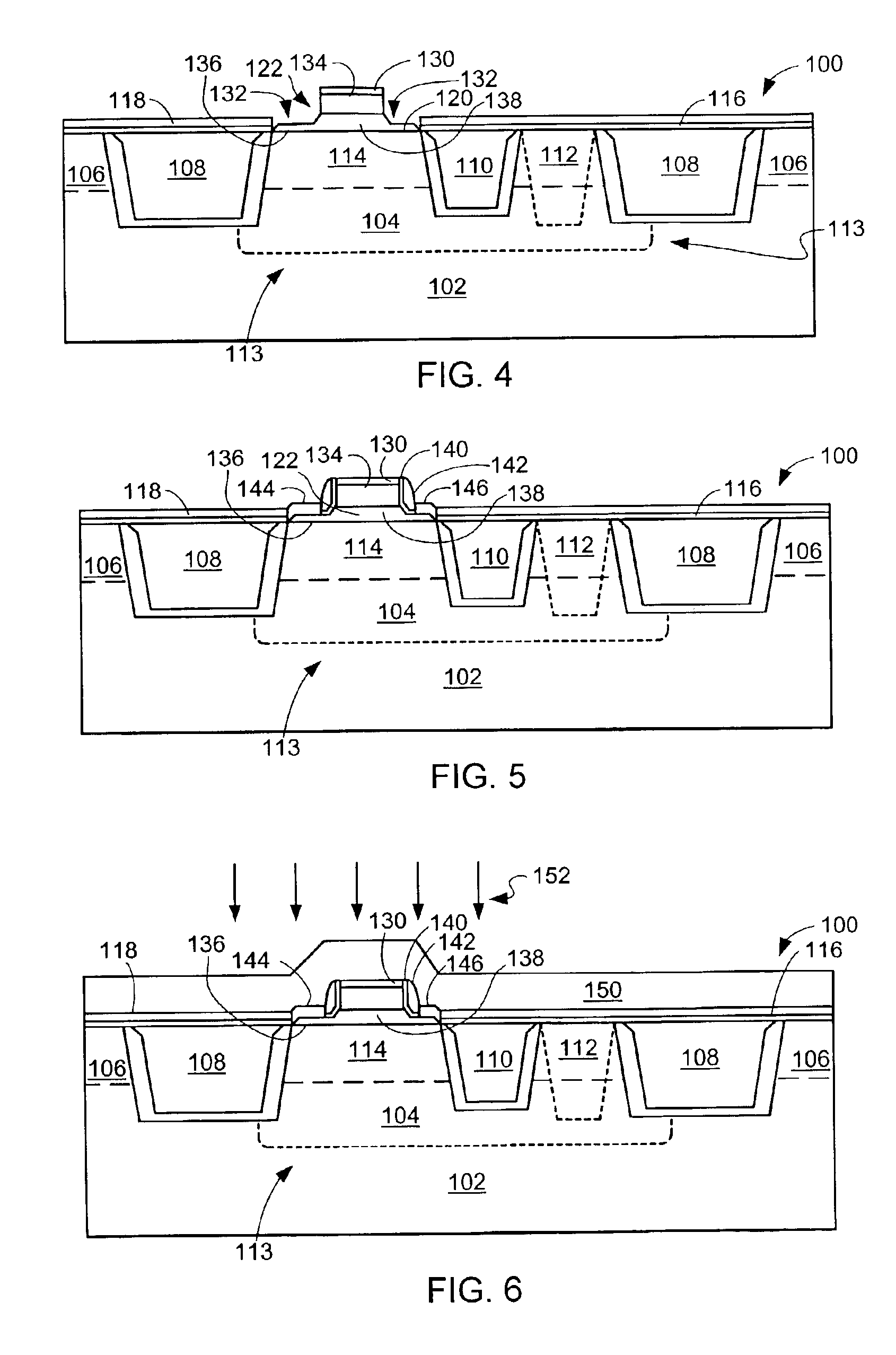

Permanently on transistor implemented using a double polysilicon layer CMOS process with buried contact

InactiveUS6919600B2Protective processingTransistorSemiconductor/solid-state device detailsDouble polysiliconPolysilicon gate

A permanently-ON MOS transistor comprises silicon source and drain regions of a first conductivity type in a silicon well region of a second conductivity type. A silicon contact region of the first conductivity types is buried in the well region, said contact region contacting said source region and said drain region. A first gate insulating layer is selectively placed over the silicon source and drain regions. A second gate insulating layer is selectively placed over the first gate insulating layer and over the silicon contact region. A polysilicon gate region is placed over the second gate insulating layer.

Owner:HRL LAB

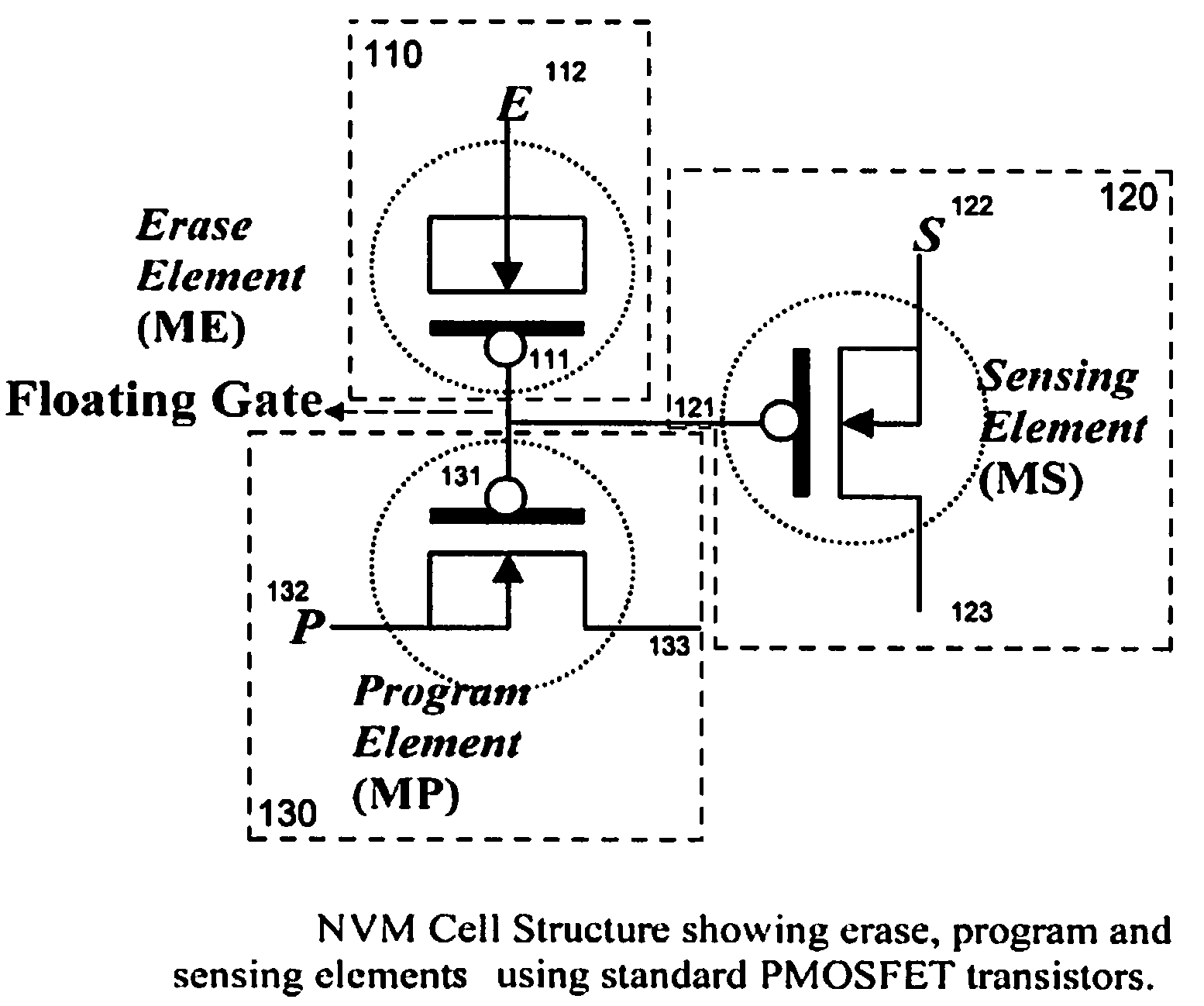

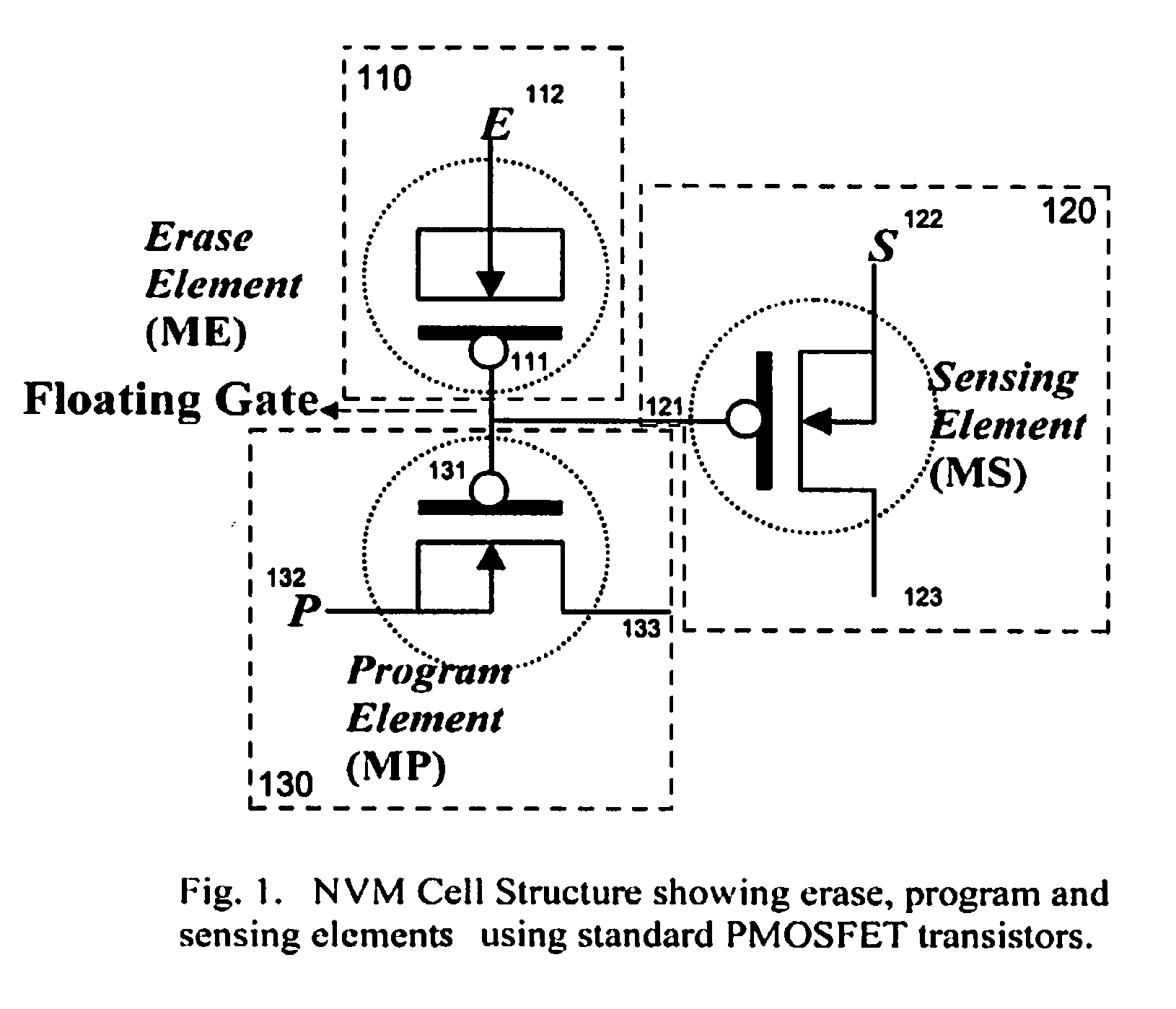

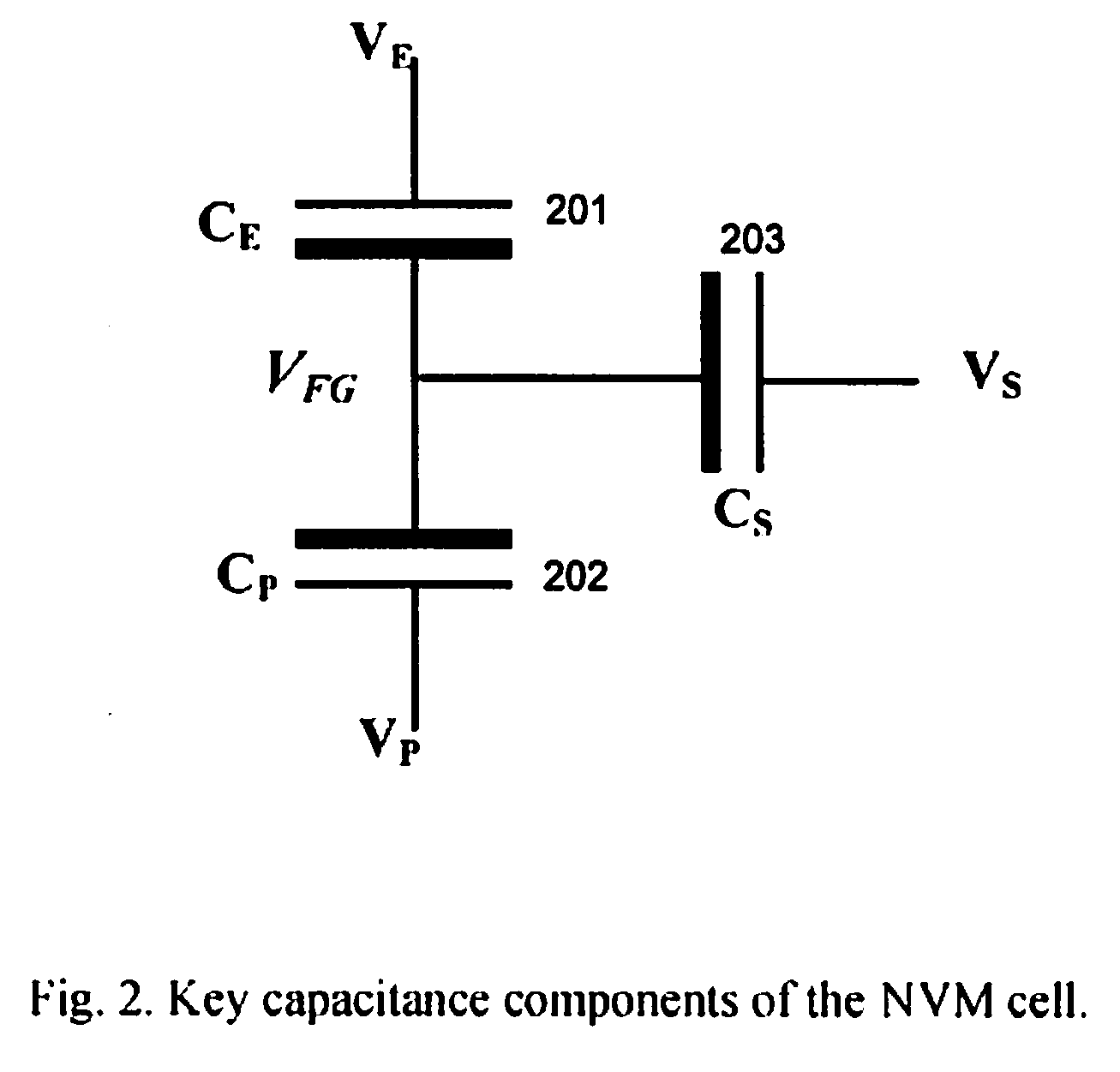

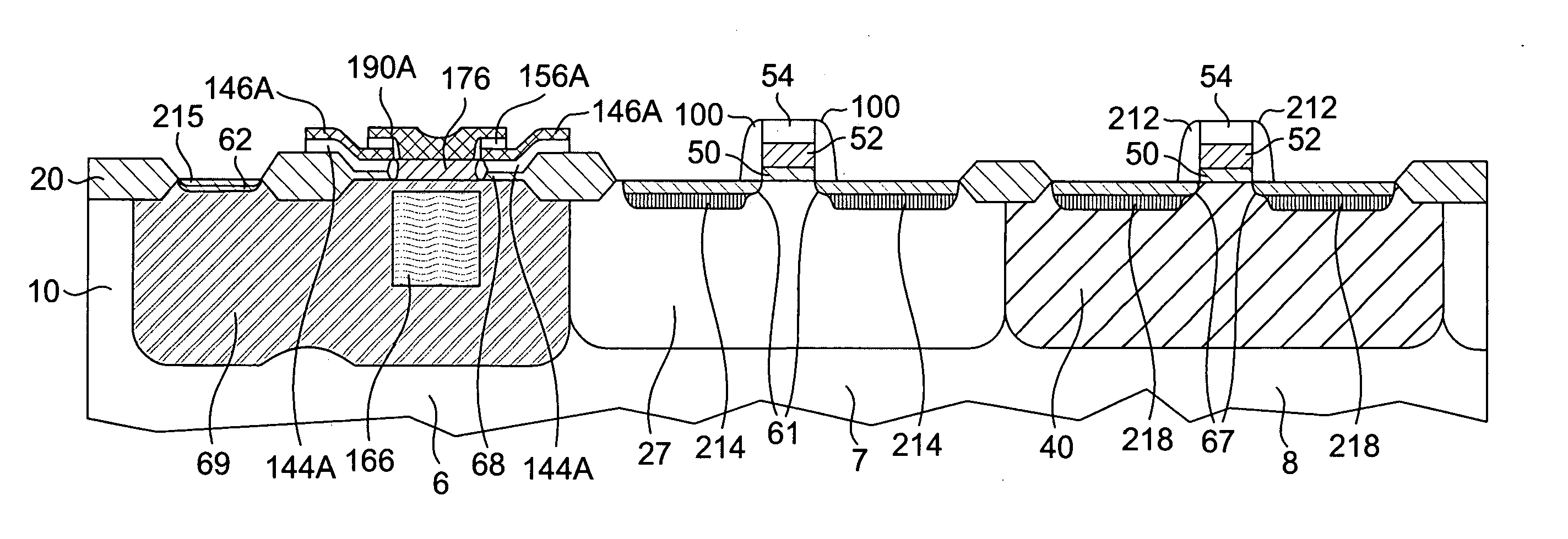

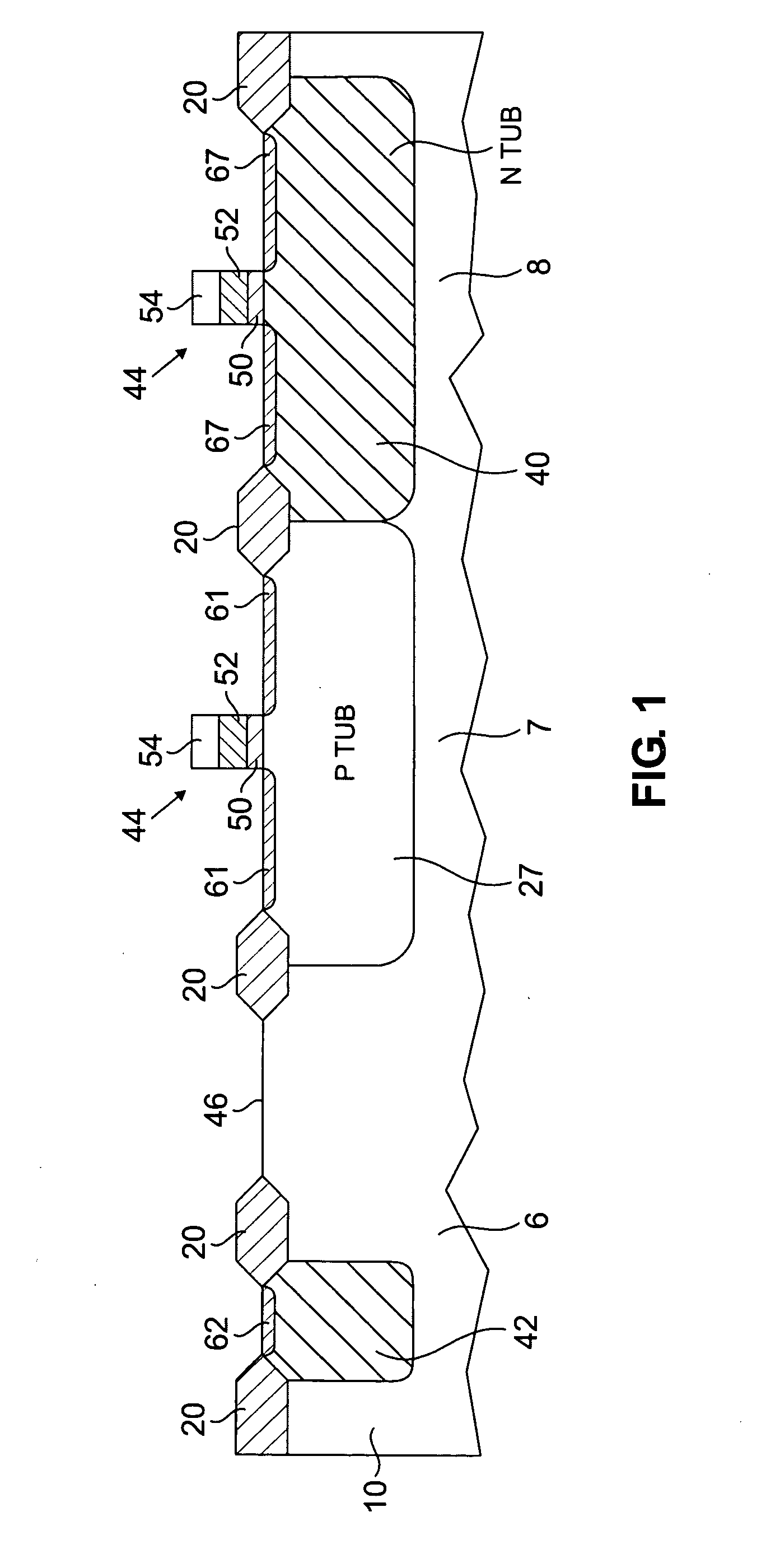

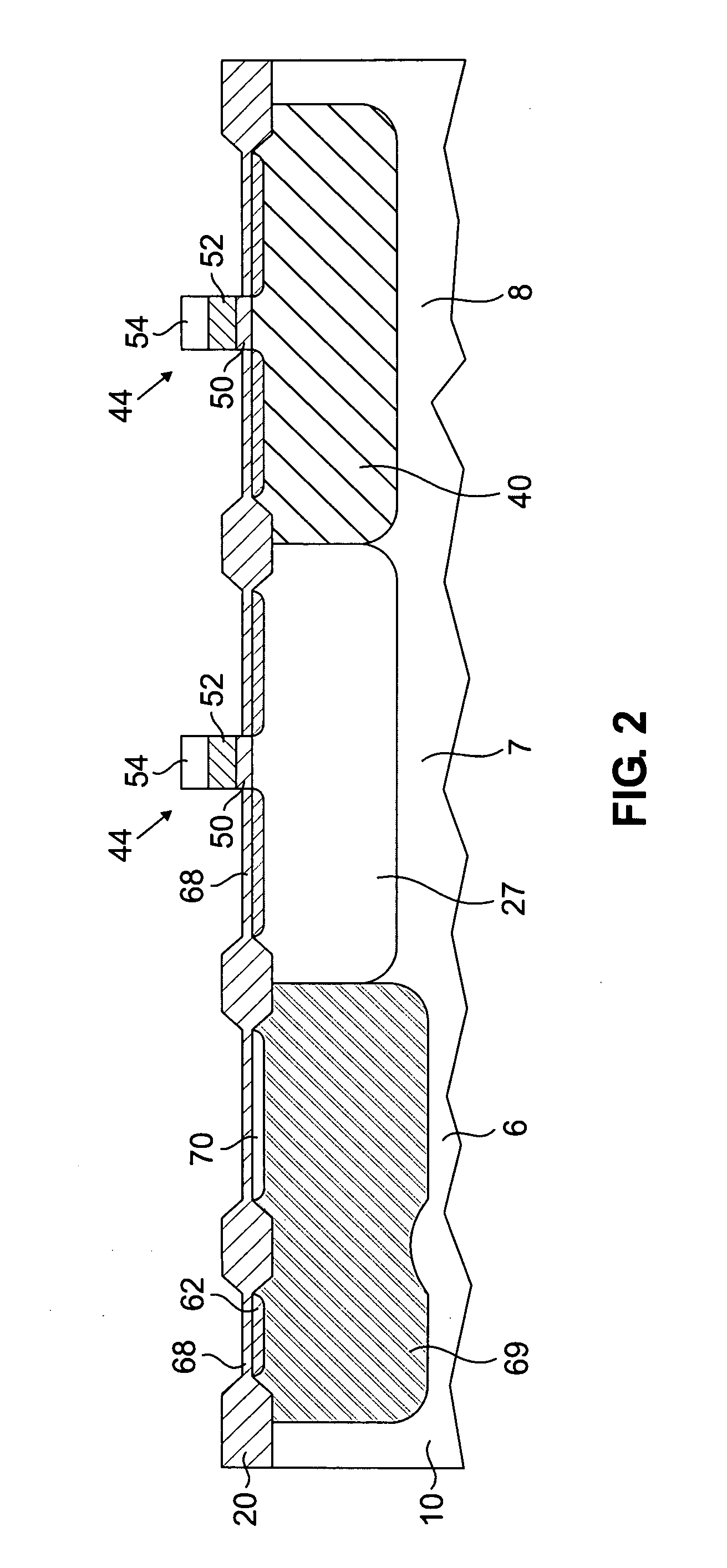

CMOS Compatible Single-Poly Non-Volatile Memory

InactiveUS20080310237A1Little and no extra cost addedImpact transistor performanceSolid-state devicesRead-only memoriesLow voltageComputer terminal

The present invention teaches a single-poly non-volatile memory cell which is compatible with the CMOS process, uses lower voltages for operating, and is more reliable in program, read, or erase operation. The single-poly non-volatile memory cell in accordance with the present invention comprises a program transistor with a program terminal; a sensing transistor with a sensing terminal; and an erase transistor with an erase terminal, wherein the sensing transistor shares a floating gate with the program transistor and the erase transistor. By employing the present invention, significant cost advantages in feature-rich semiconductor products, such as System-on-Chip (SoC) design, compared to conventional dual-poly floating gate embedded Flash memory are provided.

Owner:CYPRESS SEMICON CORP

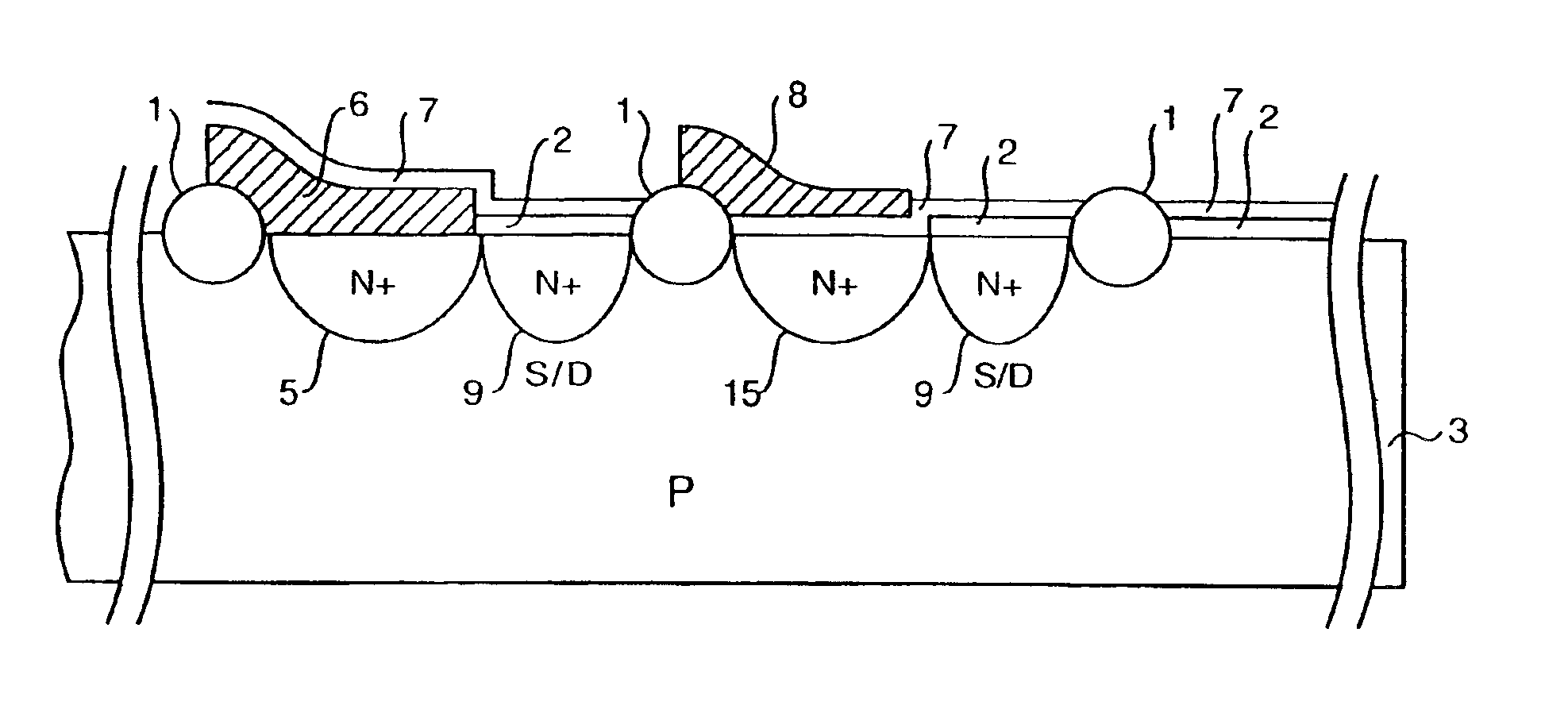

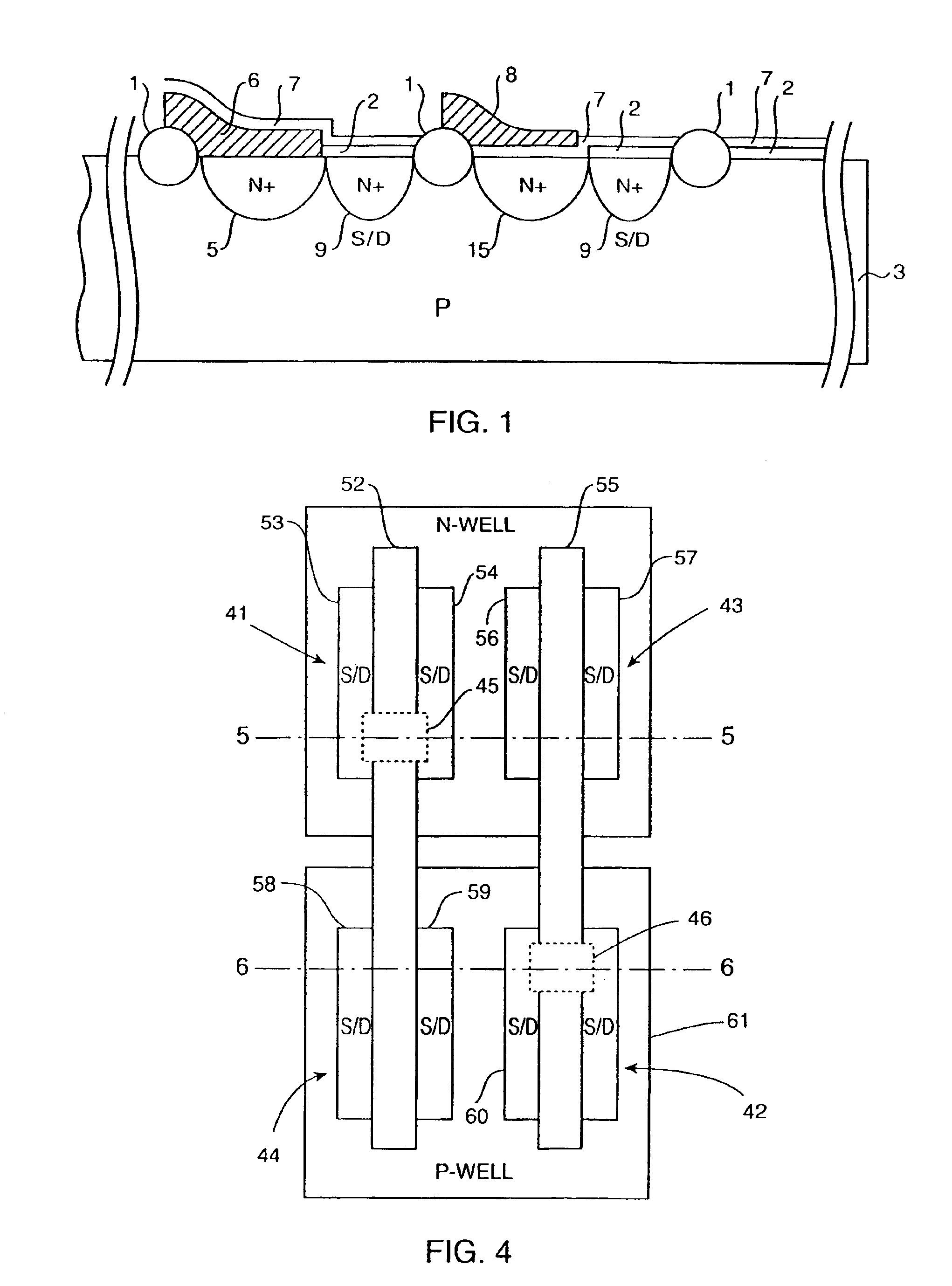

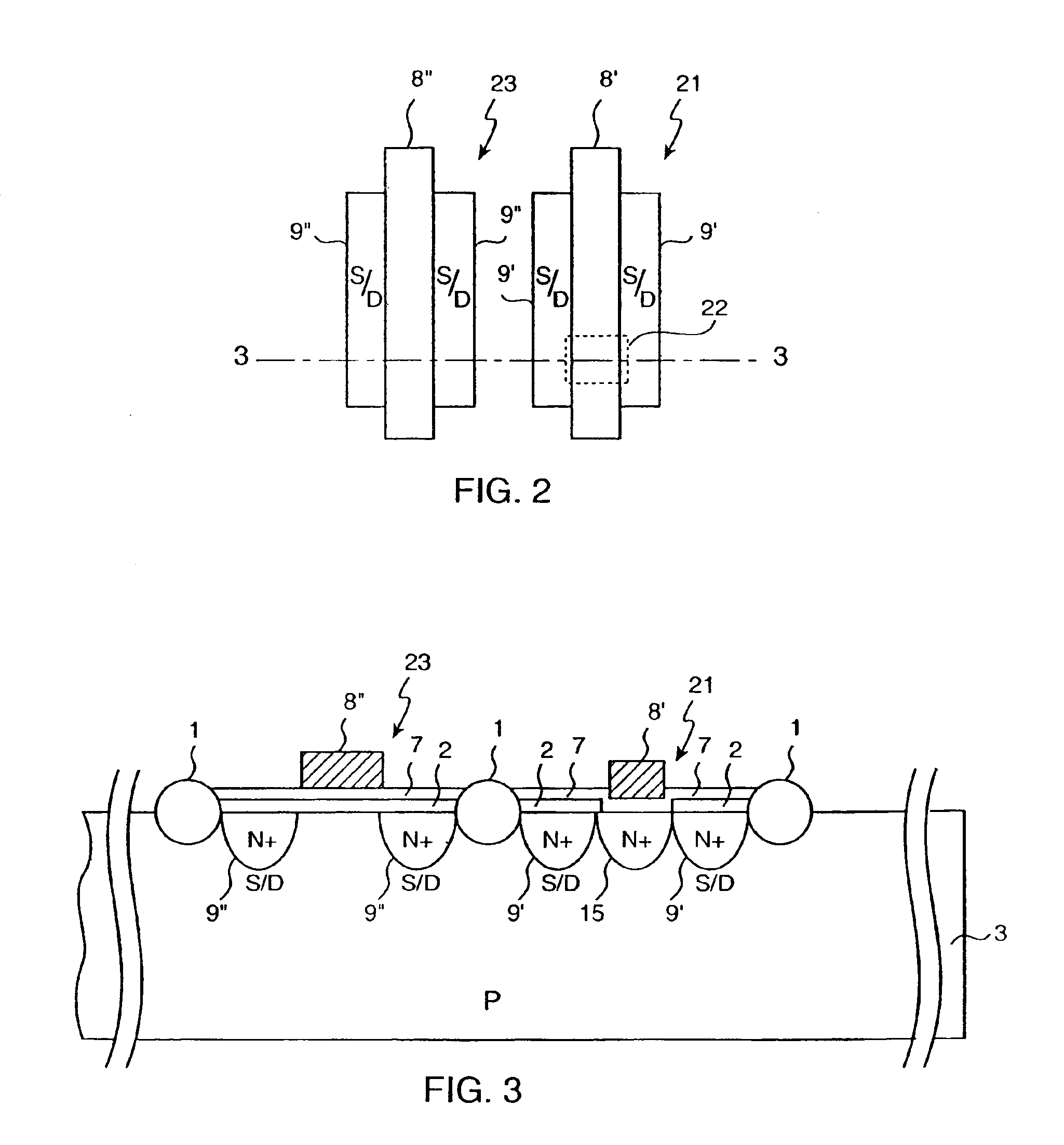

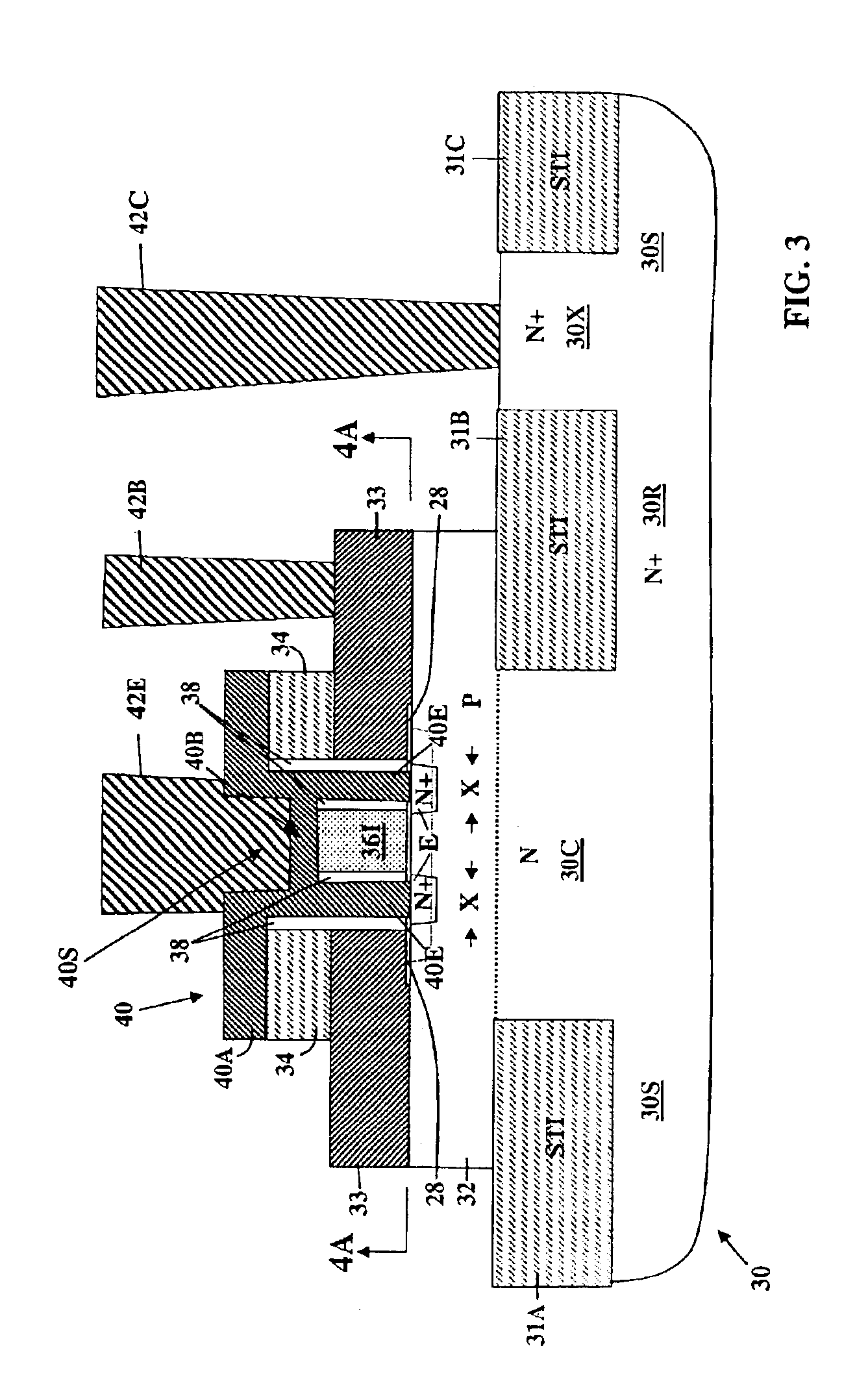

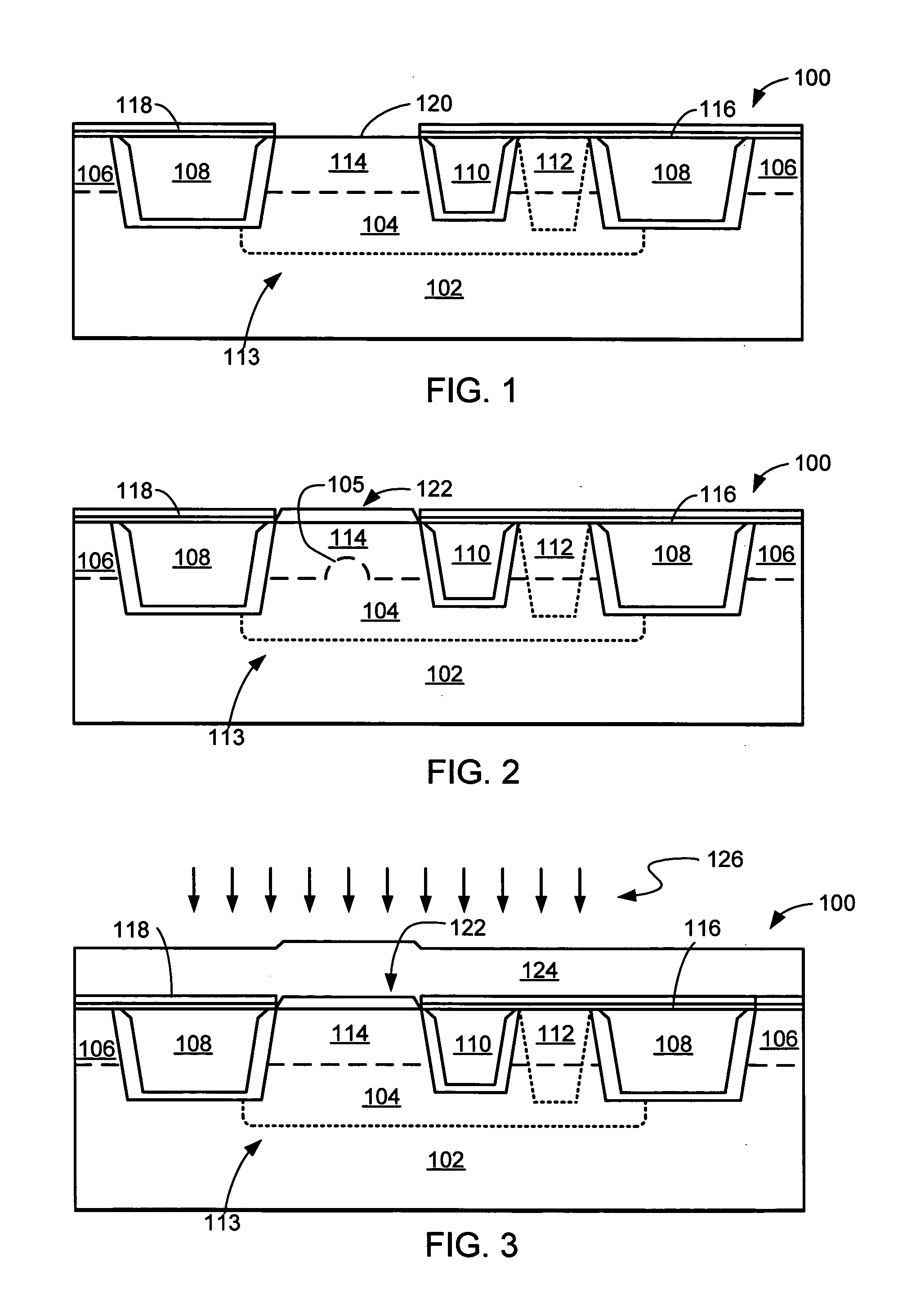

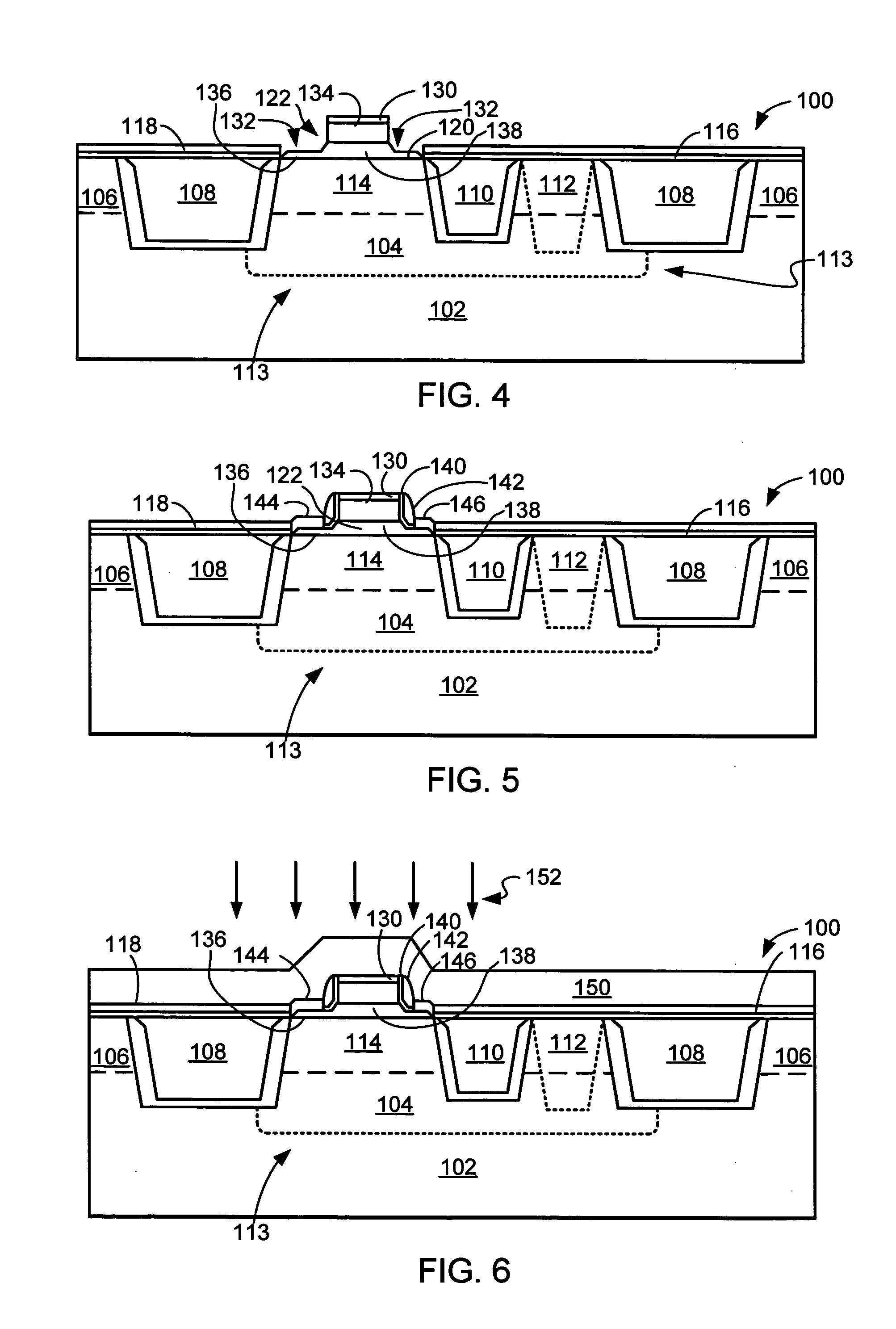

Programmable connector/isolator and double polysilicon layer CMOS process with buried contact using the same

InactiveUS6893916B2Preventing reverse engineeringSemiconductor/solid-state device detailsSolid-state devicesRegioselectivityDouble polysilicon

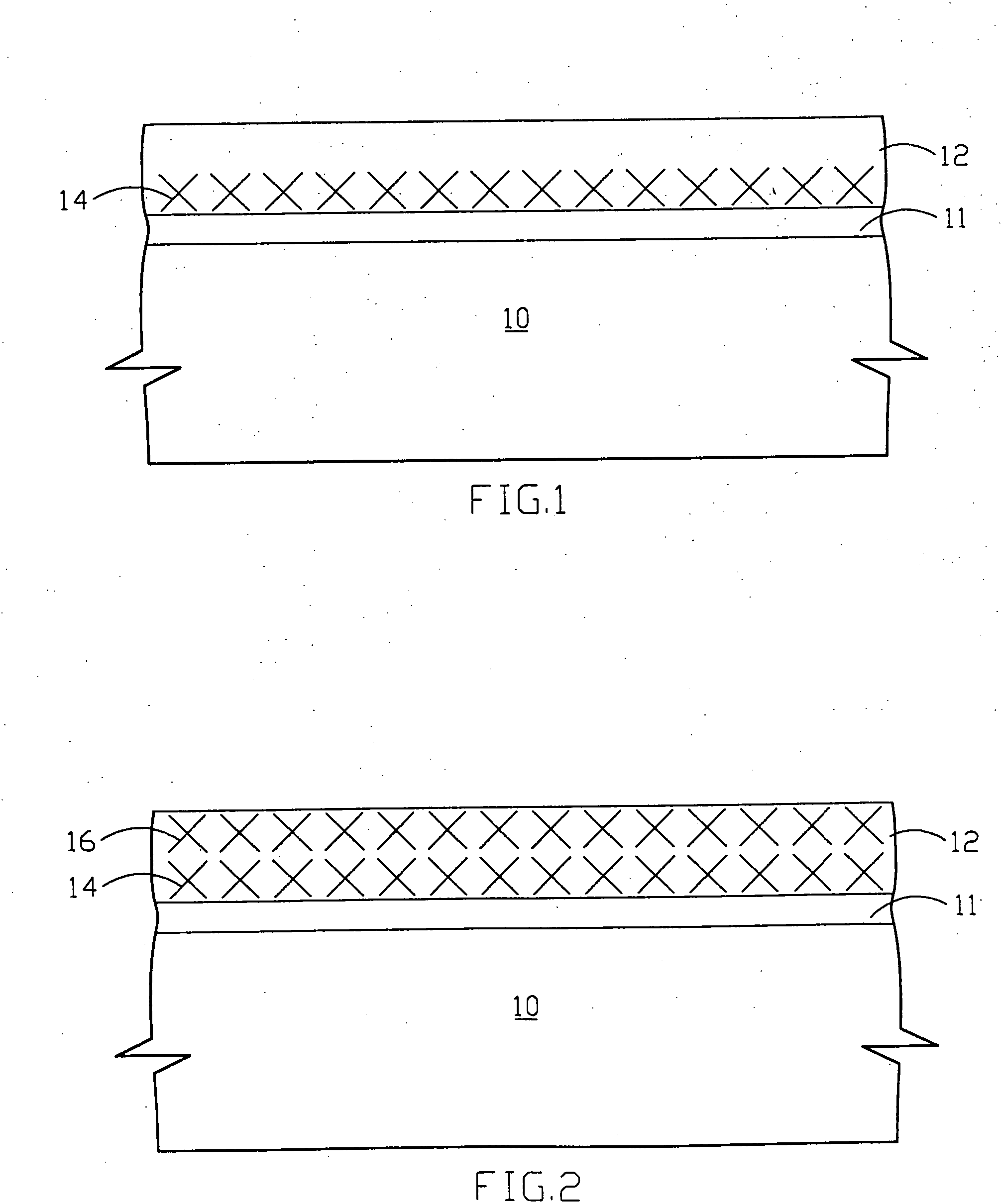

An integrated circuit structure for MOS-type devices including a silicon substrate of a first conductivity type; a first gate insulating regions selectively placed over the silicon substrate of the first conductivity tape; a first polycrystalline silicon layer selectively placed over the silicon substrate of the first conductivity type; a second gate insulating regions selectively placed over the first gate insulating regions and the first polycrystalline silicon layer; a second polycrystalline silicon layer selectively placed over the second gate insulating regions; first buried silicon regions of a second conductivity type, buried within the silicon substrate of the first conductivity type, placed under the first polycrystalline silicon layer and in contact therewith; and second buried silicon regions of the second conductivity type, buried within the silicon substrate of the first conductivity type, placed under the second gate insulating regions, under the second polycrystalline silicon layer and insulated therefrom.

Owner:HRL LAB

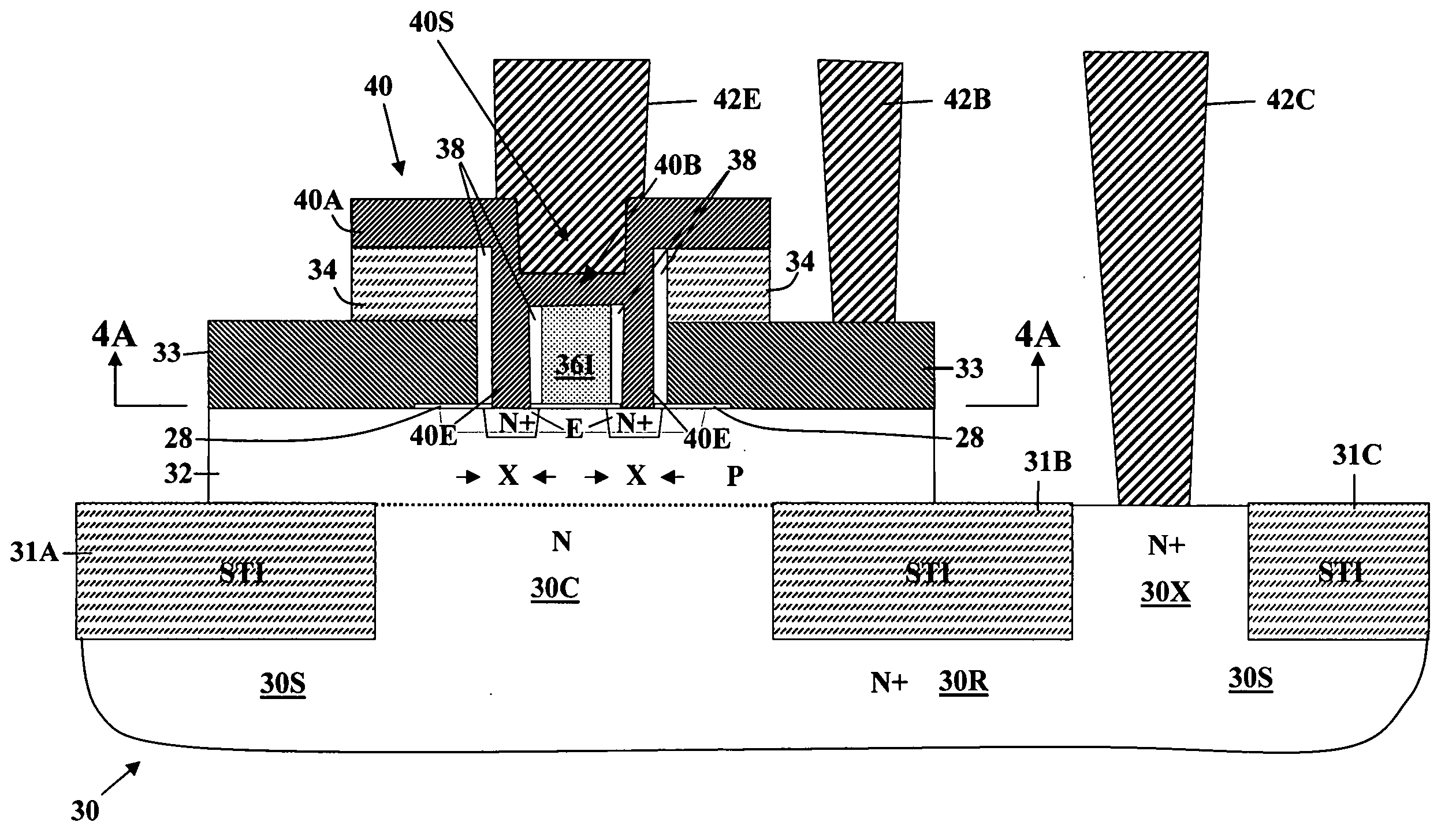

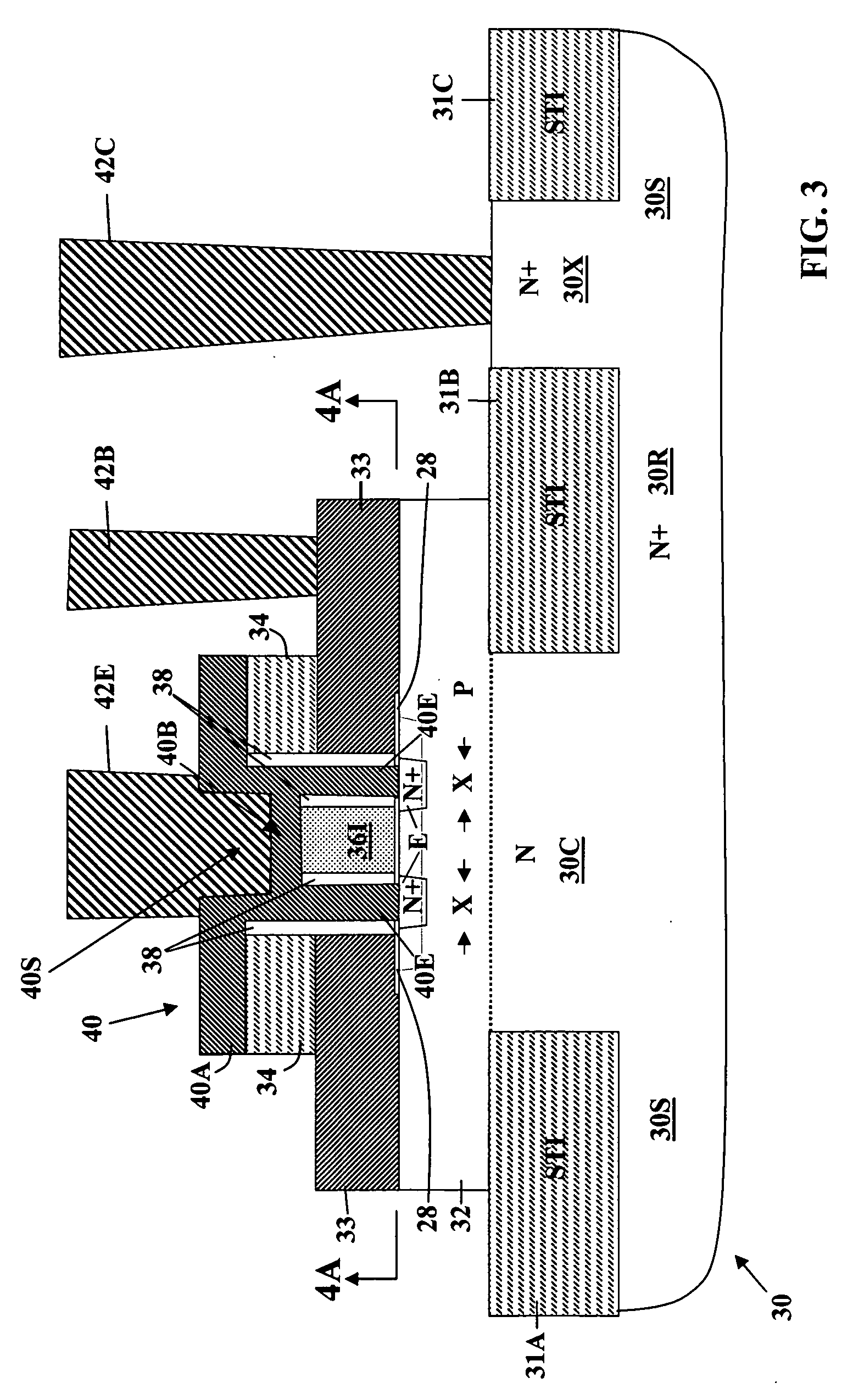

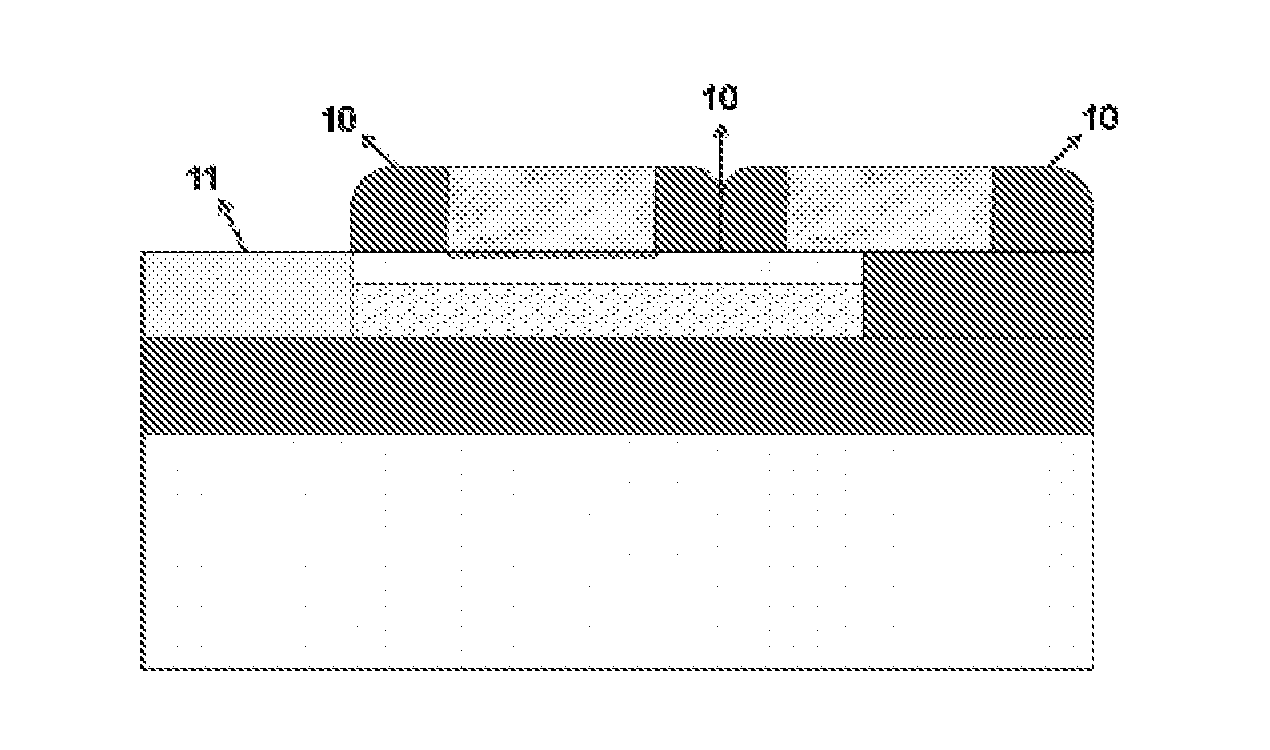

Method of manufacturing a bipolar transistor of double-polysilicon, heterojunction-base type and corresponding transistor

InactiveUS6744080B2TransistorSemiconductor/solid-state device manufacturingHeterojunctionEngineering

Transistor and method of manufacturing a bipolar transistor of the double-polysilicon, heterojunction-base type, in which a semiconducting layer with SiGe heterojunction is formed by non-selective epitaxy on an active region of a substrate and an insulating region surrounding the active region. At least one stop layer is formed on the semiconducting layer above a part of the active region. A layer of polysilicon and an upper insulating layer are formed on the semiconducting layer and on a part of the stop layer, leaving an emitter window free. An emitter region is formed by epitaxy in the emitter window, resting partially on the upper insulating layer and in contact with the semiconducting layer.

Owner:STMICROELECTRONICS SRL

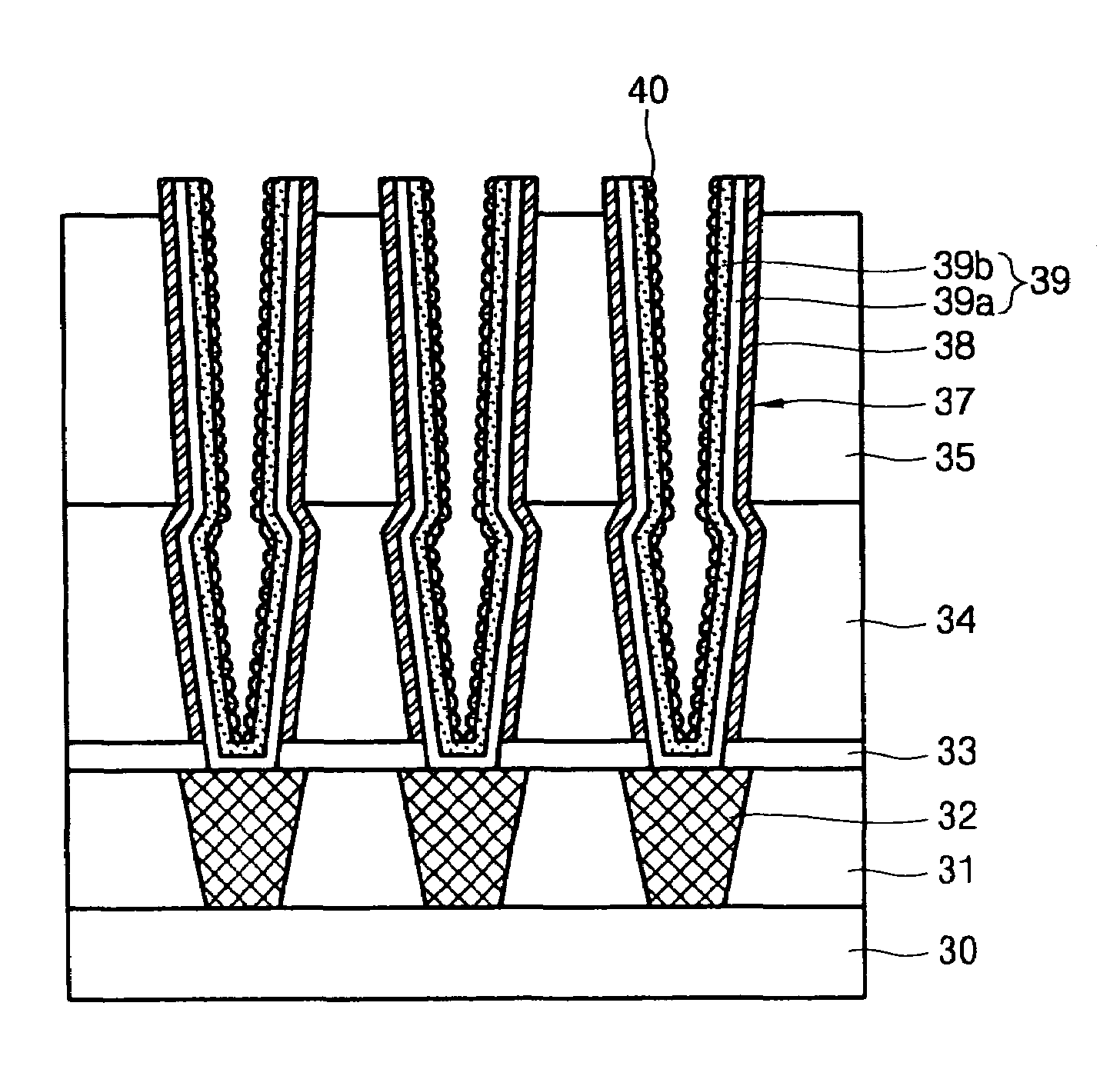

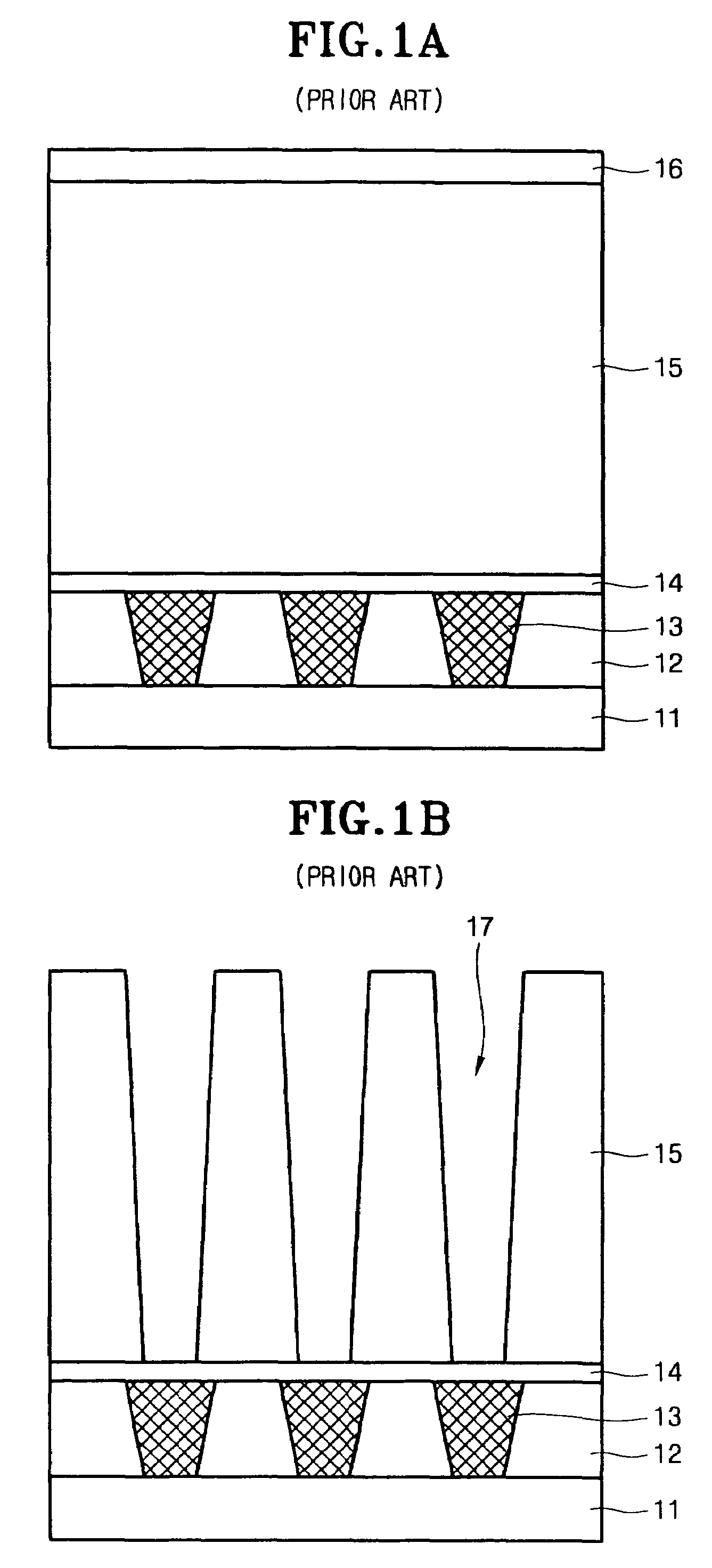

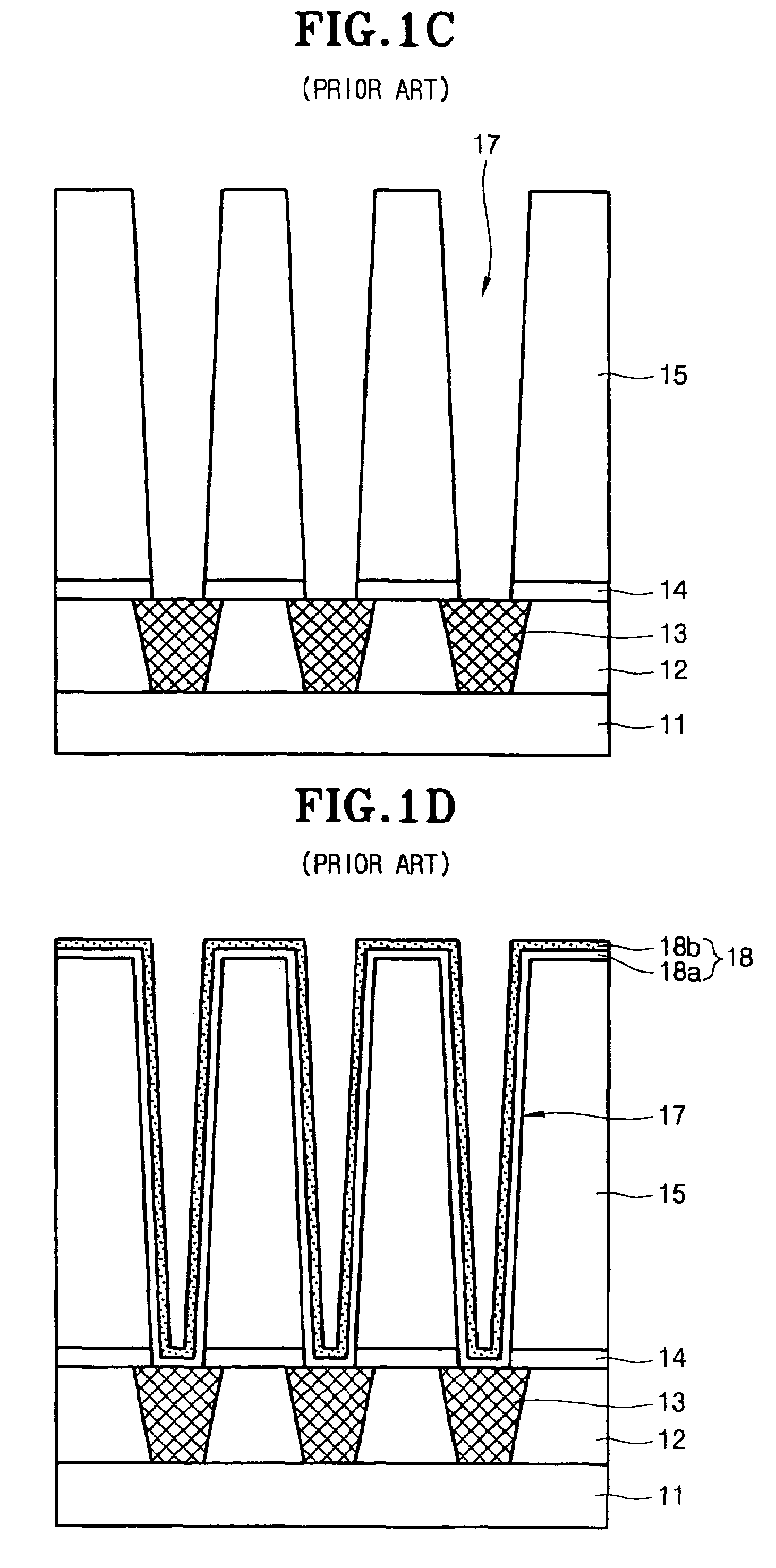

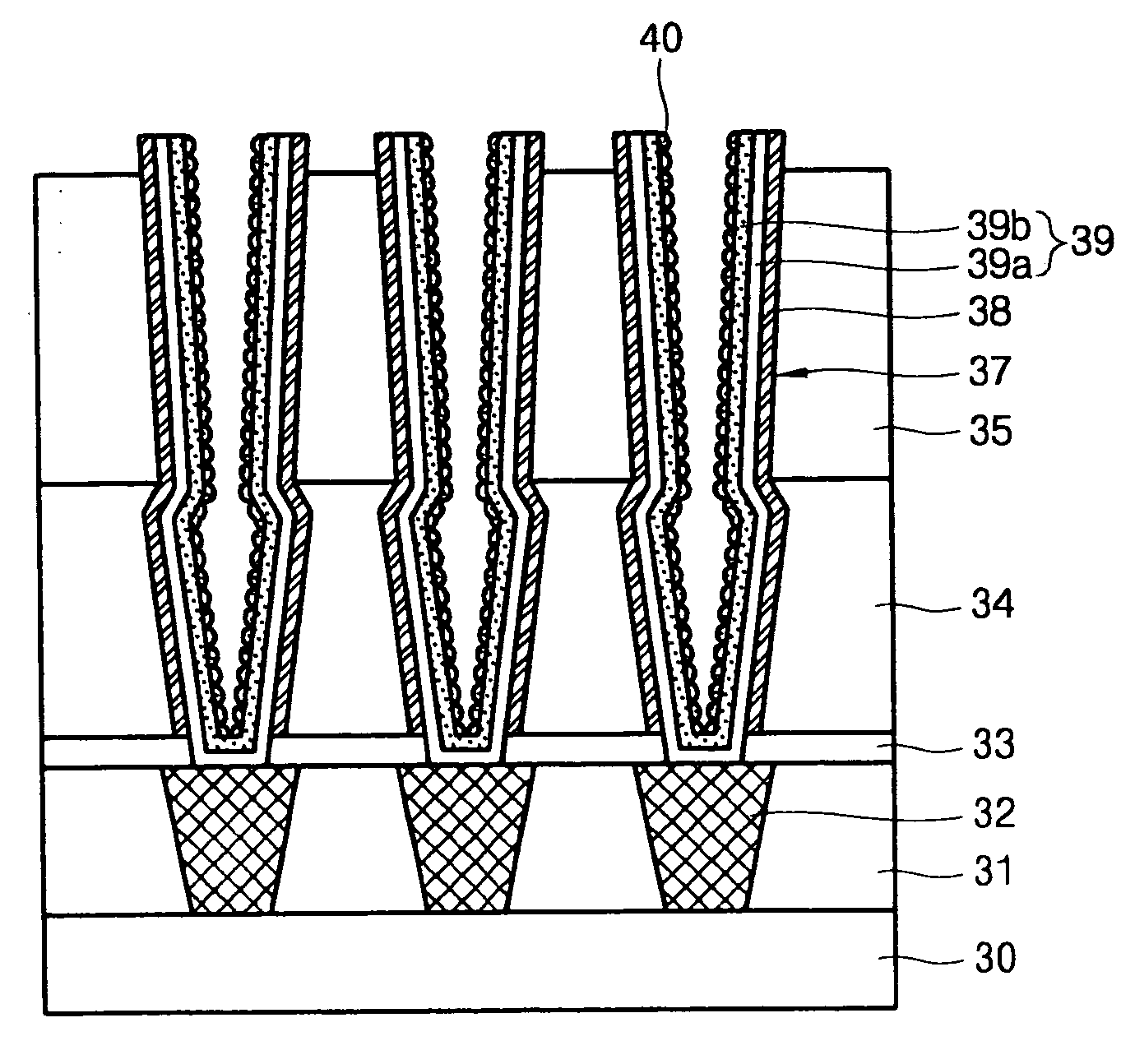

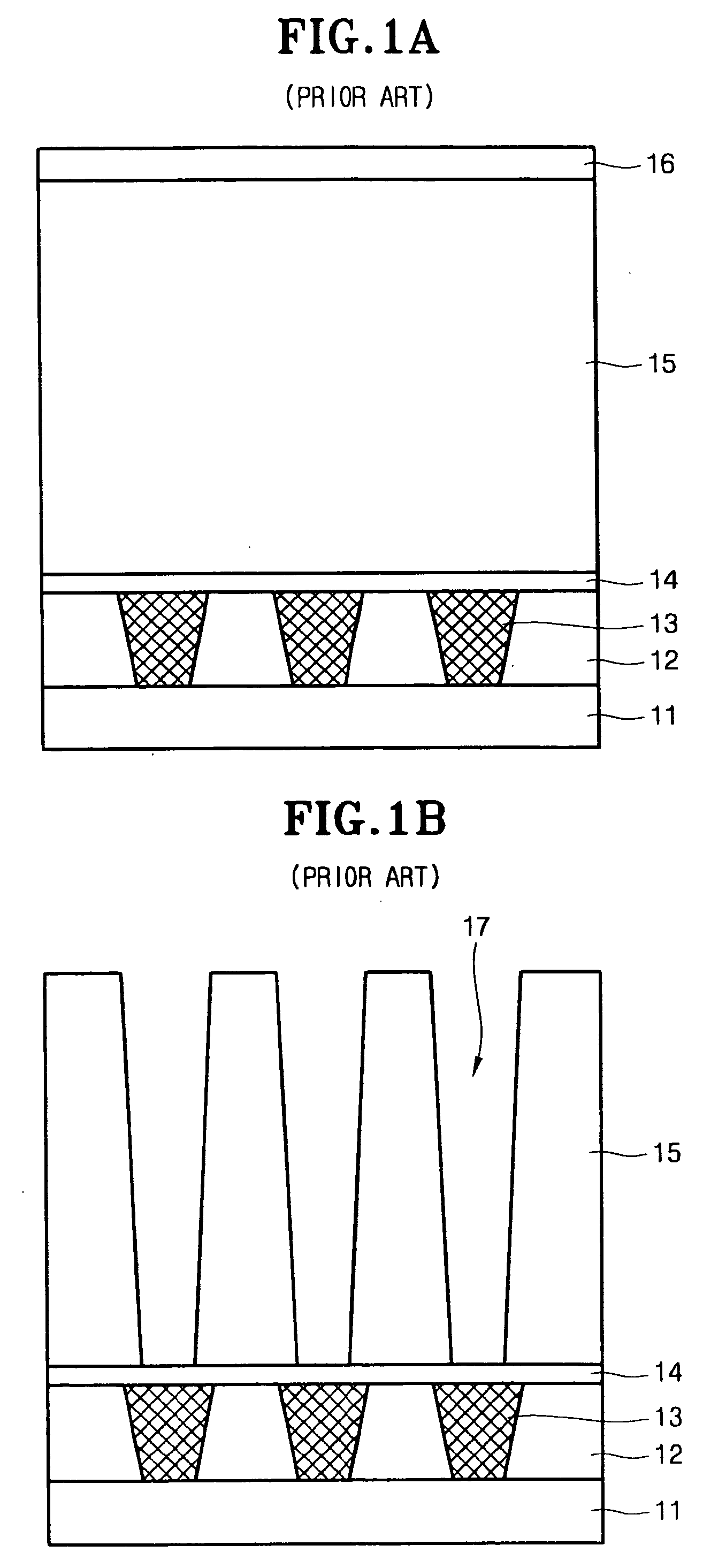

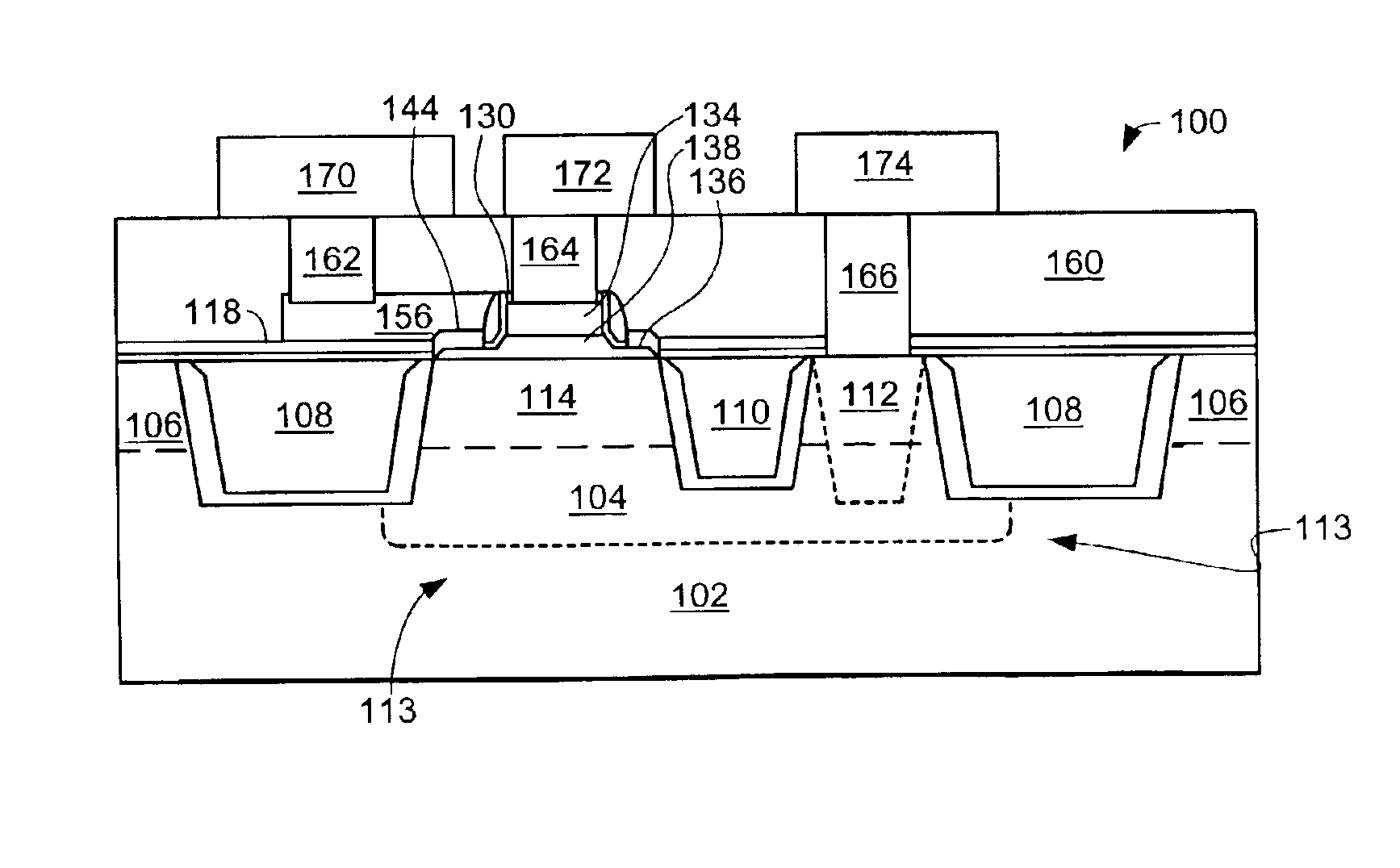

Method for forming capacitor of semiconductor device

InactiveUS7112506B2Increase the effective surface areaAvoid overgrowthTransistorSolid-state devicesNitrideDouble polysilicon

Disclosed is a method for forming a capacitor of a semiconductor device. An etch stop layer, first oxide layer and second oxide layer are sequentially deposited on an insulating interlayer of a substrate. Contact holes through which portions of the etch stop layer are exposed above plugs of the insulating interlayer are formed. The contact holes are cleaned by a cleaning solution having an etching selectivity which is higher for the first oxide layer than for the second oxide layer, thereby enlarging lower portions of the contact holes. A spacer nitride layer is formed on surfaces of the contact holes and the second oxide layer. Portions of the spacer nitride layers located on the second oxide layer and above the plugs together with portions of the etch stop layer located on the plugs are removed. A double polysilicon layer is formed on the spacer nitride layer segments.

Owner:SK HYNIX INC

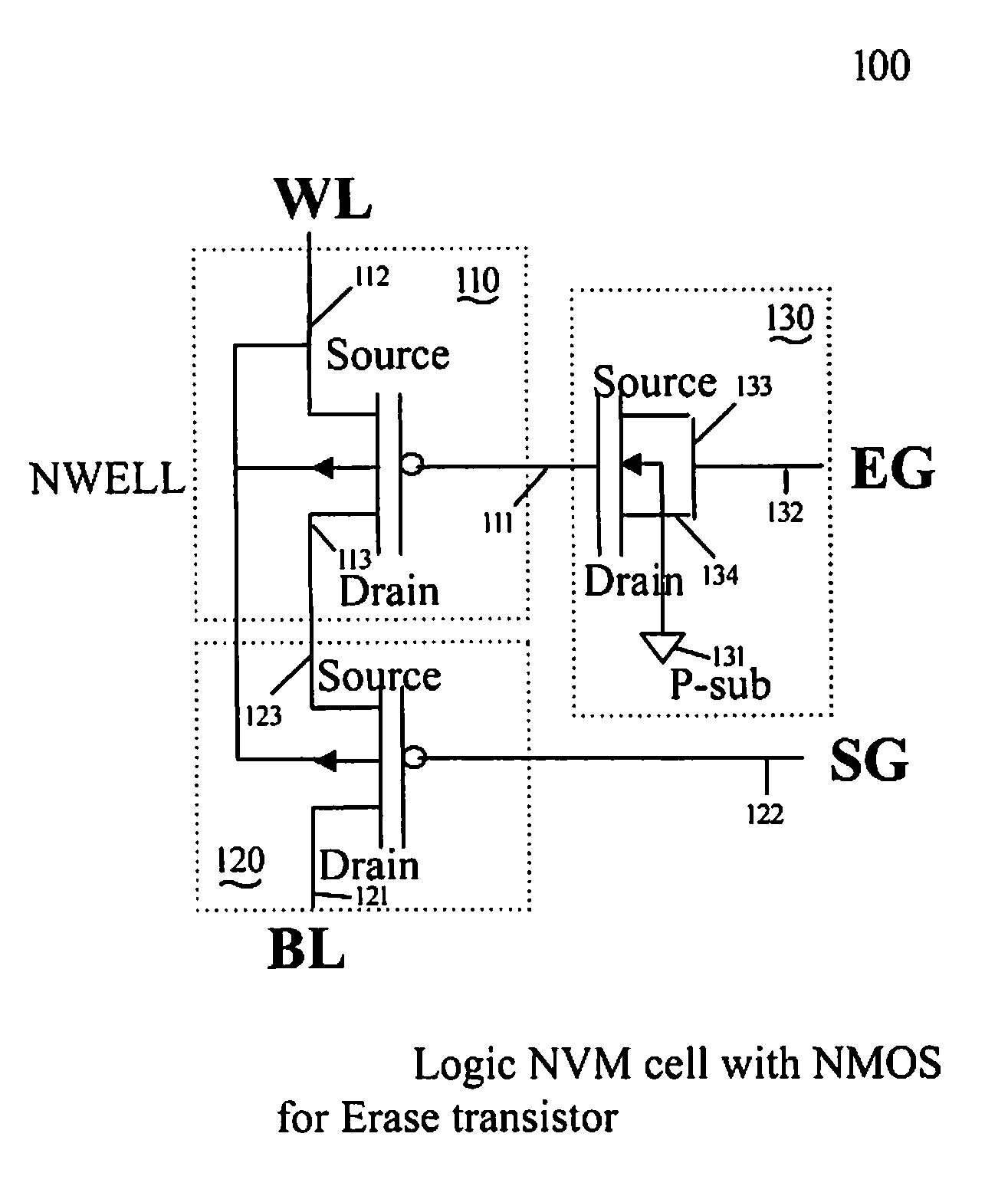

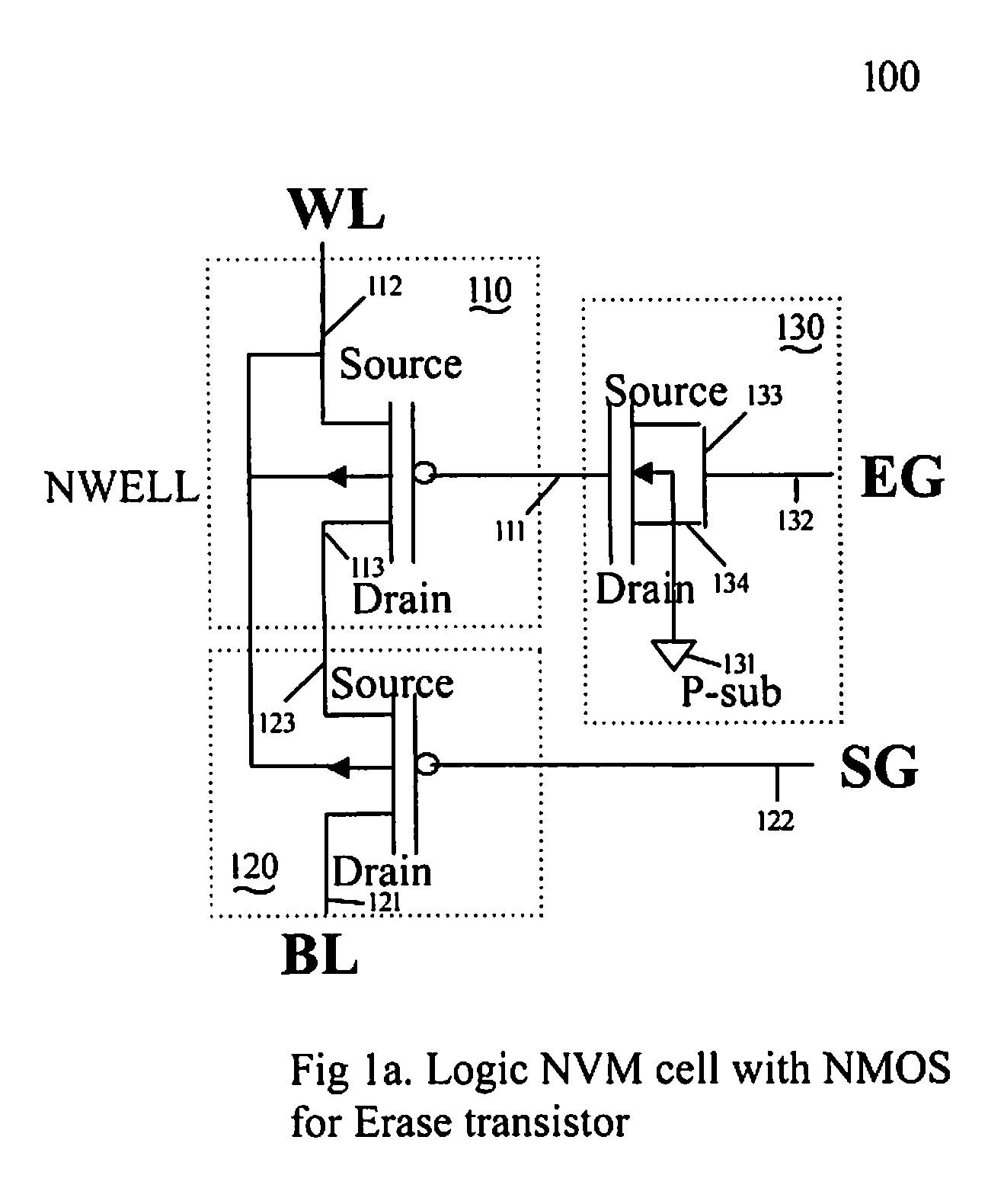

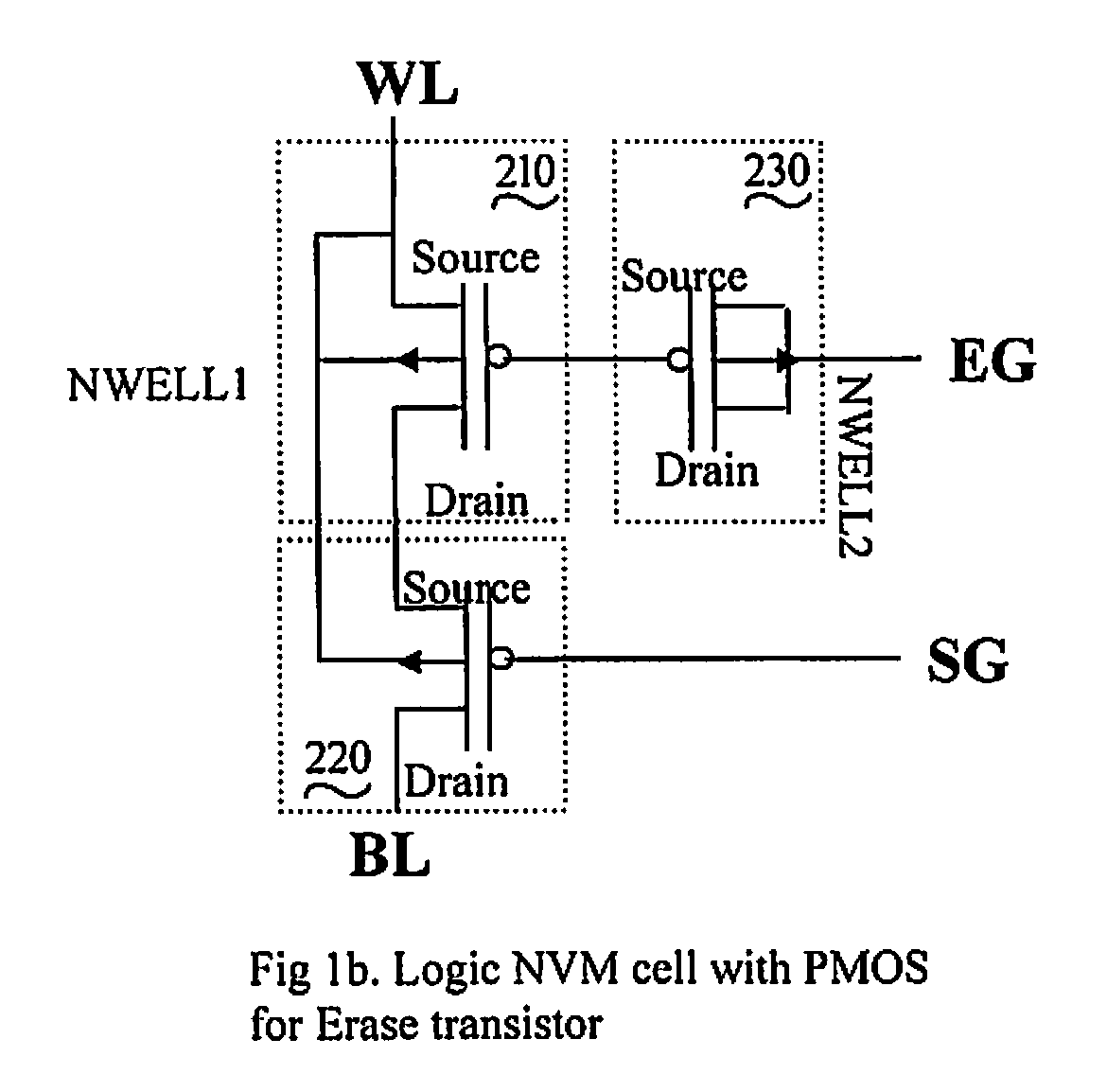

CMOS Logic Compatible Non-Volatile Memory Cell Structure, Operation, And Array Configuration

ActiveUS20090052245A1Reduce the erase voltageRead-only memoriesDigital storageLow voltageEngineering

The present invention is to provide a logic based single-poly non-volatile memory cell which is compatible with the CMOS process, uses lower voltages for operating, and is more reliable in program, read, or erase operation. A non-volatile memory cell in accordance with the present invention comprises a program transistor with a program transistor source as a first program terminal; a select transistor with a select transistor gate as a select terminal and a select transistor drain as a second program terminal; and an erase transistor with an erase transistor source and an erase transistor drain connected as an erase terminal, wherein the erase transistor shares a floating gate with the program transistor and the drain program transistor is connected to the select transistor source. By employing the present invention, significant cost advantages in feature-rich semiconductor products, such as System-on-Chip (SoC) design, compared to conventional dual-poly floating gate embedded Flash memory are provided.

Owner:INFINEON TECH LLC

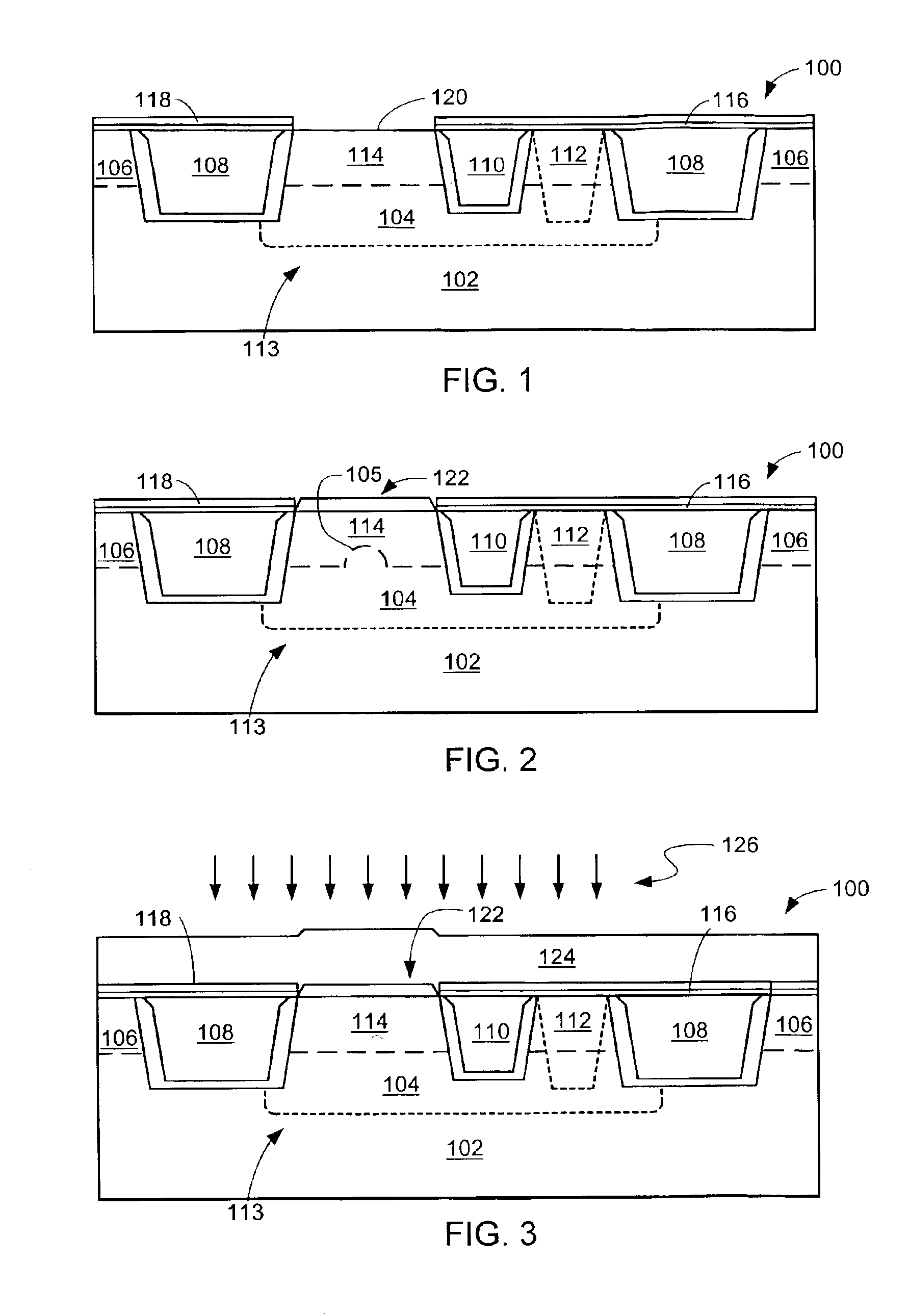

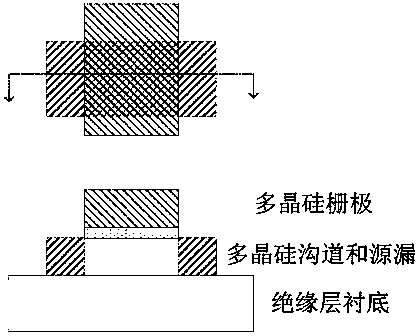

Process to integrate fabrication of bipolar devices into a CMOS process flow

A BiCMOS method for forming bipolar junction transistors and CMOS devices in a substrate. To avoid erosion of the bipolar junction transistor material layers, gate spacers for the CMOS devices are formed while a bipolar junction transistor photoresist layer is in place. The photoresist layer is used for etching the emitter polysilicon layer (for single polysilicon layer bipolar junction transistors) or for etching the base polysilicon layer (for double polysilicon layer bipolar junction transistors) prior to gate spacer etch.

Owner:AGERE SYST INC

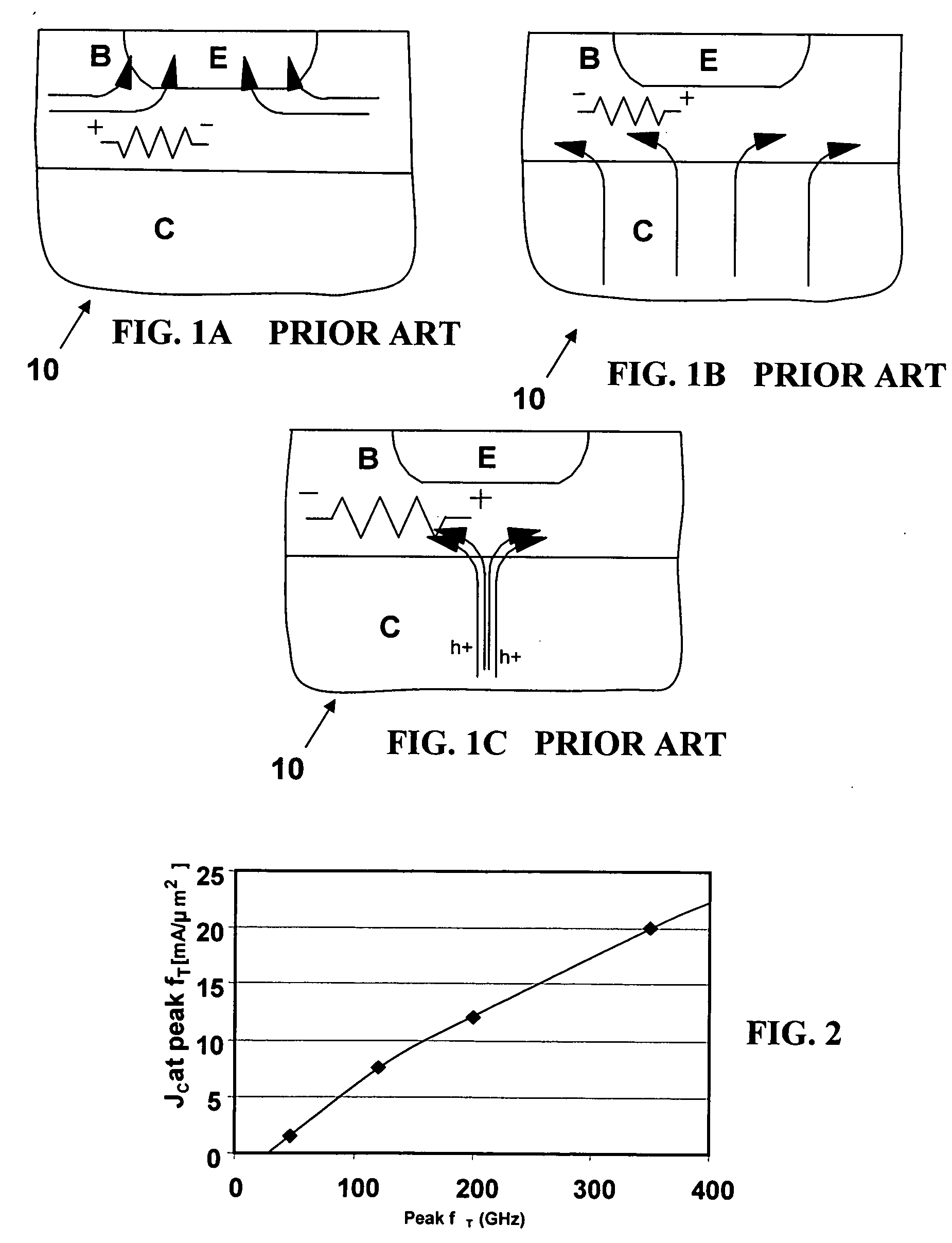

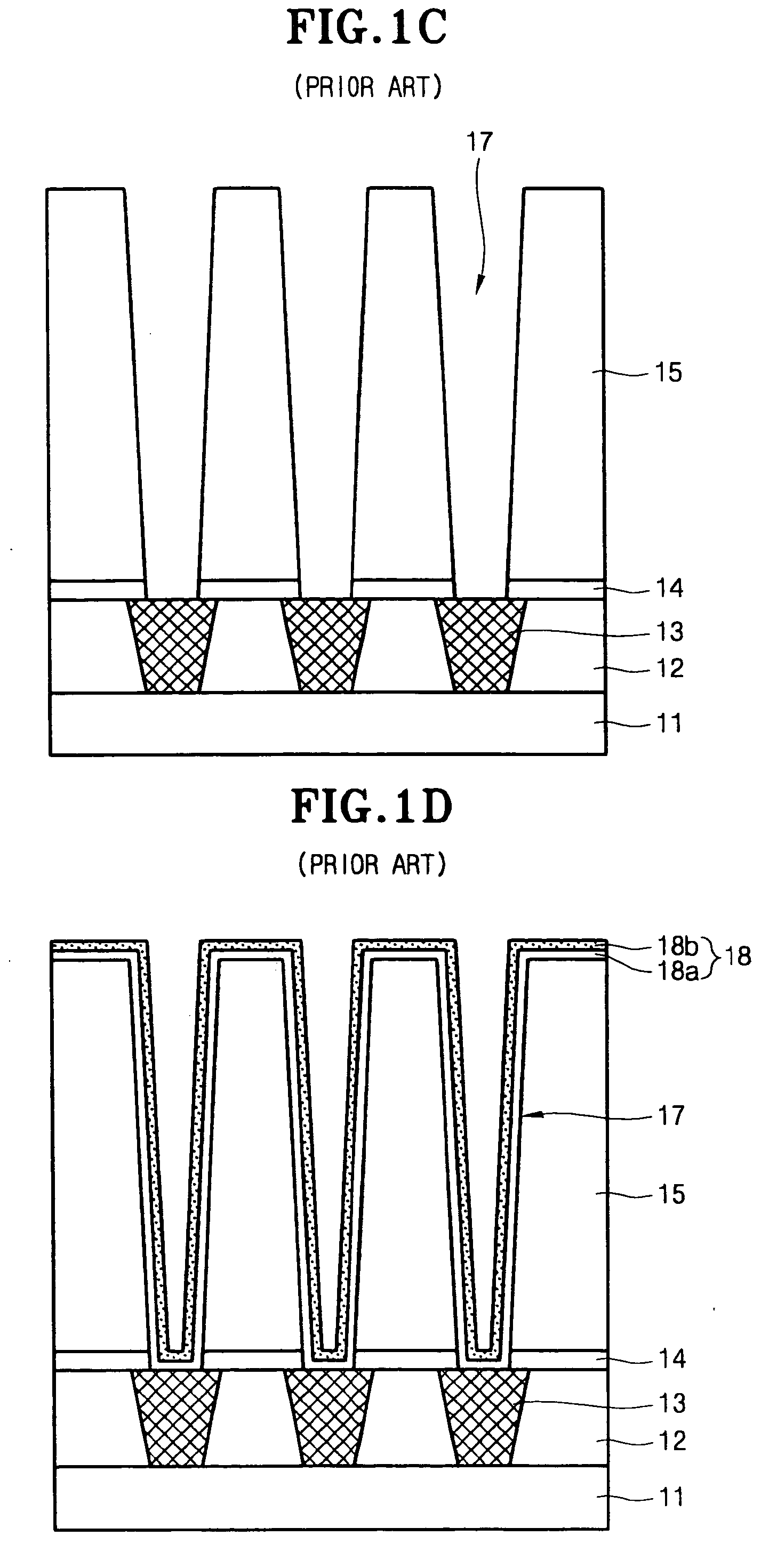

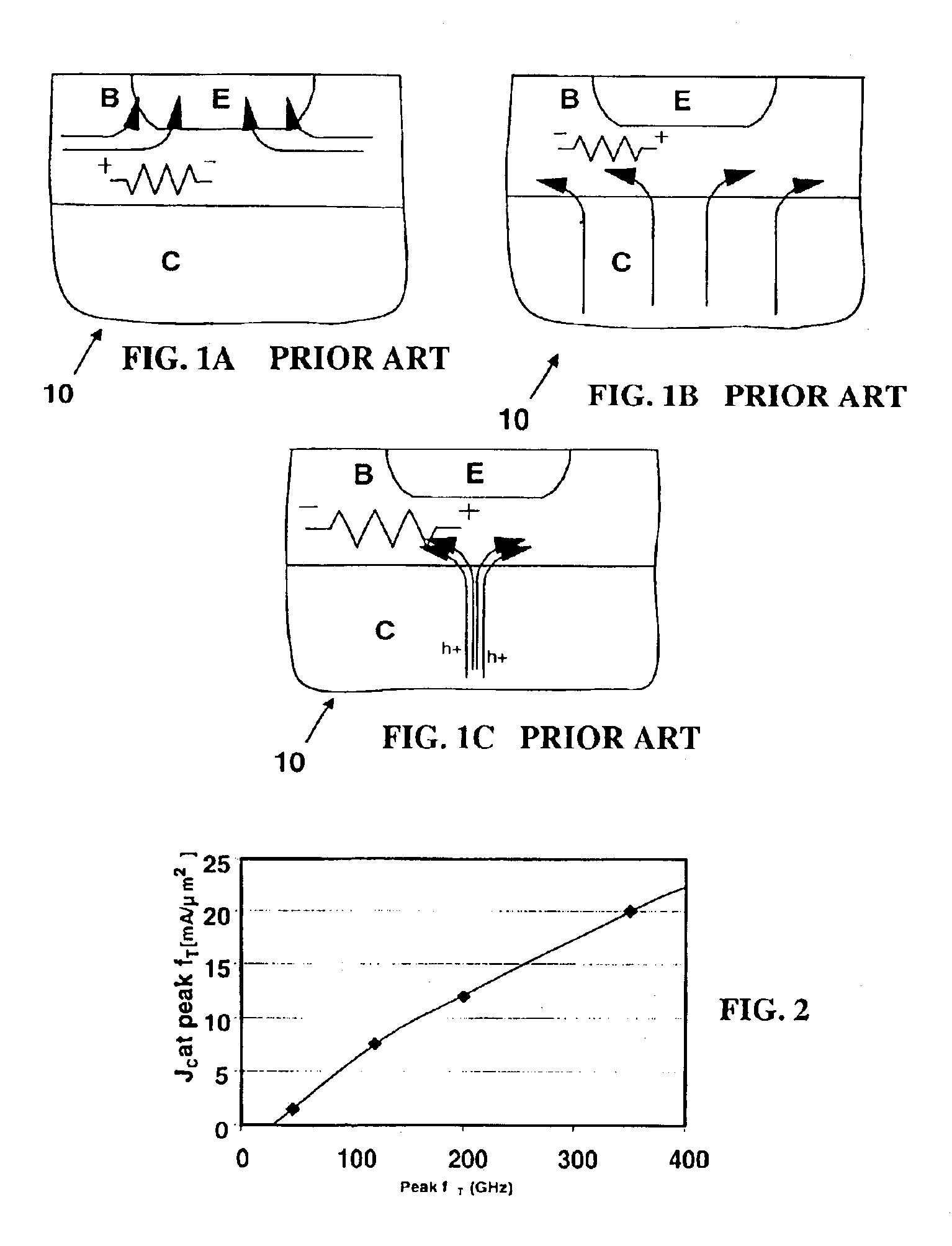

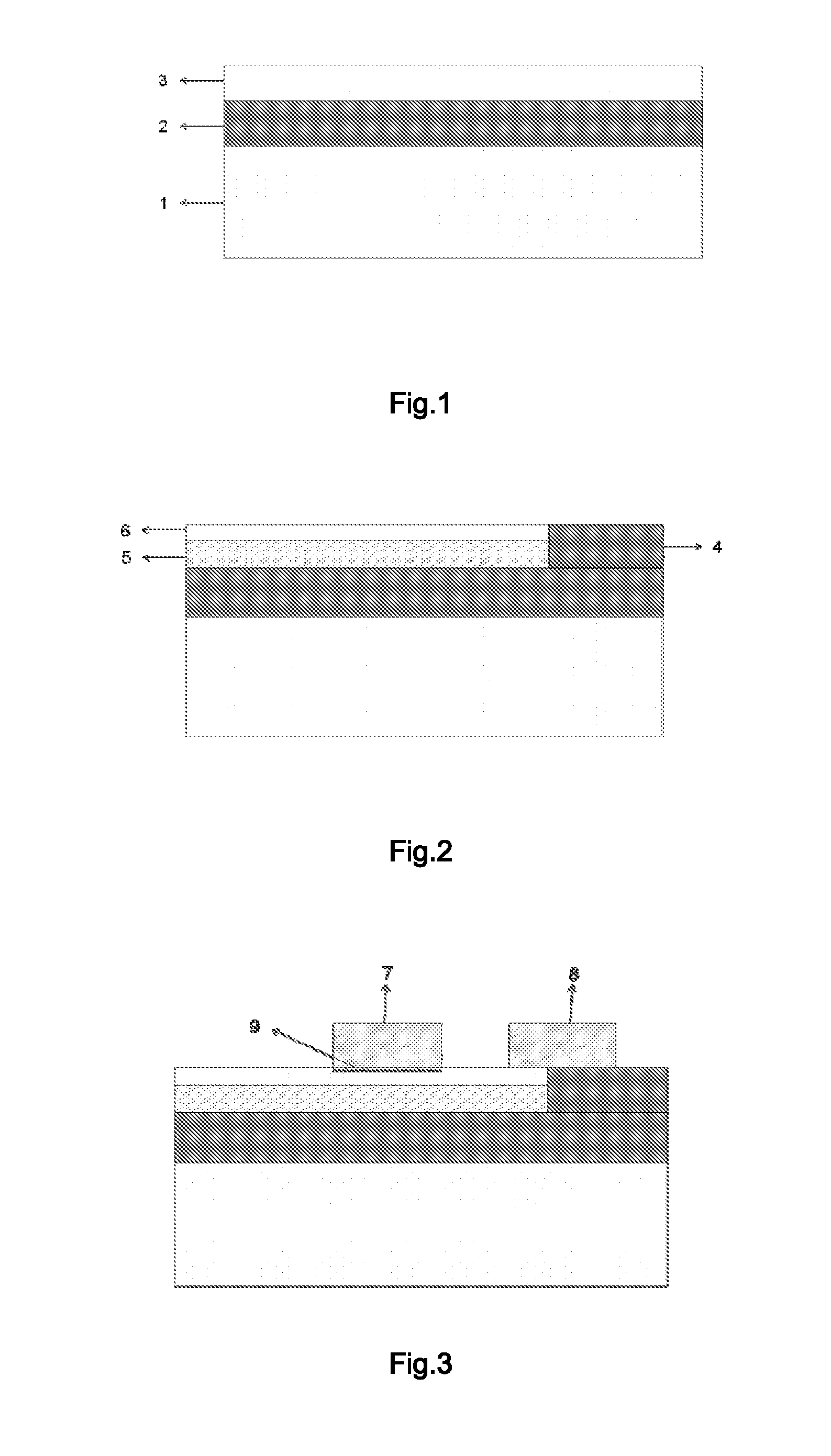

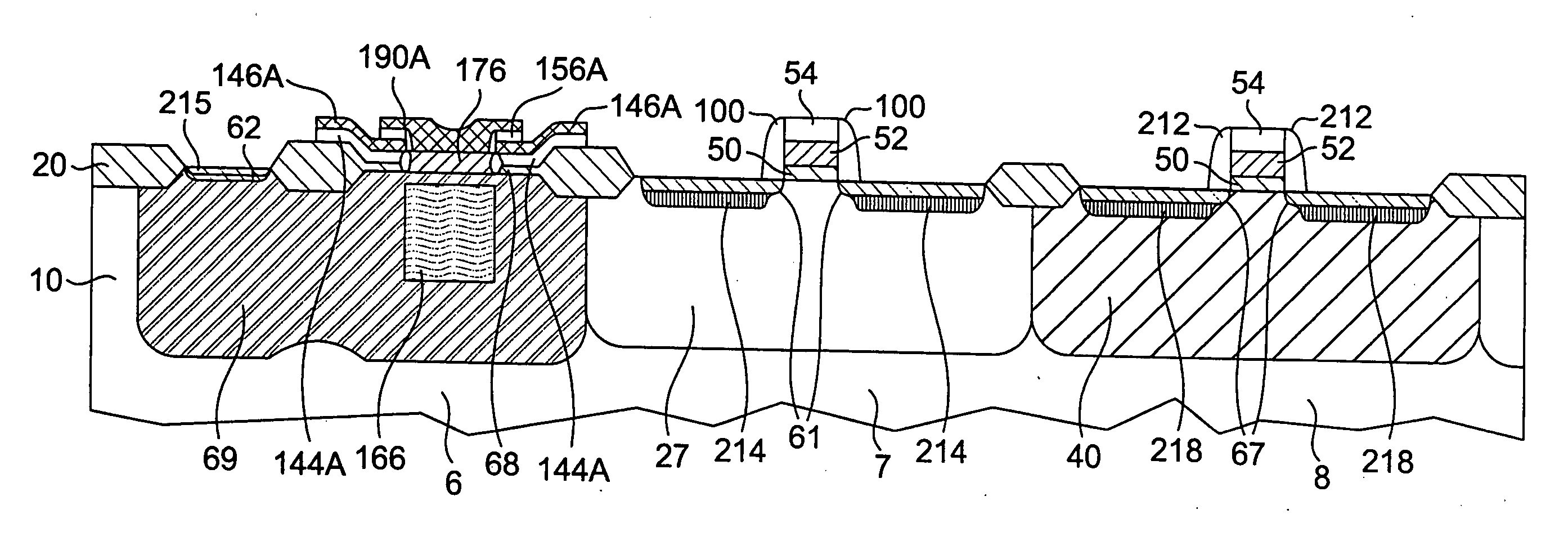

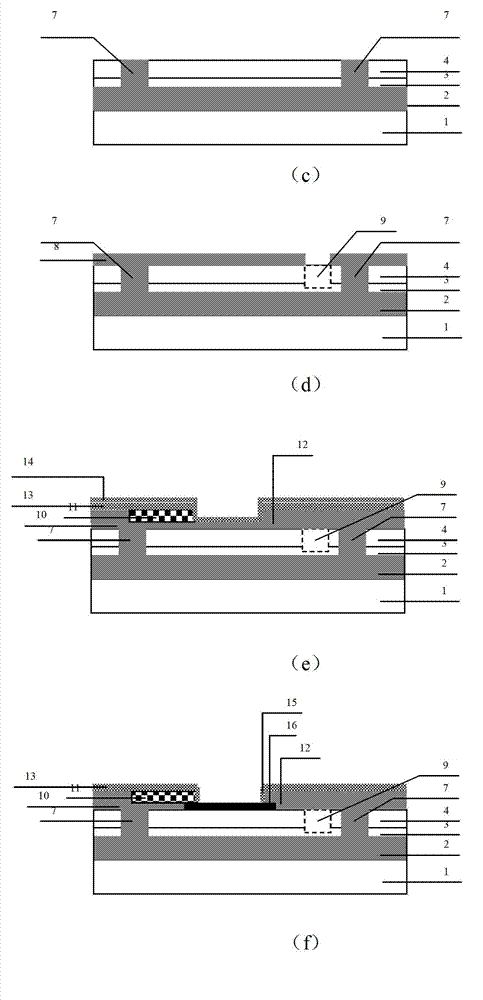

Bipolar transistor with a very narrow emitter feature

ActiveUS20050082642A1Lower resistanceHigh operating requirementsTransistorSemiconductor/solid-state device manufacturingOptoelectronicsContact layer

A double-polysilicon, self-aligned bipolar transistor has a collector region formed in a doped semiconductor substrate, an intrinsic counterdoped base formed on the surface of the substrate and a doped intrinsic emitter formed in the surface of the intrinsic base. An etch stop insulator layer overlies the intrinsic base layer above the collector. A base contact layer of a conductive material overlies the etch stop dielectric layer and the intrinsic base layer. A dielectric layer overlies the base contact layer. A wide window extends through the insulator layer and the base contact layer down to the insulator layer. An island or a peninsula is formed in the wide window leaving at least one narrowed window within the wide window, with sidewall spacers in either the wide window or the narrowed window. The narrowed windows are filled with doped polysilicon forming an extrinsic emitter with the intrinsic emitter formed below the extrinsic emitter in the surface of the intrinsic base.

Owner:IBM CORP

Method for forming capacitor of semiconductor device

InactiveUS20050202645A1Increase the effective surface areaAvoid overgrowthTransistorSolid-state devicesDevice materialNitride

Disclosed is a method for forming a capacitor of a semiconductor device. An etch stop layer, first oxide layer and second oxide layer are sequentially deposited on an insulating interlayer of a substrate. Contact holes through which portions of the etch stop layer are exposed above plugs of the insulating interlayer are formed. The contact holes are cleaned by a cleaning solution having an etching selectivity which is higher for the first oxide layer than for the second oxide layer, thereby enlarging lower portions of the contact holes. A spacer nitride layer is formed on surfaces of the contact holes and the second oxide layer. Portions of the spacer nitride layers located on the second oxide layer and above the plugs together with portions of the etch stop layer located on the plugs are removed. A double polysilicon layer is formed on the spacer nitride layer segments.

Owner:SK HYNIX INC

Method for creation of a very narrow emitter feature

A double-polysilicon, self-aligned bipolar transistor has a collector region formed in a doped semiconductor substrate, an intrinsic counterdoped base formed on the surface of the substrate and a doped emitter formed in the surface of the intrinsic base. Form an etch stop dielectric layer over the intrinsic base layer above the collector. Form a base contact layer of a conductive material over the etch stop dielectric layer and the intrinsic base layer. Form a second dielectric layer over the base contact layer. Etch a wide window through the dielectric layer and the base contact layer stopping the etching of the window at the etch stop dielectric layer. Form an island or a peninsula narrowing the wide window leaving at least one narrowed window within the wide window. Form sidewall spacers in the either the wide window or the narrowed window. Fill the windows with doped polysilicon to form an extrinsic emitter. Form an emitter below the extrinsic emitter in the surface of the intrinsic base.

Owner:IBM CORP

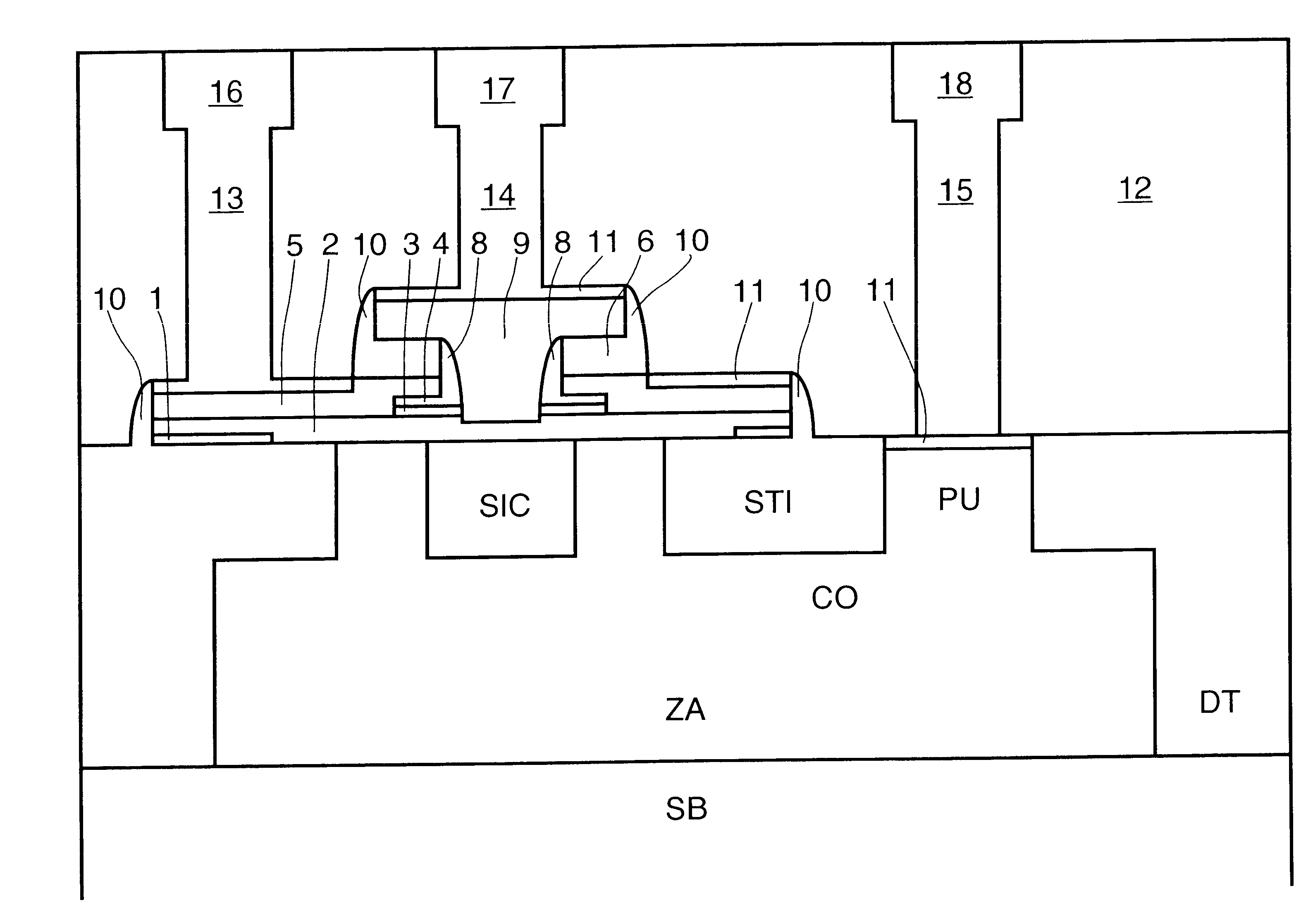

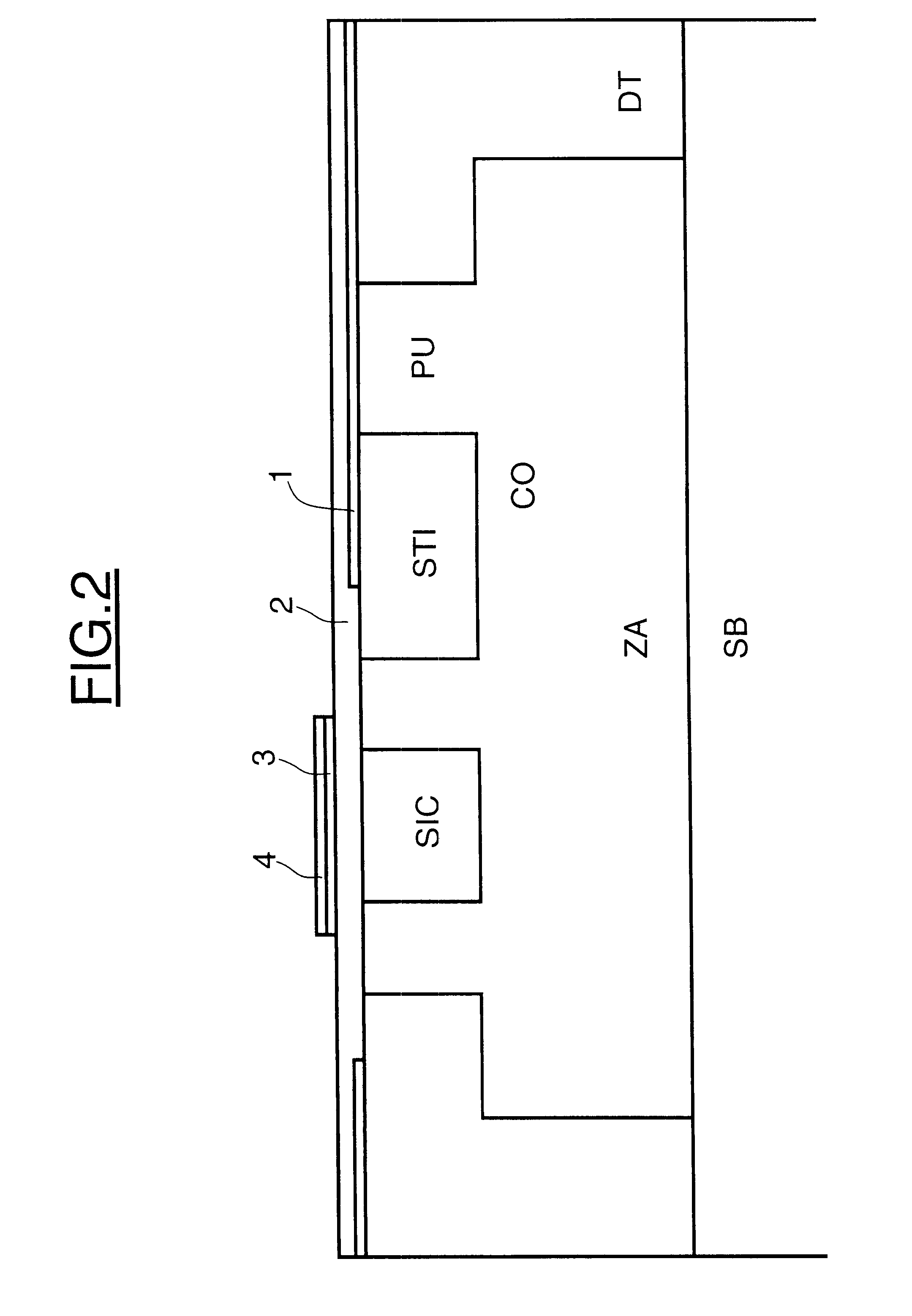

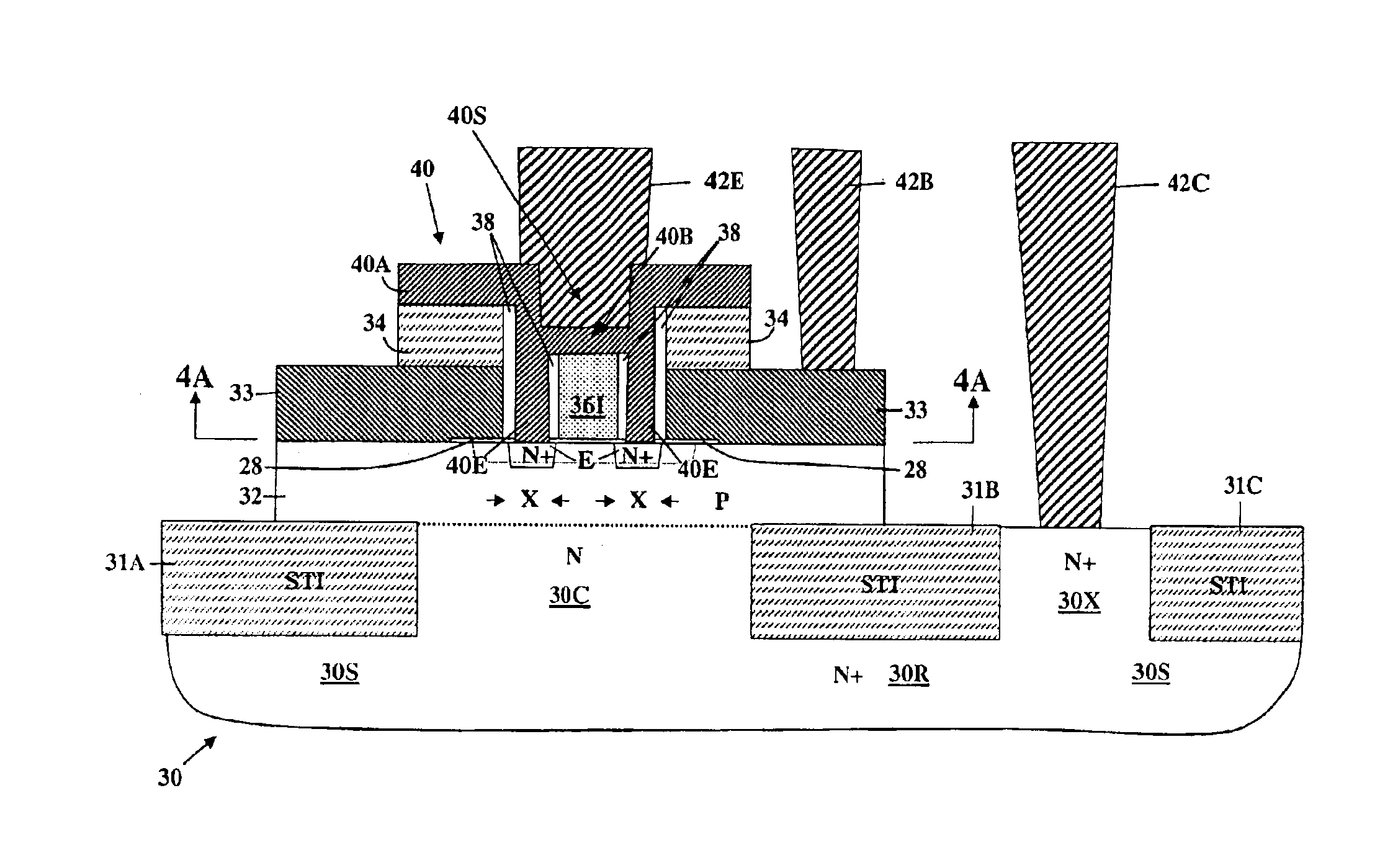

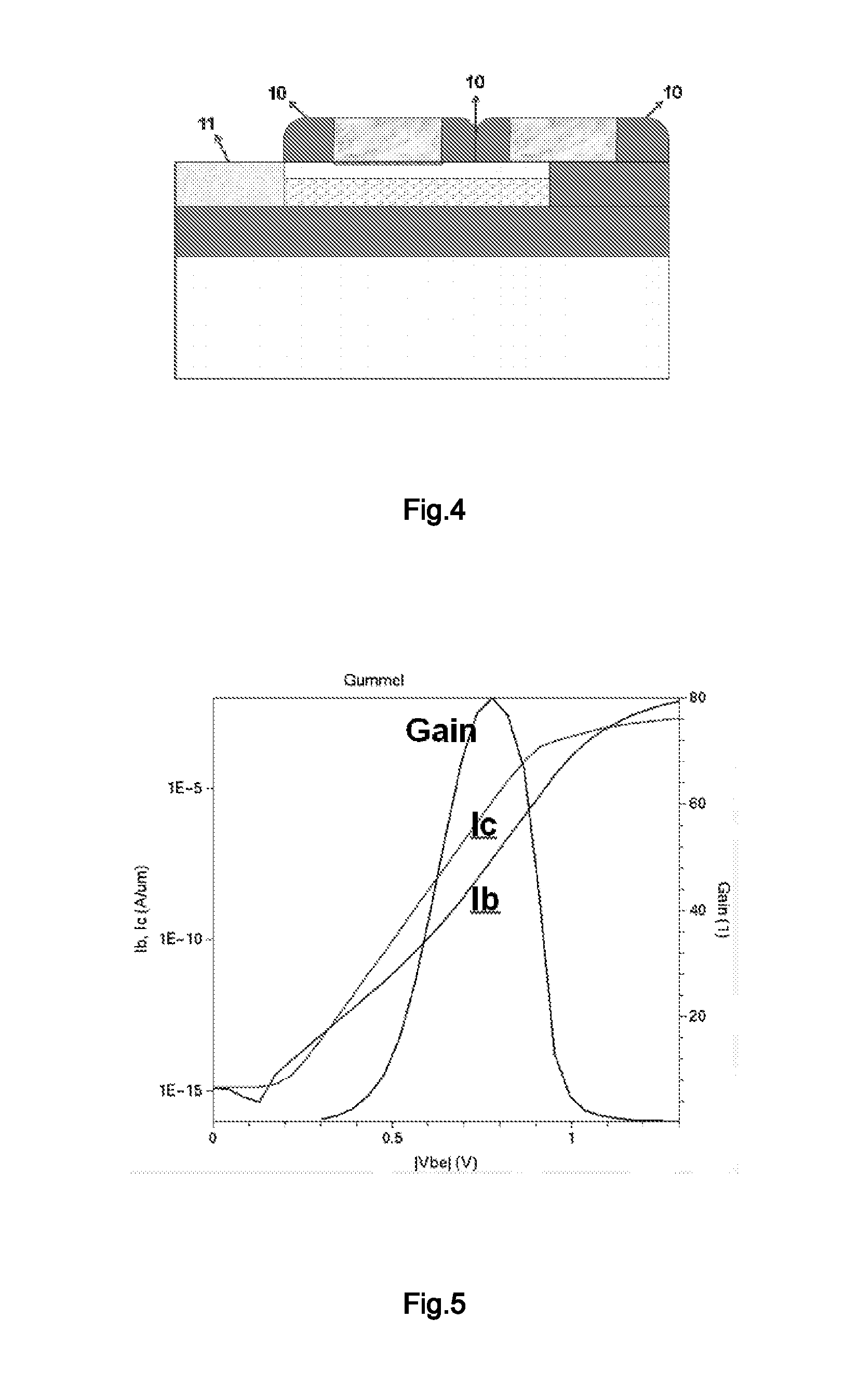

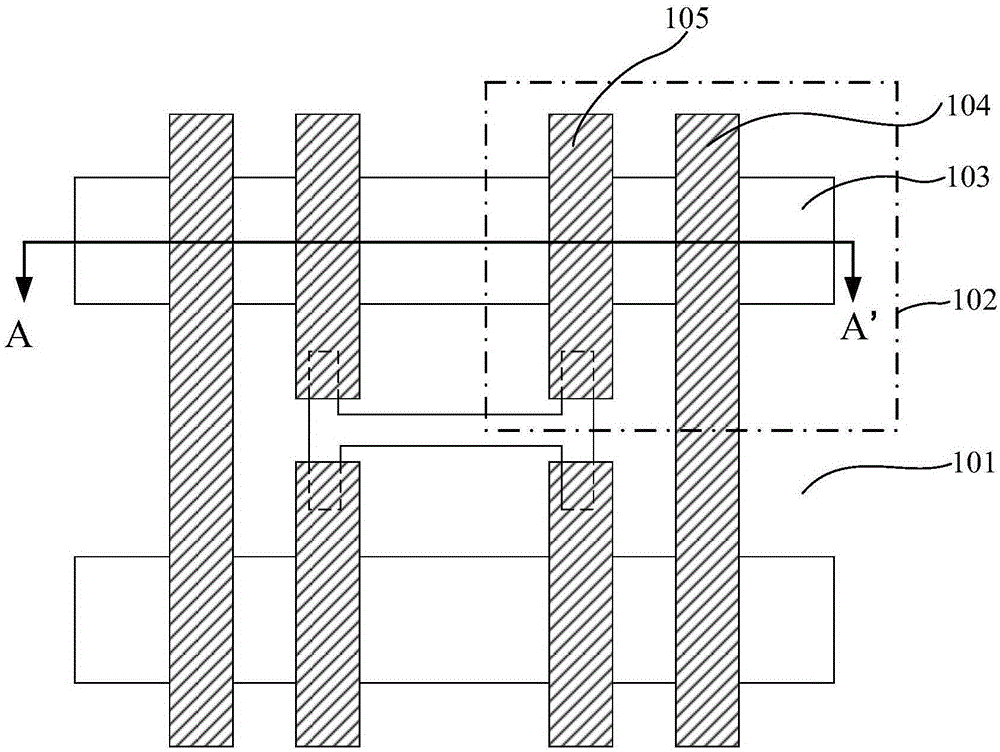

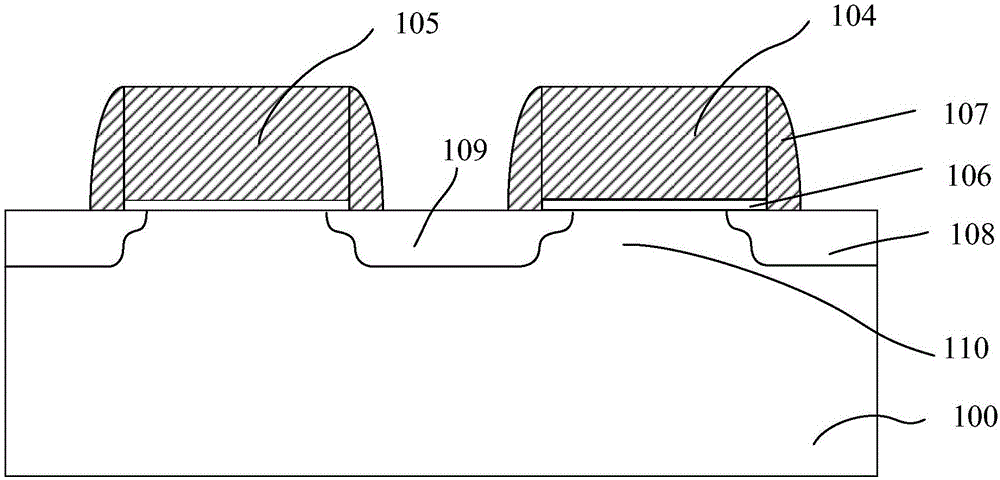

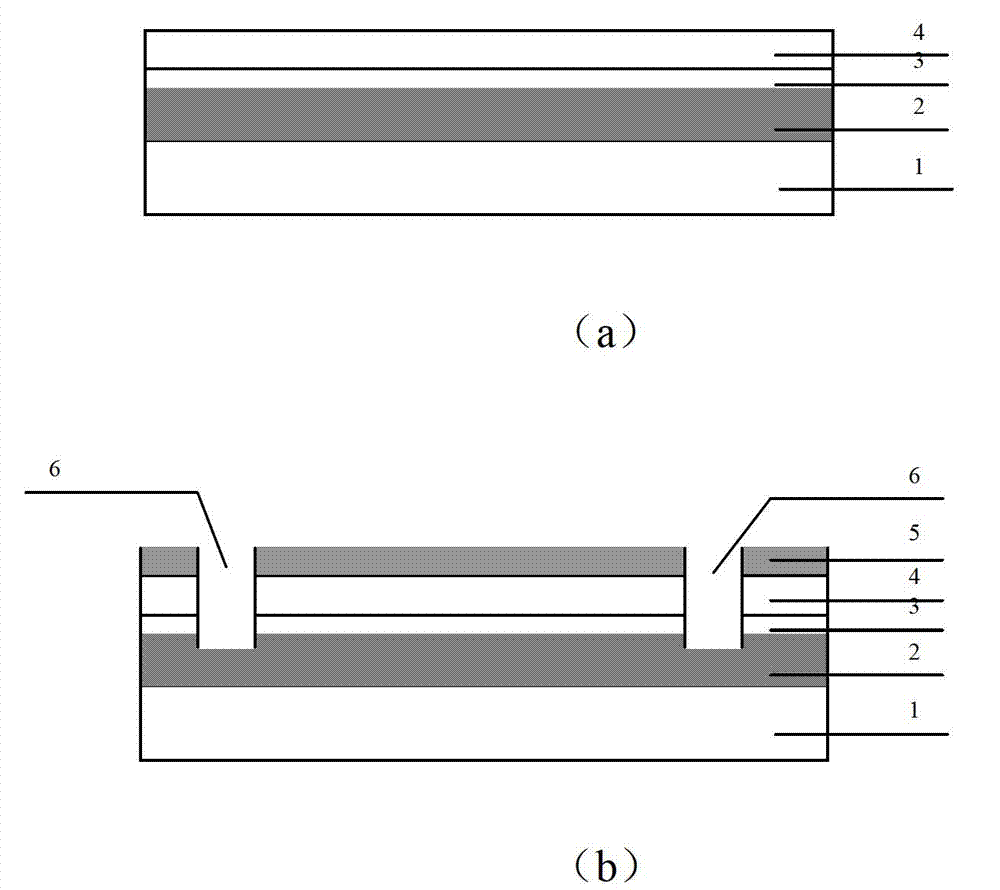

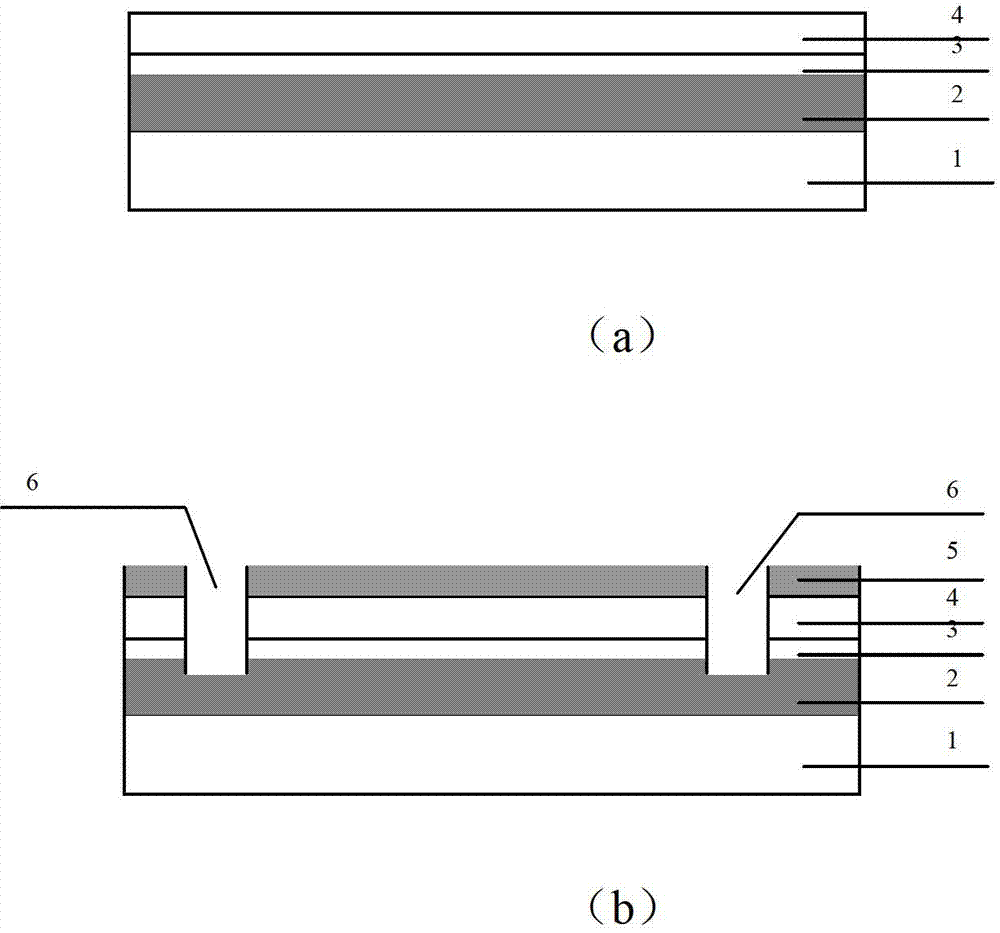

Vertical soi bipolar junction transistor and manufacturing method thereof

InactiveUS20110233727A1Highly integratedImprove compatibilitySemiconductor/solid-state device manufacturingSemiconductor devicesSoi cmosSoi substrate

The present invention discloses a vertical SOI bipolar junction transistor and a manufacturing method thereof. The bipolar junction transistor includes an SOI substrate from down to up including a body region, a buried oxide layer and a top silicon film; an active region located in the top silicon film formed by STI process; a collector region located in the active region deep close to the buried oxide layer formed by ion implantation; a base region located in the active region deep close to the top silicon film formed by ion implantation; an emitter and a base electrode both located over the base region; a side-wall spacer located around the emitter and the base electrode. The present invention utilizing a simple double poly silicon technology not only can improve the performance of the transistor, but also can reduce the area of the active region in order to increase the integration density. Furthermore, the present invention utilizes side-wall spacer process to improve the compatibility of SOI BJT and SOI CMOS, which simplifies the SOI BiCMOS process and thus reduce the cost.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

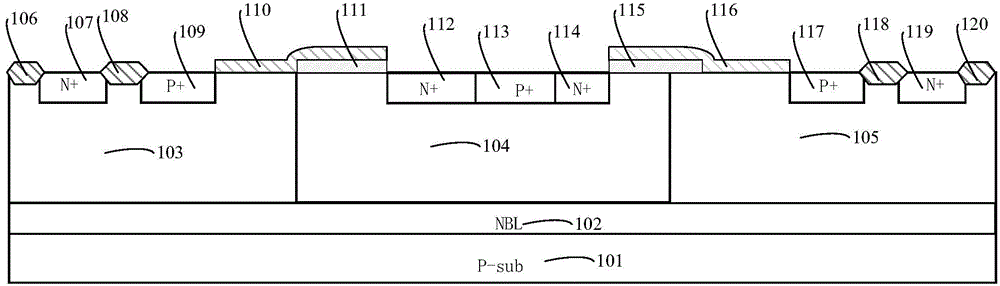

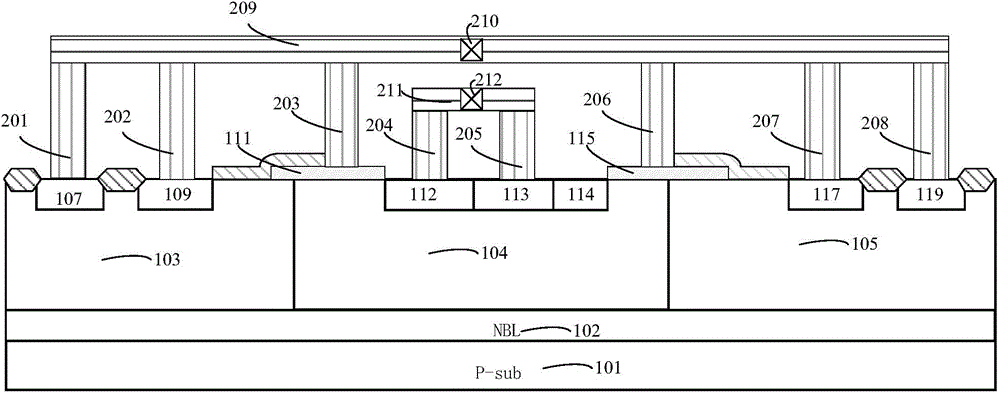

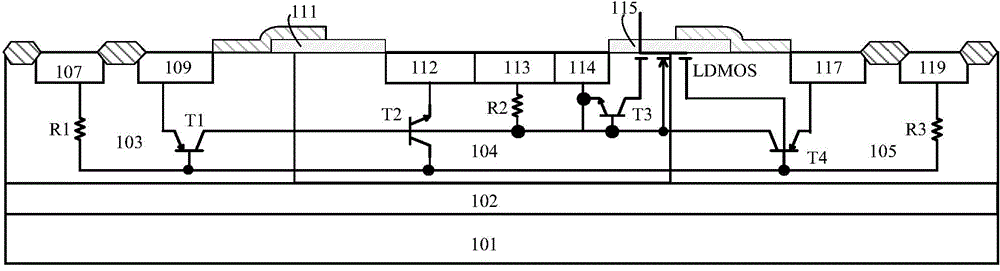

High-voltage ESD protection device with small hysteresis window

ActiveCN104576639ALower the trigger voltageIncrease holding voltageSolid-state devicesSemiconductor devicesHysteresisElectrical resistance and conductance

The invention discloses a high-voltage ESD protection device with a small hysteresis window. The high-voltage ESD protection device can be used for an ESD protection circuit of an on-chip high-voltage IC. The high-voltage ESD protection device mainly comprises a P type substrate, an N type buried layer, an N well, P wells, a plurality of P+ injection regions, a plurality of N+ injection regions, double polysilicon gates and a plurality of field oxide isolation regions. According to the protection device, two ESD current discharge paths consisting of LDMOSs and SCRs are formed under the action of high-voltage ESD pulses; parasitic PNP transistors and N-well resistors form a common branch of the current discharge paths, so that the electron emissivity of the device is reduced, and the maintaining voltage and ESD robustness are improved; in addition, a Zener diode is arranged in the device so as to reduce triggering voltage and realize high-voltage ESD protection with the small hysteresis window.

Owner:JIANGNAN UNIV

Process to integrate fabrication of bipolar devices into a CMOS process flow

A BiCMOS method for forming bipolar junction transistors and CMOS devices in a substrate. To avoid erosion of the bipolar junction transistor material layers, gate spacers for the CMOS devices are formed while a bipolar junction transistor photoresist layer is in place. The photoresist layer is used for etching the emitter polysilicon layer (for single polysilicon layer bipolar junction transistors) or for etching the base polysilicon layer (for double polysilicon layer bipolar junction transistors) prior to gate spacer etch.

Owner:AGERE SYST INC

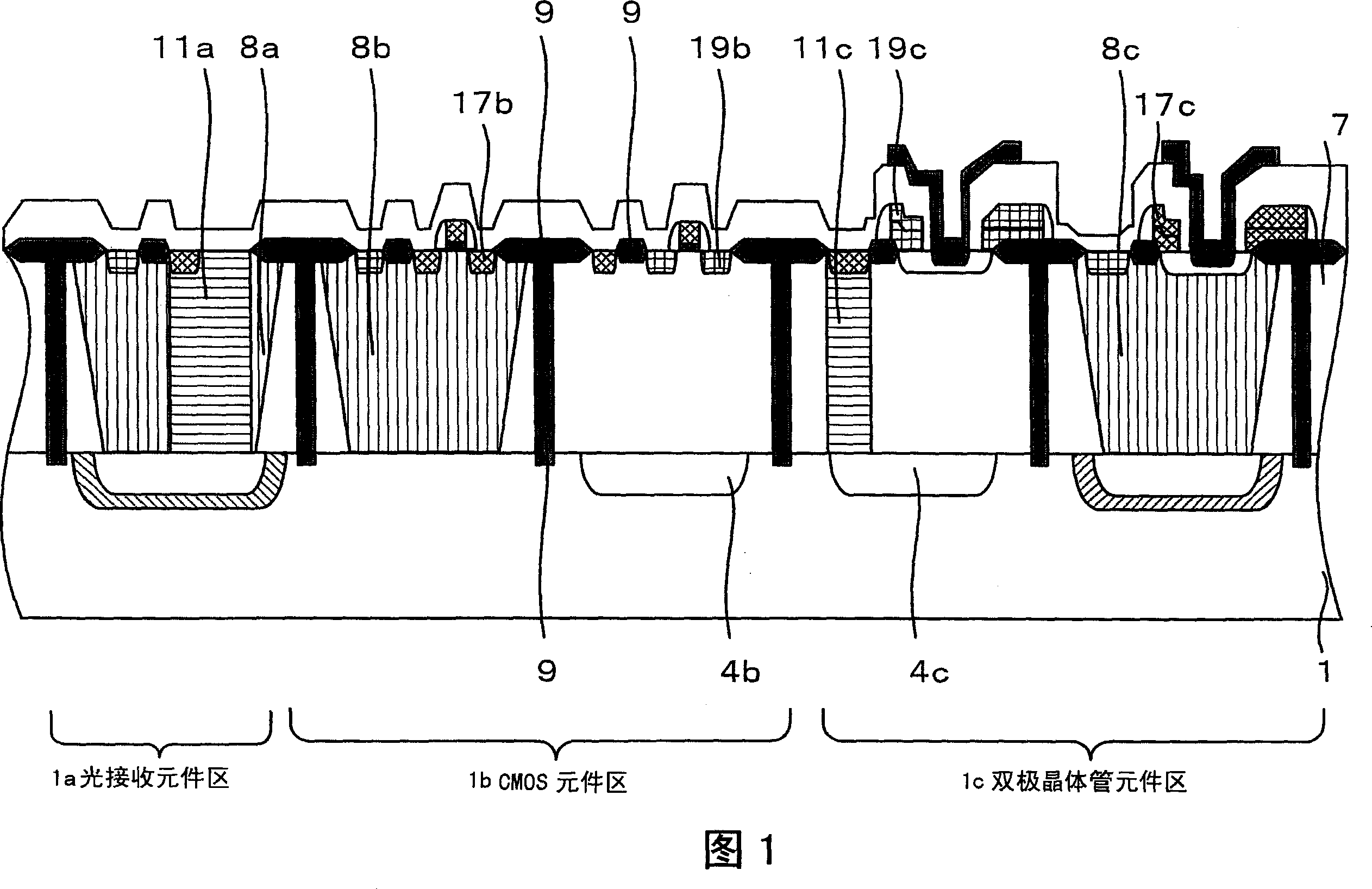

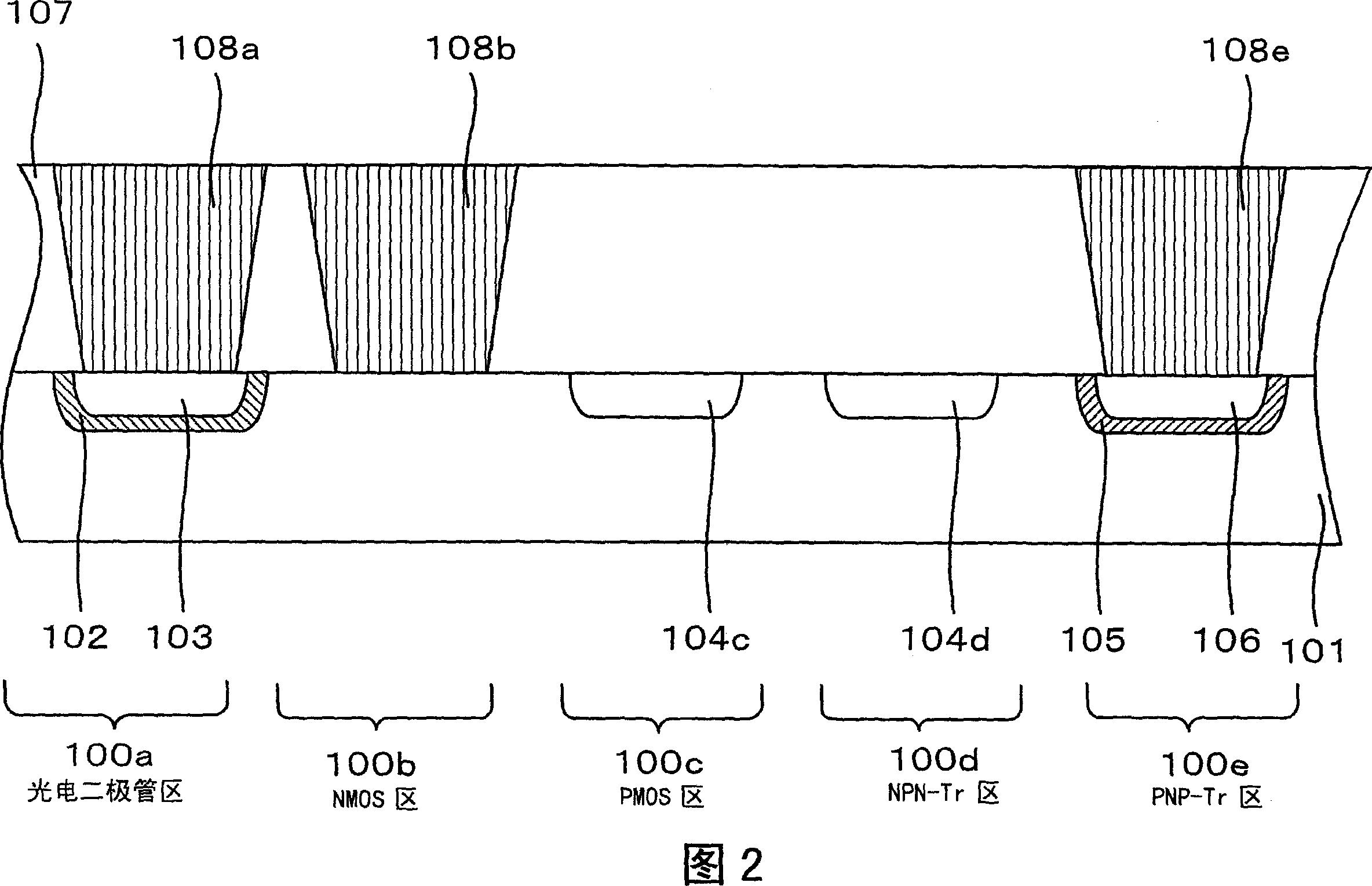

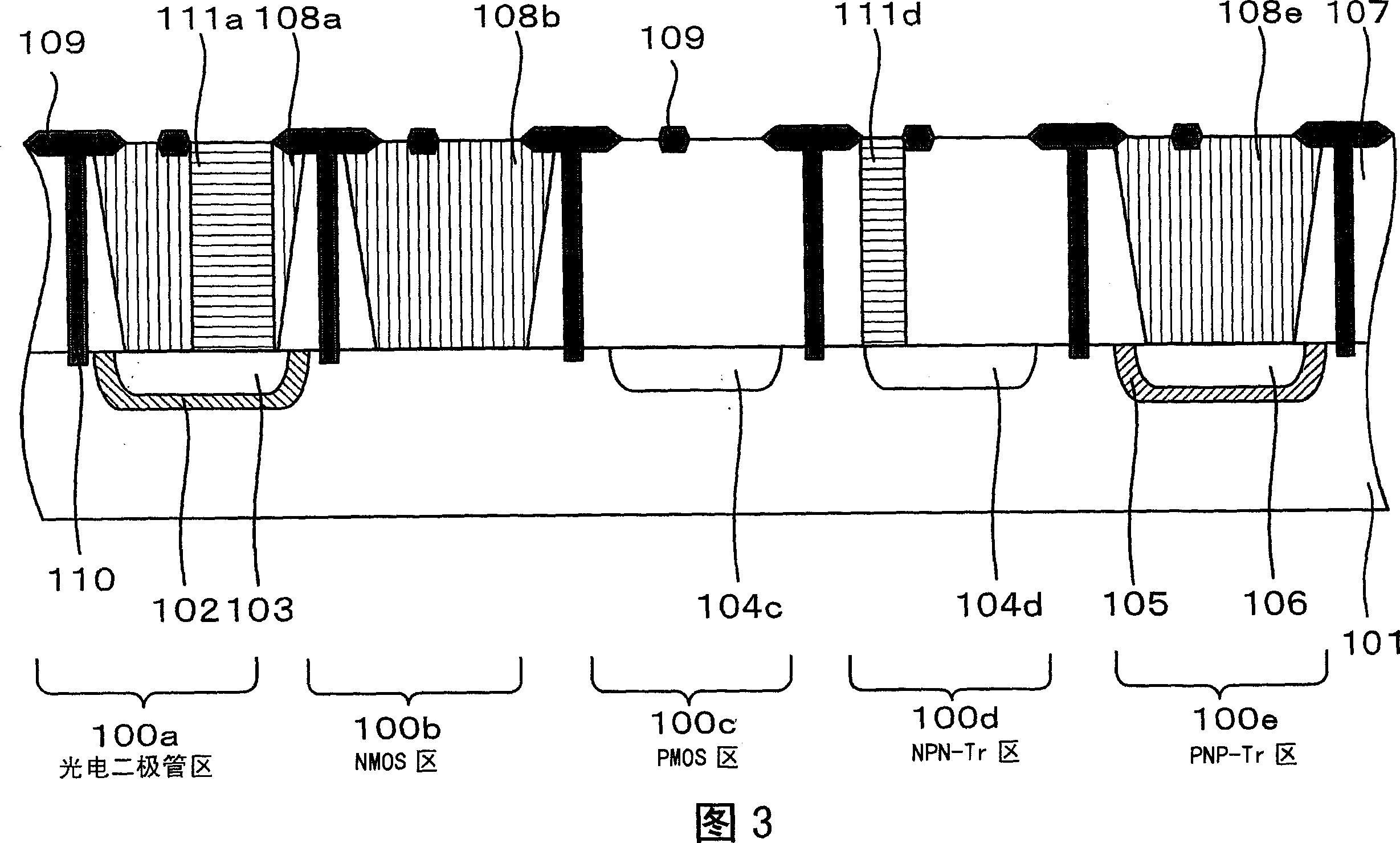

Method of manufacturing semiconductor device

A method of manufacturing a high-speed operable and broadband operable semiconductor device where a light-receiving element section, a CMOS element and a bipolar transistor element having a double polysilicon structure are formed on one chip. By performing the same conductivity type ion implantation, the same conductivity type diffusion layers (examples thereof include N-type diffusion layers, an anode diffusion layer, P-type well diffusion layer and collector diffusion layer as P-type diffusion layers, a cathode diffusion layer and collector contact diffusion layer as N-type diffusion layers, a source / drain diffusion layer and base Poly-Si diffusion layer as N-type diffusion layers, and a source / drain diffusion layer and base Poly-Si diffusion layer as P-type diffusion layers) are simultaneously formed in two or more regions among a light-receiving element region, CMOS element region and bipolar transistor element region of a semiconductor substrate or of an epitaxial layer over the semiconductor substrate.

Owner:FUJITSU MICROELECTRONICS LTD

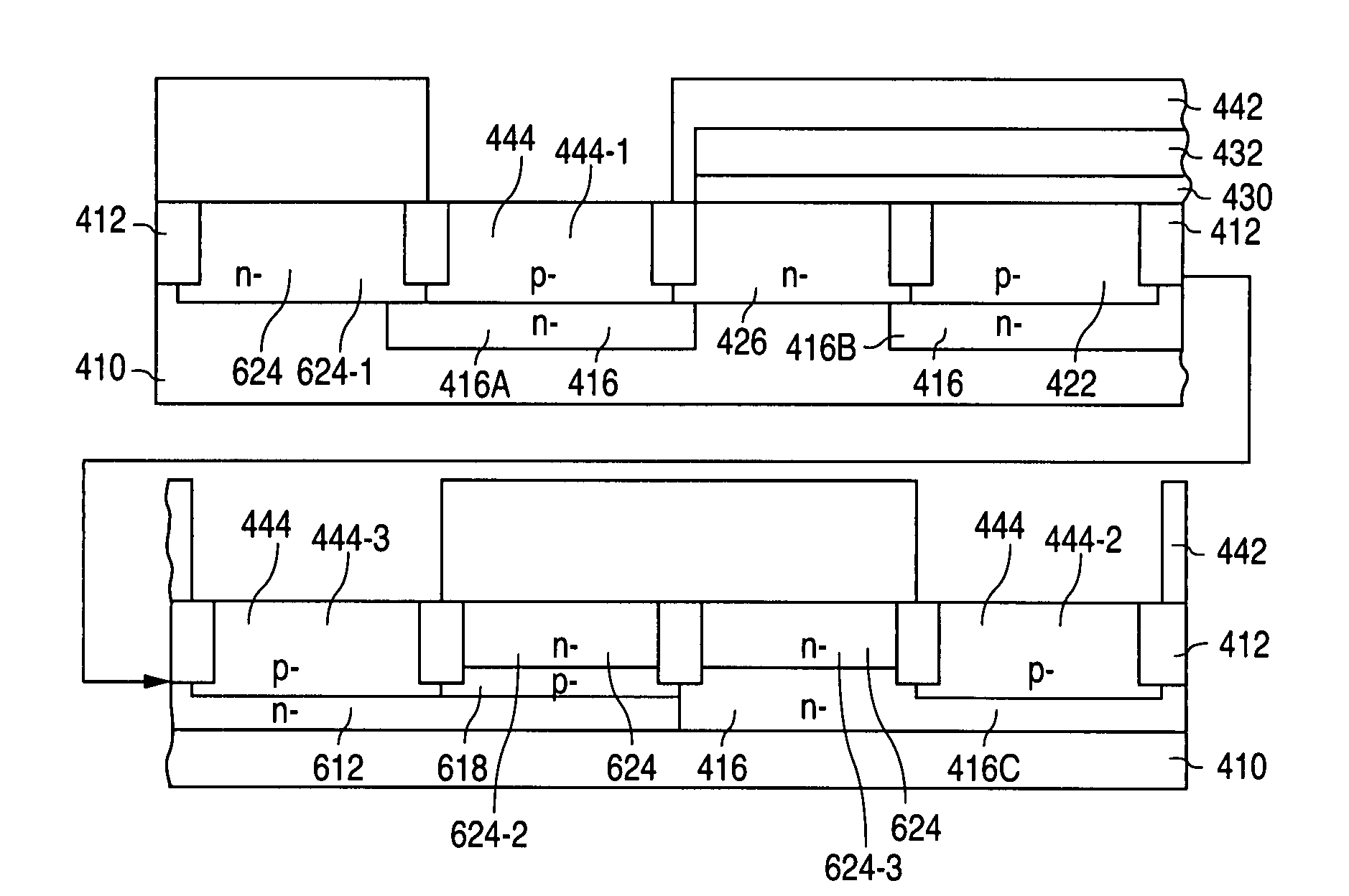

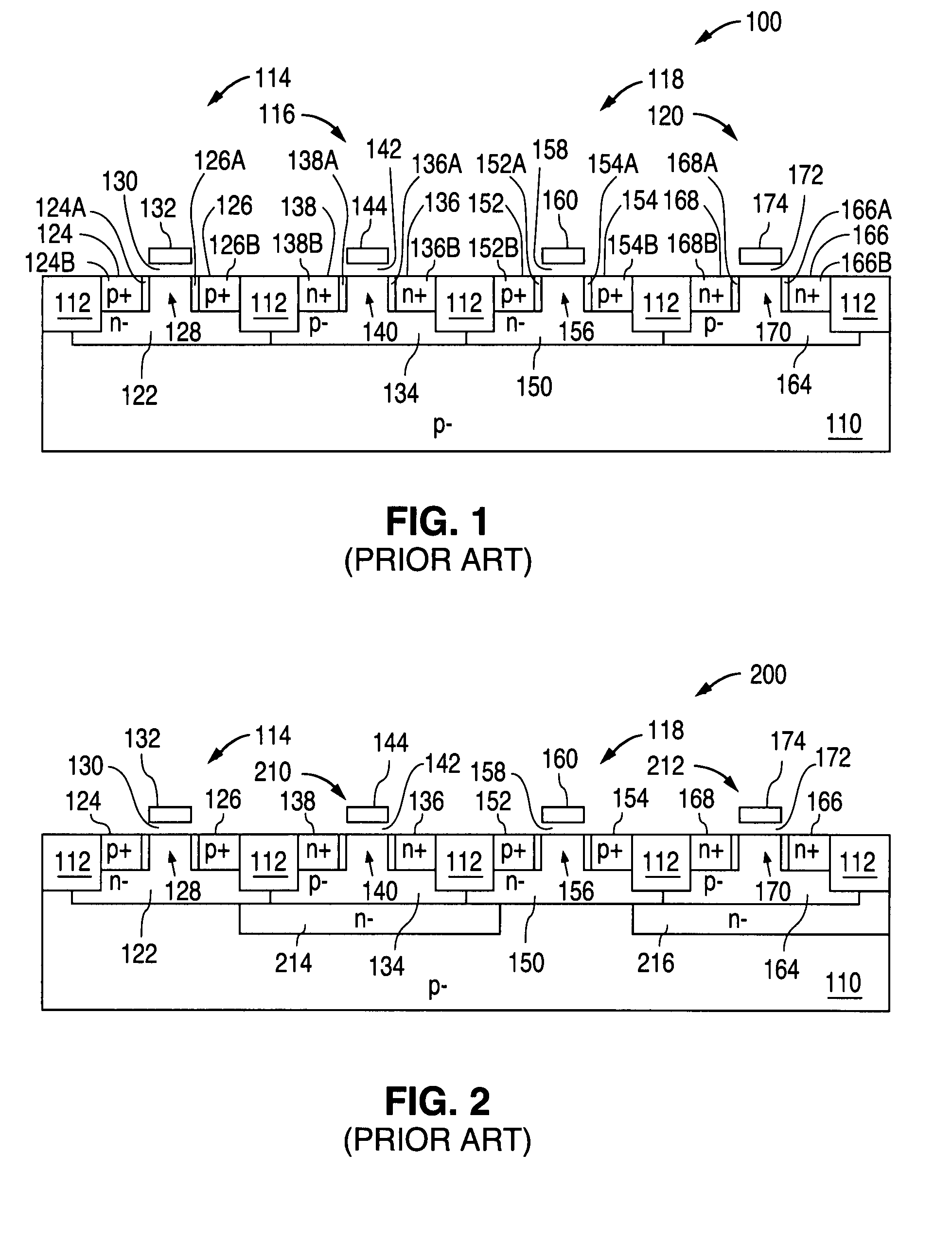

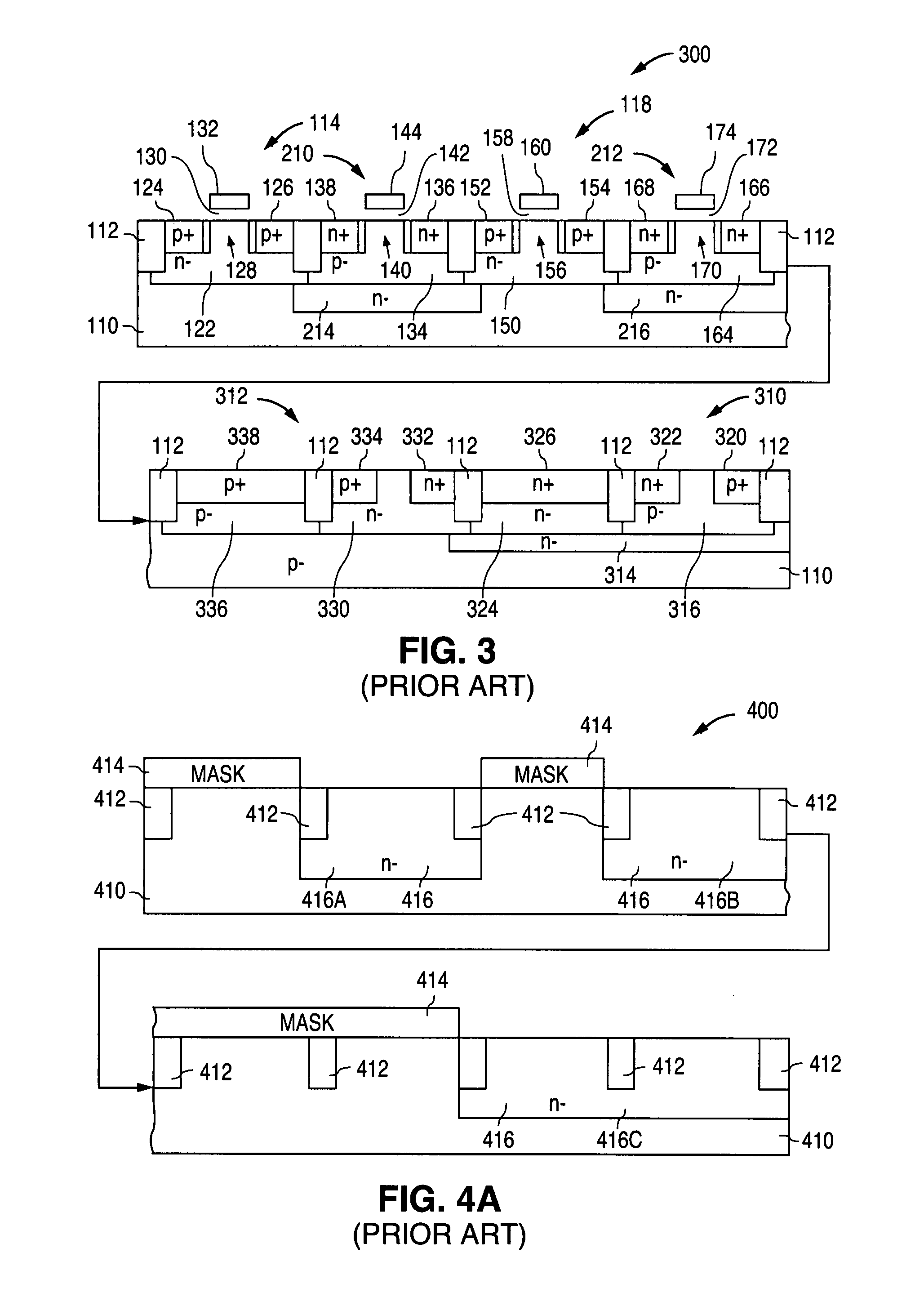

Method of forming npn and pnp bipolar transistors in a CMOS process flow that allows the collectors of the bipolar transistors to be biased differently than the substrate material

NPN and PNP bipolar junction transistors are formed in a semiconductor substrate material in a double polysilicon CMOS process flow in a manner that allows the collectors of both of the npn and pnp bipolar transistors to be biased differently than the bias that is placed on the semiconductor substrate material.

Owner:NAT SEMICON CORP

Semiconductor memory and manufacture method thereof

ActiveCN106298677ALow working voltageIncrease reaction rateSolid-state devicesSemiconductor/solid-state device manufacturingMiniaturizationEngineering

Provided is a semiconductor memory and a manufacture method thereof. The method comprises that a semiconductor substrate is provided, a tunneling oxidation layer is formed on the semiconductor substrate, a selecting grid and a floating grid are formed at the surface of the tunneling oxidation layer, a control grid is formed at the surface of the floating grid, and an inter-grid dielectric layer is formed between the floating grid and the control grid. According to the invention, a double-polysilicon-layer grid structure formed by the floating grid and the control grid can reduce the working voltage of the memory greatly, accelerate response of the memory and improve the data storage capability of the memory, and is conducive to miniaturization of devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP

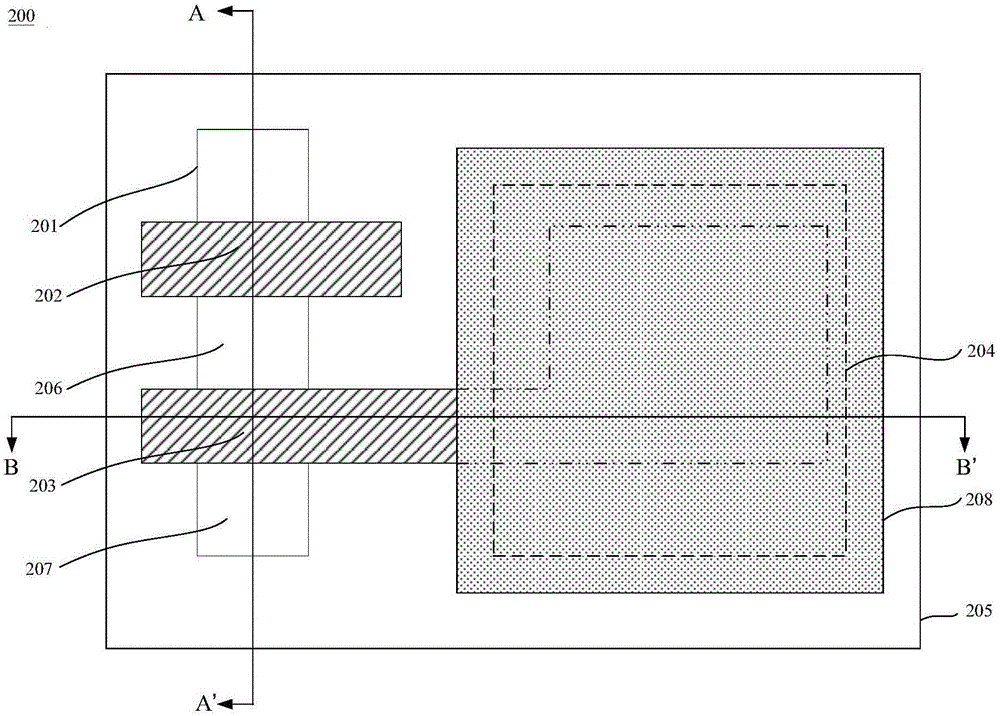

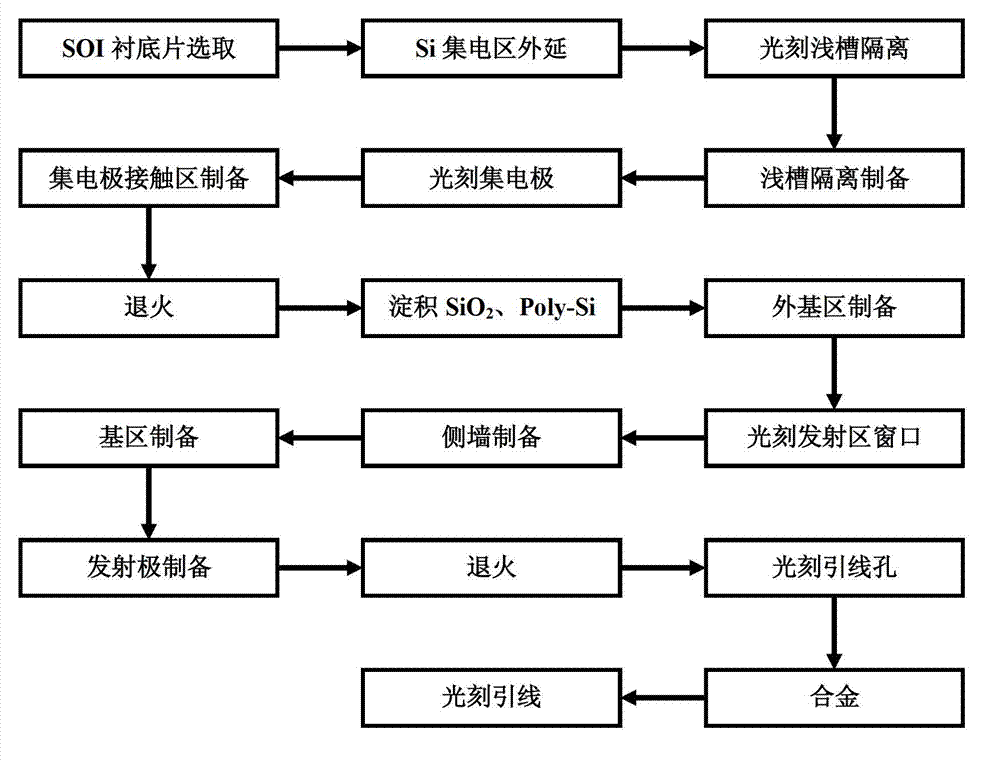

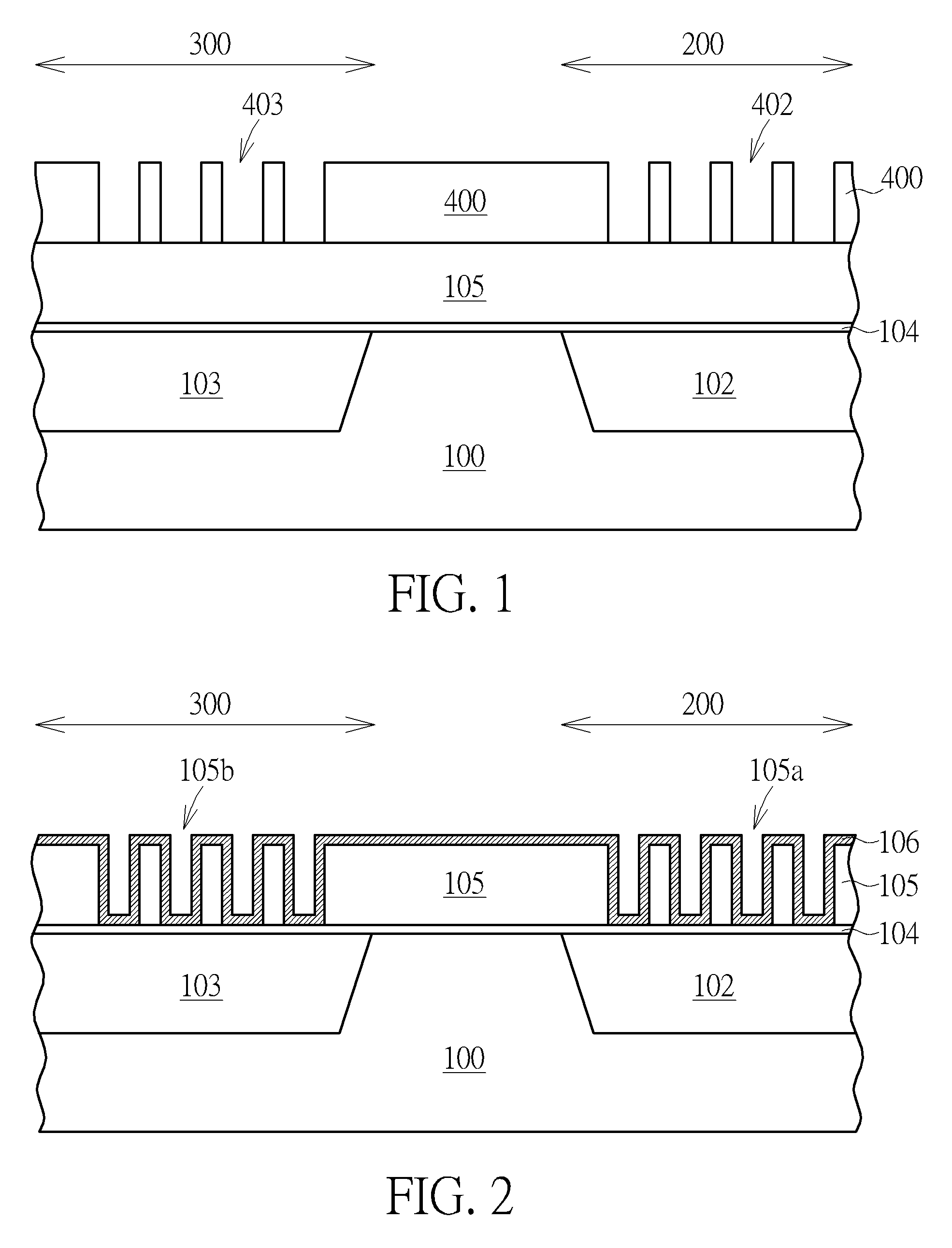

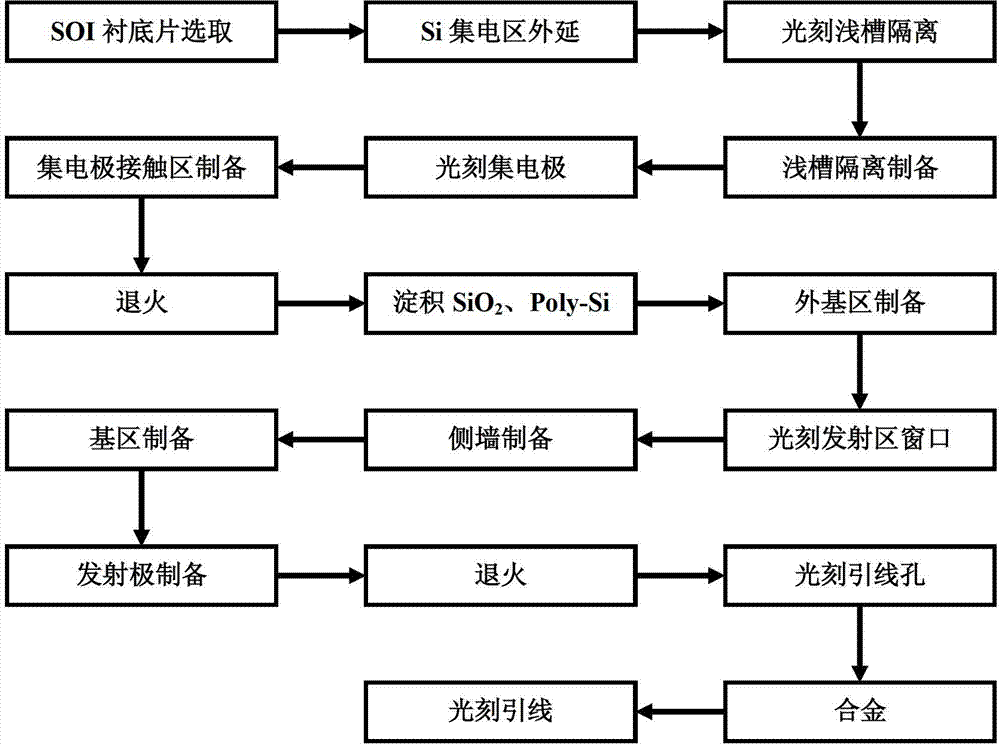

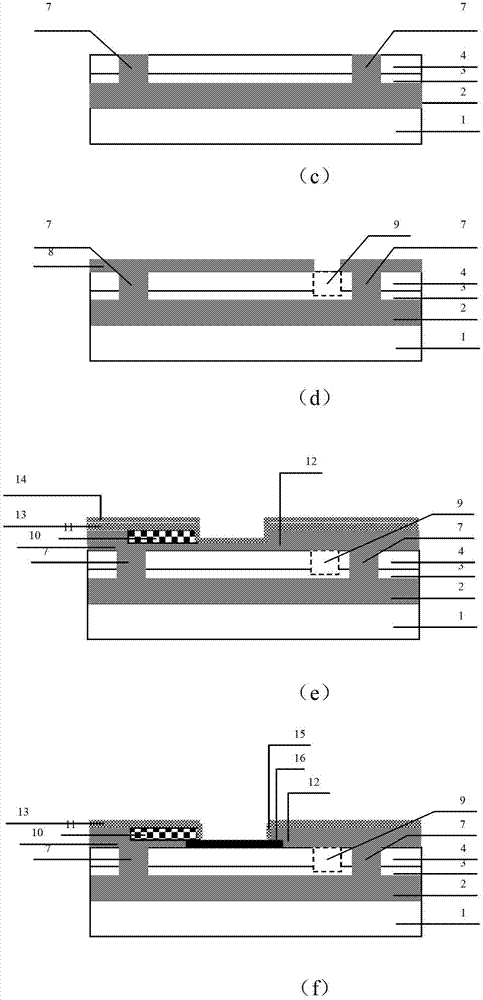

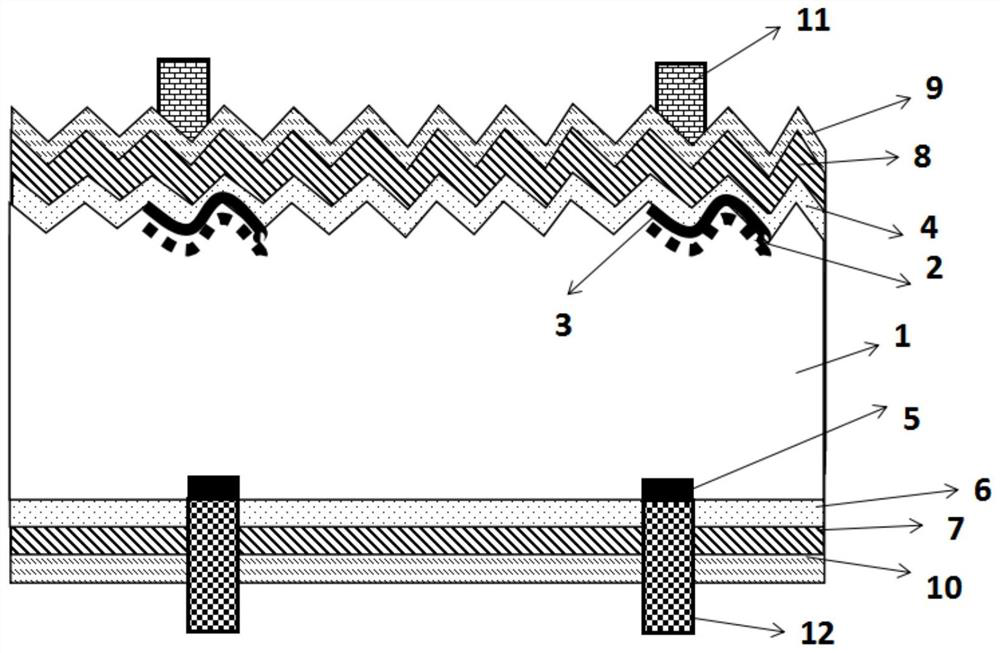

Double-polysilicon SOI (Silicon On Insulator) SiGe HBT (Heterojunction Bipolar Transistor) integrated device based on self-aligned technology and preparation method thereof

InactiveCN102738178AImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingPhosphoniumEngineering

The invention is suitable for the technical field of semiconductor integrated circuit and provides a double-polysilicon SOI (Silicon On Insulator) SiGe HBT (Heterojunction Bipolar Transistor) integrated device based on self-aligned technology and a preparation method thereof. The preparation method comprises the following steps: growing N-type Si epitaxy on an SOI substrate; photoetching a shallow slot isolation region; preparing shallow slot isolation; etching and injecting phosphonium ions to form a collector contact region; depositing SiO2, P-Poly-Si, SiO2 and nitride in sequence; carrying out dry etching to form a nitride side wall; carrying out wet etching to form a base region window; selectively growing a SiGe base region; depositing N-type Poly-Si; then removing Poly-Si outside an emitter to form an HBT (Heterojunction Bipolar Transistor); and finally photoetching an emitter region, the base region and a collector region pin hole, metalizing, photoetching a lead wire to form an HBT integrated circuit in which the thickness of the base region is 20-60nm. The technique provided by the invention is compatible with the existing CMOS (Complementary Metal-Oxide-Semiconductor) integrated circuit processing technology, and can prepare the integrated circuit of a BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor) device based on SOI under the condition of little capital and equipment investment so that the performance of the existing analog and digital-analog hybrid integrated circuit is greatly improved.

Owner:XIDIAN UNIV

Double polysilicon bipolar transistor and method of manufacture therefor

InactiveUS6936519B2Easy to operateSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

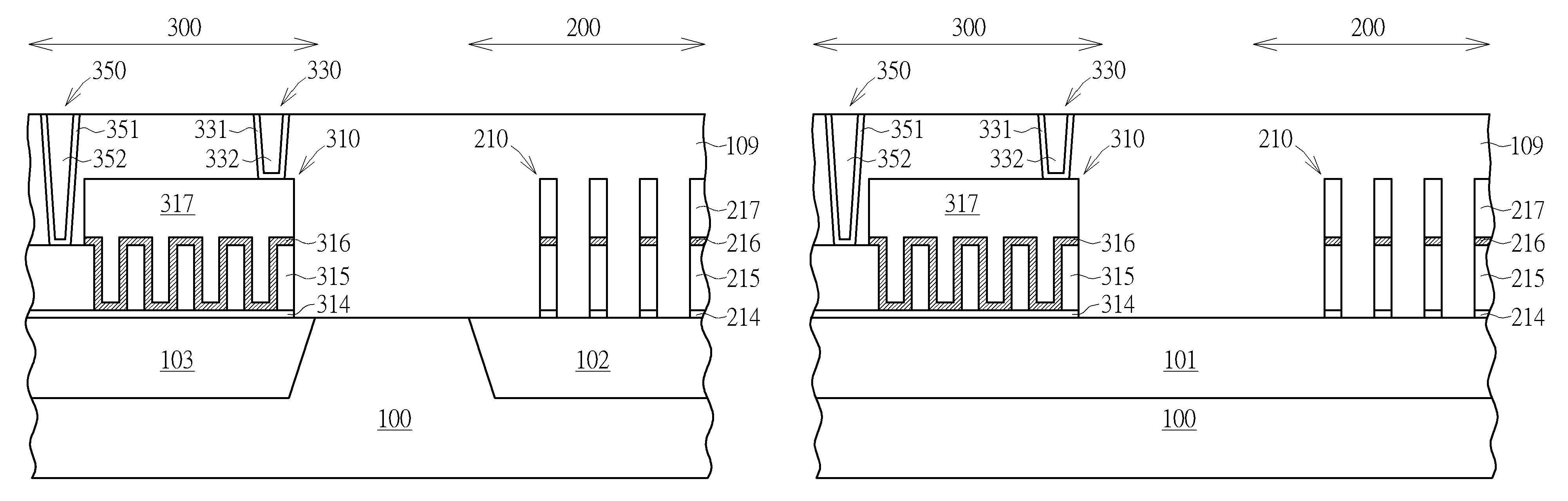

Semiconductor integrated device including capacitor and memory cell and method of forming the same

A semiconductor integrated device and a method of forming the same, the semiconductor integrated device includes a substrate, at least one shallow trench isolation, a memory cell device and a poly-insulator-poly capacitor. A capacitor region and a memory cell region are defined on the substrate. The at least one shallow trench isolation is formed in the substrate. The memory cell device is disposed on the at least one shallow trench isolation in the memory cell region and includes a double polysilicon gate. The poly-insulator-poly capacitor is disposed on the at least one shallow trench isolation in the capacitor region, wherein the poly-insulator-poly capacitor directly contacts the at least one shallow trench isolation.

Owner:UNITED MICROELECTRONICS CORP

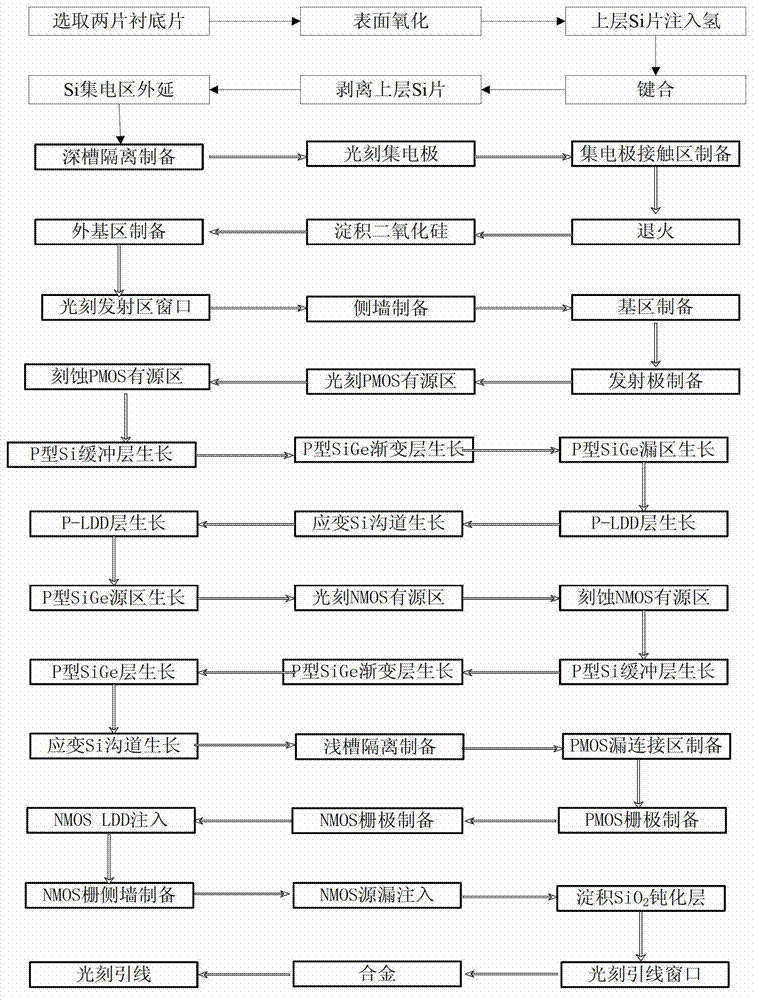

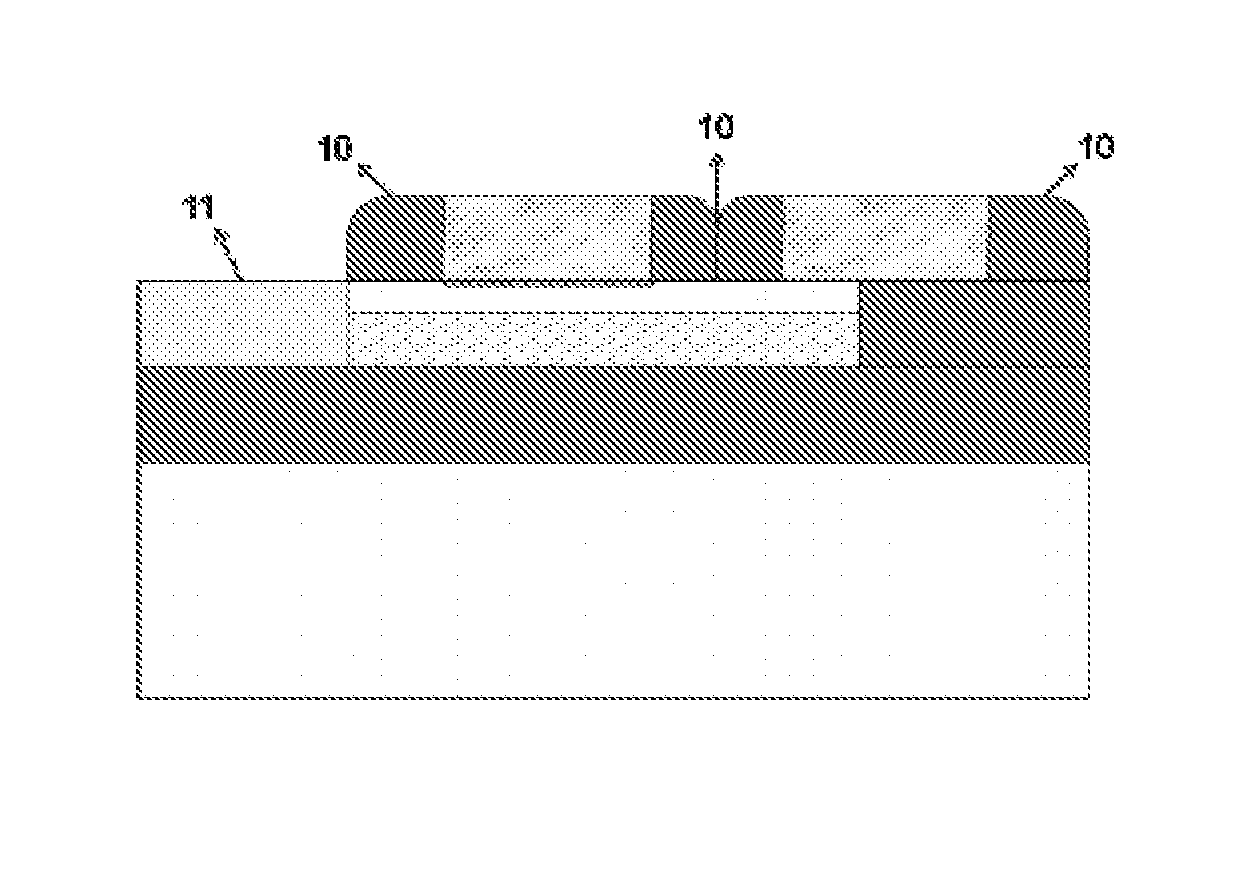

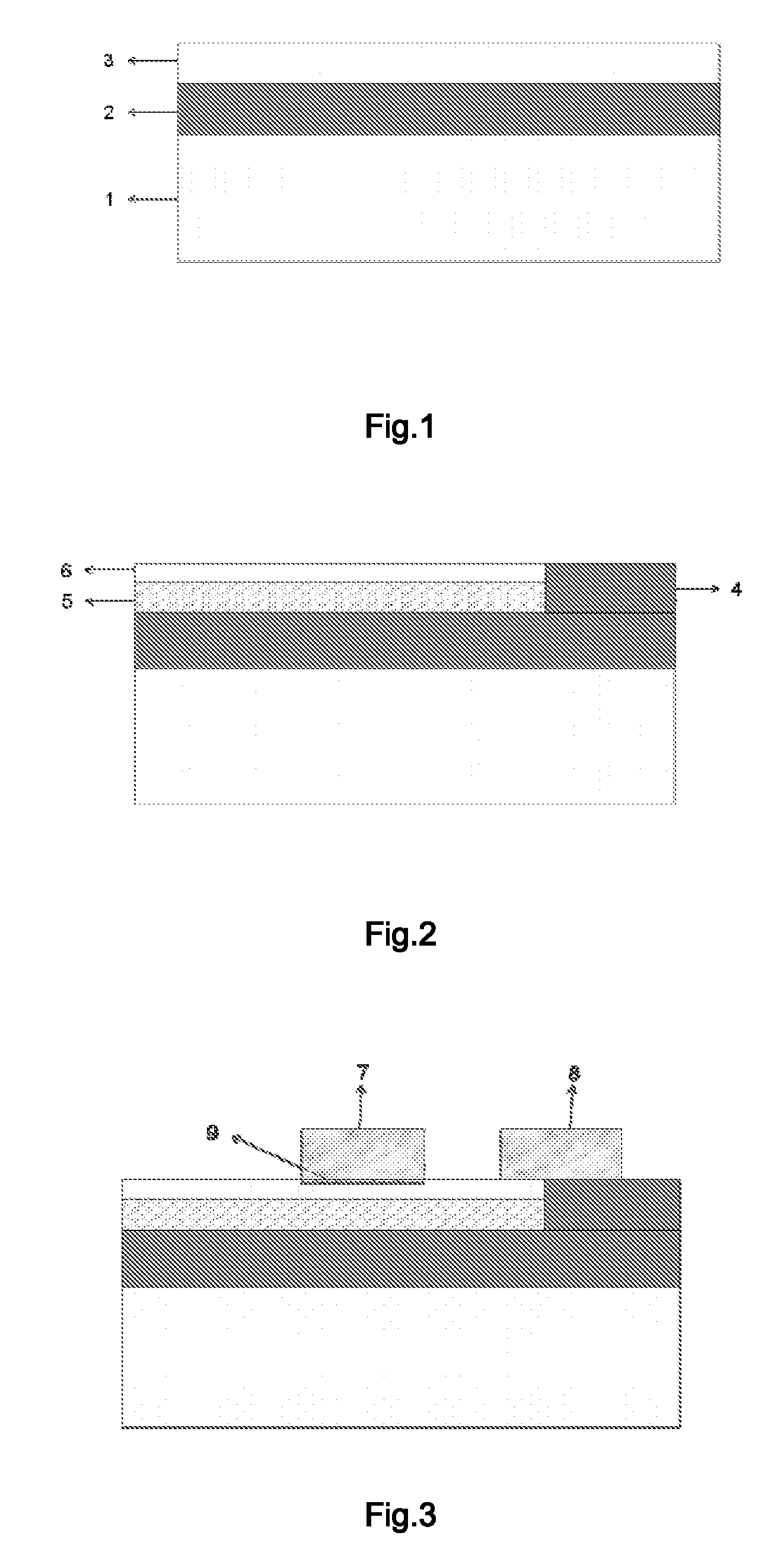

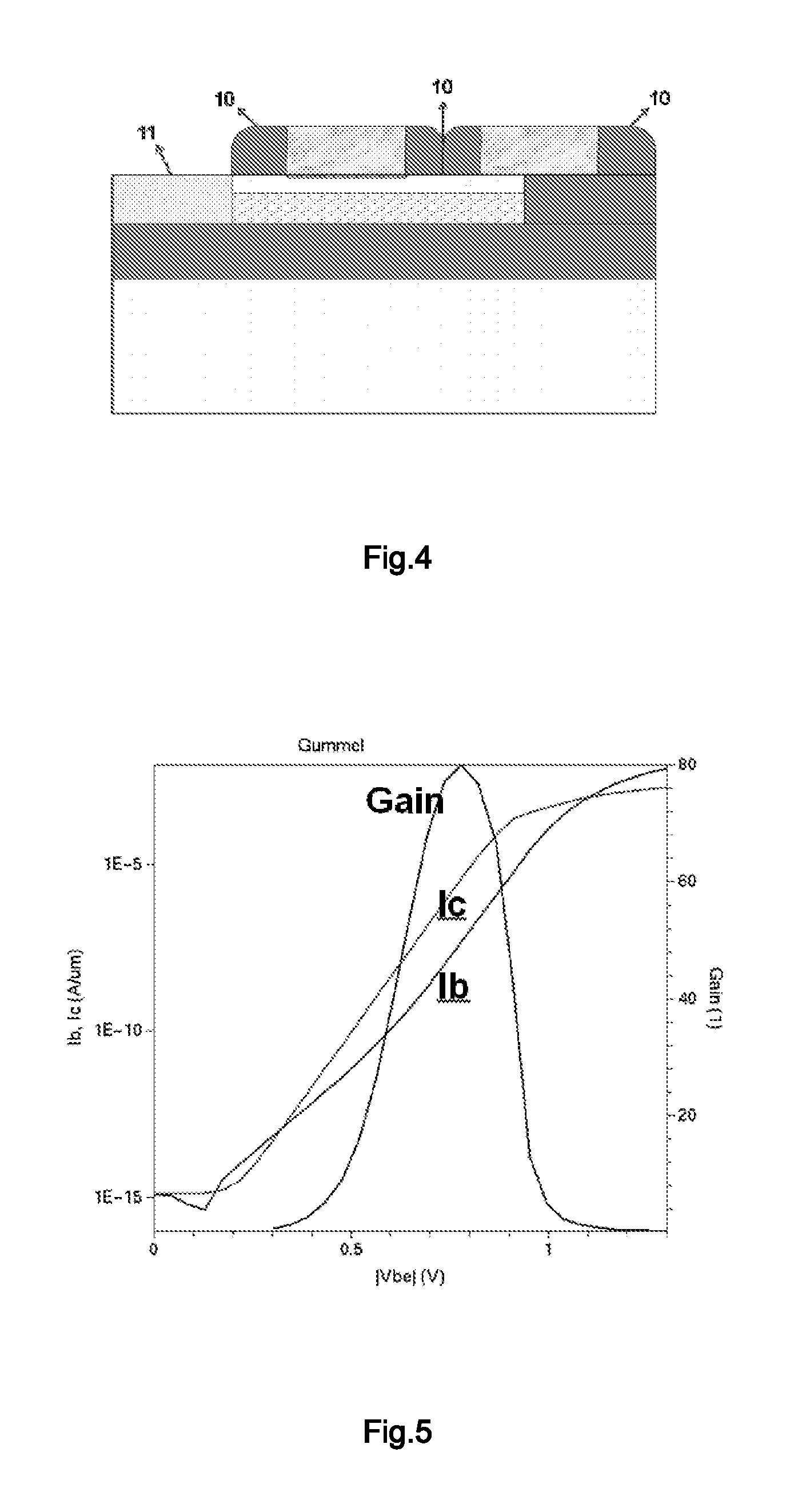

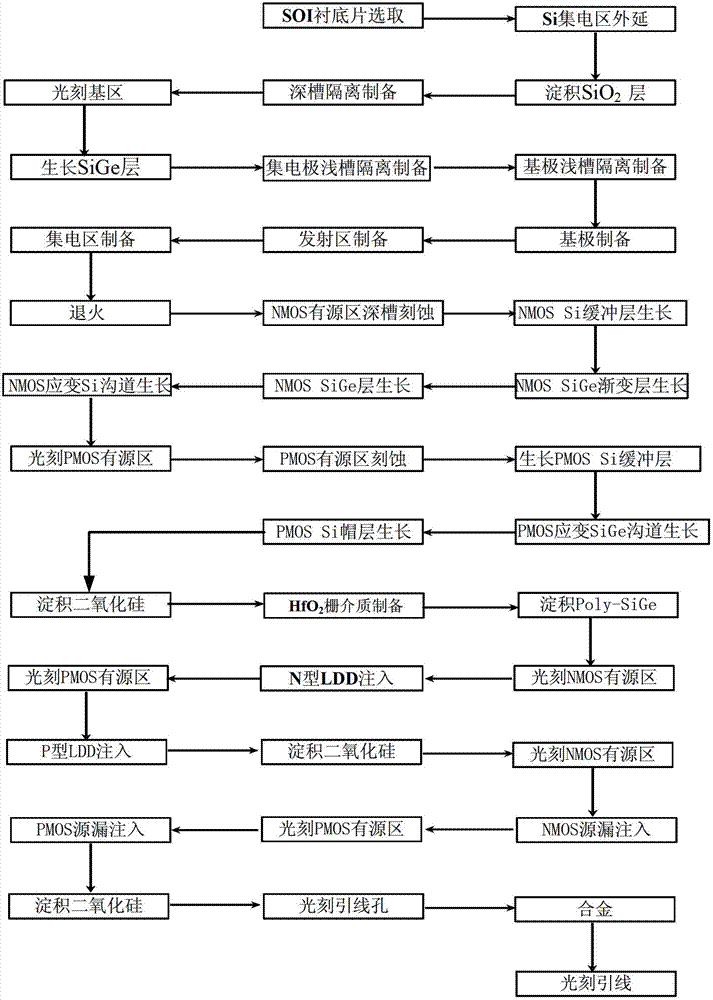

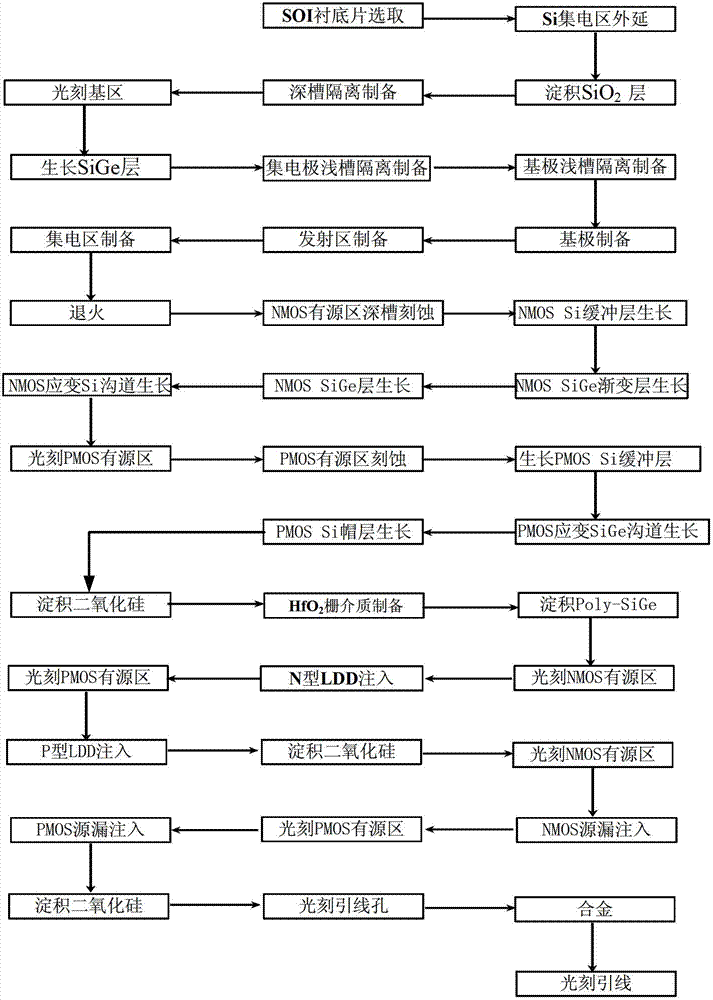

Vertical-channel mixed-lattice-strain BiCMOS (bipolar complementary metal oxide semiconductor) integrated device and preparation method

InactiveCN102738154AImprove performanceHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricP channel

The invention discloses a vertical-channel mixed-lattice-strain BiCMOS integrated device and a preparation method. The preparation method comprises preparing an SOI (silicon on insulator) substrate, epitaxially growing a Si layer on the substrate as a collector region, preparing deep trench isolation, and preparing a double-polysilicon SiGe HBT (heterojunction bipolar transistor) device on the active region of the bipolar device by self-alignment process; etching an active region of a PMOS (p-channel metal oxide semiconductor) device by lithography, continuously growing seven material layers on the active region, andpreparing a drain and a gate to obtain the PMOS device; etching a trench in the active region of an NMOS (n-channel metal oxide semiconductor) device by lithography, continuously growing four material layers on the active region, preparing a gate dielectric layer and gate polysilicon to obtain the NMOS device, etching lead holes by lithography, alloying, and etching leads by lithography to obtain the vertical-channel mixed-lattice-strain BiCMOS integrated device and circuit with a CMOS conductive channel of 22 to 45nm. The preparation method provided by the invention can prepare the performance-enhanced vertical-channel mixed-lattice-strain BiCMOS integrated device at 600 to 800 DEG C by fully utilizing the characteristics of mobility anisotropy of the tensile strained Si material.

Owner:XIDIAN UNIV

Vertical SOI bipolar junction transistor and manufacturing method thereof

InactiveUS8629029B2Highly integratedImprove compatibilitySemiconductor/solid-state device manufacturingSemiconductor devicesSoi cmosSoi substrate

The present invention discloses a vertical SOI bipolar junction transistor and a manufacturing method thereof. The bipolar junction transistor includes an SOI substrate from down to up including a body region, a buried oxide layer and a top silicon film; an active region located in the top silicon film formed by STI process; a collector region located in the active region deep close to the buried oxide layer formed by ion implantation; a base region located in the active region deep close to the top silicon film formed by ion implantation; an emitter and a base electrode both located over the base region; a side-wall spacer located around the emitter and the base electrode. The present invention utilizing a simple double poly silicon technology not only can improve the performance of the transistor, but also can reduce the area of the active region in order to increase the integration density. Furthermore, the present invention utilizes side-wall spacer process to improve the compatibility of SOI BJT and SOI CMOS, which simplifies the SOI BiCMOS process and thus reduce the cost.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

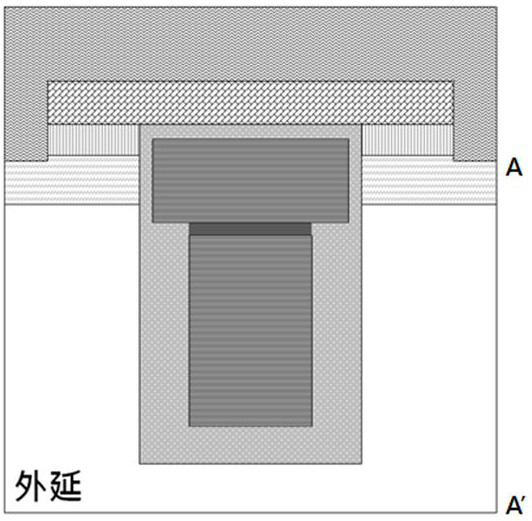

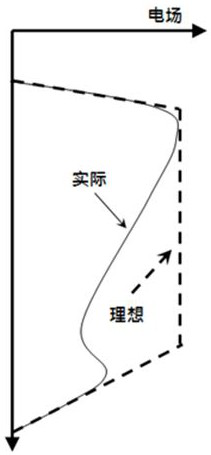

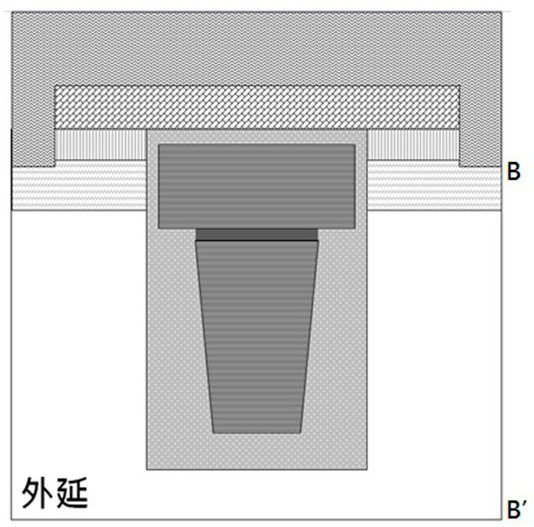

Oblique oxygen manufacturing method of shielding gate groove type MOS transistor

ActiveCN113571421AImprove controllabilitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryGate oxide

The invention relates to the technical field of semiconductors, and particularly discloses an oblique oxygen manufacturing method of a shielding gate groove type MOS transistor. The method comprises the following steps of: providing an epitaxial layer; performing photoetching on the epitaxial layer to obtain a groove; growing an oxide layer along the inner side of the groove; depositing polycrystalline silicon for the first time in the groove after growing the oxide layer; performing ion etching on the first polycrystalline silicon to obtain a triangular polycrystalline silicon side wall residual layer along the side wall of the groove; forming a total oxide layer on the triangular polycrystalline silicon side wall residual layer; depositing secondary polycrystalline silicon on the total oxide layer and performing etching to obtain source polycrystalline silicon; etching the total oxide layer until the total oxide layer is flush with the source polycrystalline silicon; forming an IPO layer on the source polysilicon, and forming a gate oxide layer on the total oxide layer; and depositing polycrystalline silicon for the third time on the IPO layer, and etching to obtain a source electrode and gate electrode double polycrystalline silicon structure of a shielding gate groove. The oblique oxygen manufacturing method of the shielding gate groove type MOS transistor is good in controllability and can be achieved without adding too many process steps.

Owner:江苏应能微电子股份有限公司

Method for forming a polycide gate and structure of the same

InactiveUS20050156252A1Semiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsPhotoresist

The method of forming a polycide gate includes forming a pad oxide layer on a substrate. A first conductive layer is formed on the pad oxide layer. Subsequently, a first ion implantation into the first conductive layer is next performed to form deep implantation region of polysilicon. Successively, a second ion implantation into the first conductive layer is performed to form shallow implantation region of polysilicon, wherein the second ion type is the same as the first ion type. A second conductive layer formed on the first conductive layer. A further patterned photoresist layer is formed on the second conductive layer. Next, a dry etching process one time by way of using the patterned photoresist layer as an etching mask is performed to etch through in turn the second conductive layer, the first conductive layer and the pad oxide layer until forming a gate with double polysilicon implantation, thereby forming a polycide gate. Finally, the photoresist layer is then removed.

Owner:UNITED MICROELECTRONICS CORP

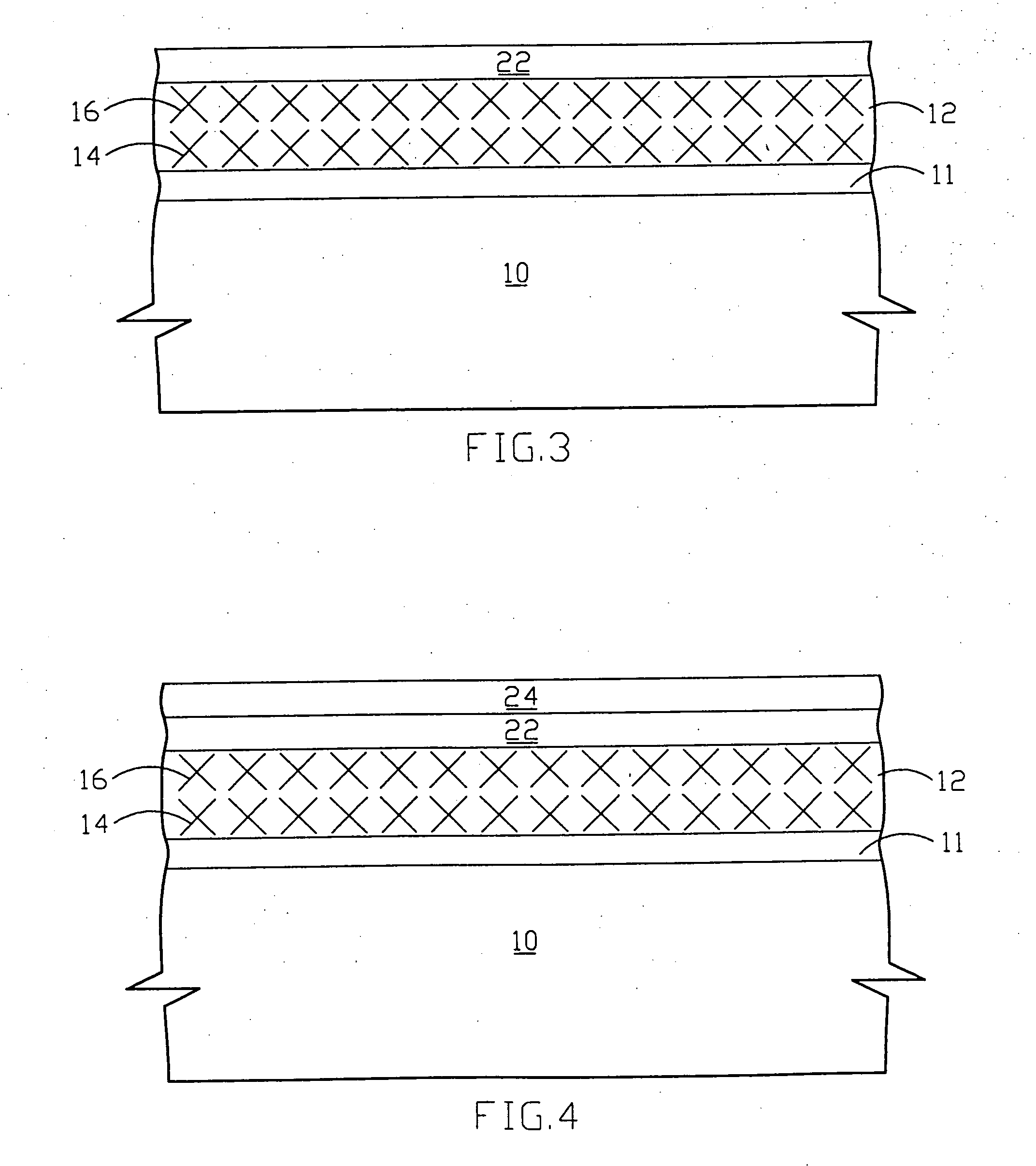

Formation method of enhanced field effect transistor

The invention provides a method for manufacturing a polycrystalline silicon channel SOI MOSFET under a bulk silicon CMOS process, which is suitable for double polycrystalline silicon processes such asan EEPROM process. The polycrystalline silicon channel SOI MOSFET has the SOI MOSFET characteristics such as small source-drain capacitance and easiness in forming isolation, and can be applied to the design of switching devices and the like.

Owner:南京飞芯电子科技有限公司

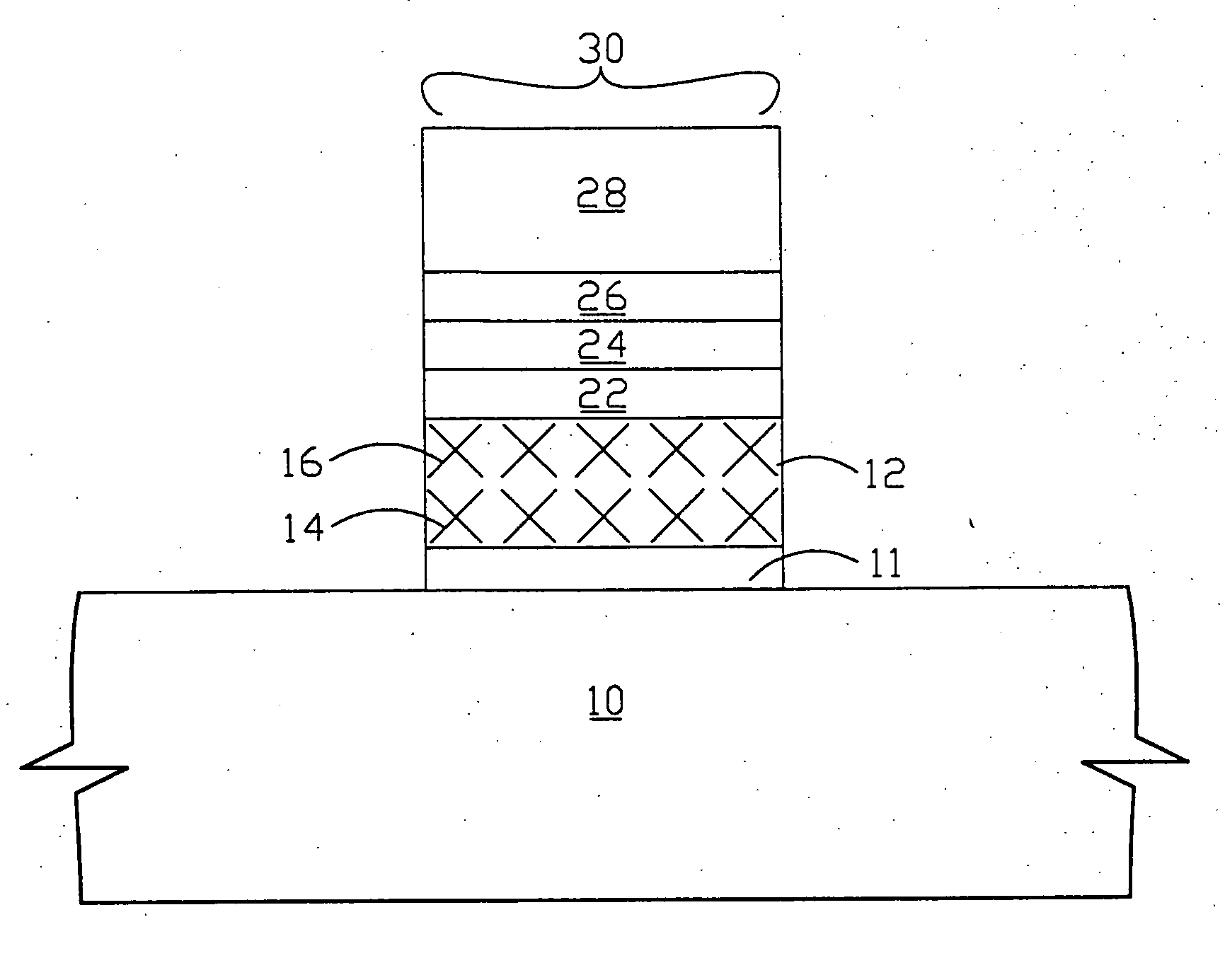

Double polysilicon bipolar transistor

InactiveUS20050170580A1Easy to operateSmall sizeSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringDielectric layer

A bipolar transistor, with a substrate having a collector region and a base structure provided thereon. An emitter structure is formed over the base structure and an extrinsic base structure is formed over the base structure and over the collector region beside and spaced from the emitter structure. A dielectric layer is deposited over the substrate and connections are formed to the extrinsic base structure, the emitter structure and the collector region.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

A kind of double polycrystalline soi SiGe HBT integrated device and preparation method based on self-alignment process

InactiveCN102738178BImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingPhosphoniumIntegrated circuit

The invention is suitable for the technical field of semiconductor integrated circuit and provides a double-polysilicon SOI (Silicon On Insulator) SiGe HBT (Heterojunction Bipolar Transistor) integrated device based on self-aligned technology and a preparation method thereof. The preparation method comprises the following steps: growing N-type Si epitaxy on an SOI substrate; photoetching a shallow slot isolation region; preparing shallow slot isolation; etching and injecting phosphonium ions to form a collector contact region; depositing SiO2, P-Poly-Si, SiO2 and nitride in sequence; carrying out dry etching to form a nitride side wall; carrying out wet etching to form a base region window; selectively growing a SiGe base region; depositing N-type Poly-Si; then removing Poly-Si outside an emitter to form an HBT (Heterojunction Bipolar Transistor); and finally photoetching an emitter region, the base region and a collector region pin hole, metalizing, photoetching a lead wire to form an HBT integrated circuit in which the thickness of the base region is 20-60nm. The technique provided by the invention is compatible with the existing CMOS (Complementary Metal-Oxide-Semiconductor) integrated circuit processing technology, and can prepare the integrated circuit of a BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor) device based on SOI under the condition of little capital and equipment investment so that the performance of the existing analog and digital-analog hybrid integrated circuit is greatly improved.

Owner:XIDIAN UNIV

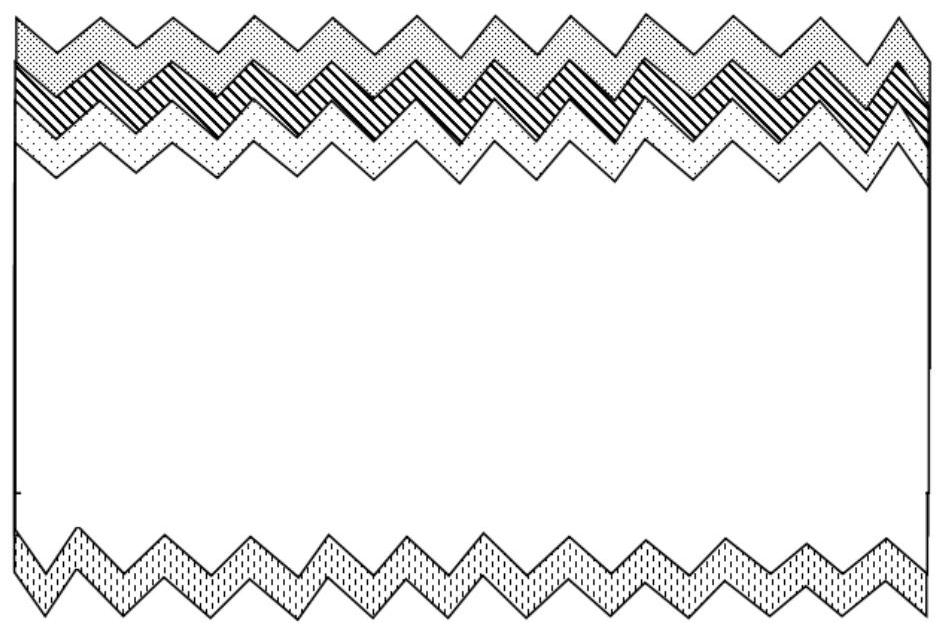

A kind of double-sided selective emitter high-efficiency crystalline silicon cell and preparation method thereof

ActiveCN111524983BRaise VocAvoid the disadvantage of high surface concentrationFinal product manufacturePhotovoltaic energy generationPhotovoltaic industryEtching

The invention belongs to the field of solar photovoltaic industry, and specifically provides a double-sided selective emitter high-efficiency crystalline silicon battery and a preparation method thereof; the double-sided selective emitter structure is adopted, and the boron-doped heavily doped region is aluminum oxide Instead of silicon oxide as the polysilicon structure of the tunneling layer, it can reach >1E20atom / cm 3 The constant surface concentration improves the fill factor (FF), while the light expansion area is pure boron doping, and the boron doping process of re-expansion and light expansion can be realized in one step, which simplifies the process. Silicon oxide is used as the tunneling layer for the phosphorous-doped region, the heavily doped region is a double-layer polysilicon (poly) structure with high surface concentration, which improves the metallization contact, and the lightly expanded region is a single-layer lightly doped poly structure, thereby improving the open circuit Voltage (Voc). The formation of double-sided selective emitter effectively utilizes the method of mask etching. This structure can effectively improve battery efficiency and is suitable for mass production.

Owner:CHANGZHOU UNIV +1

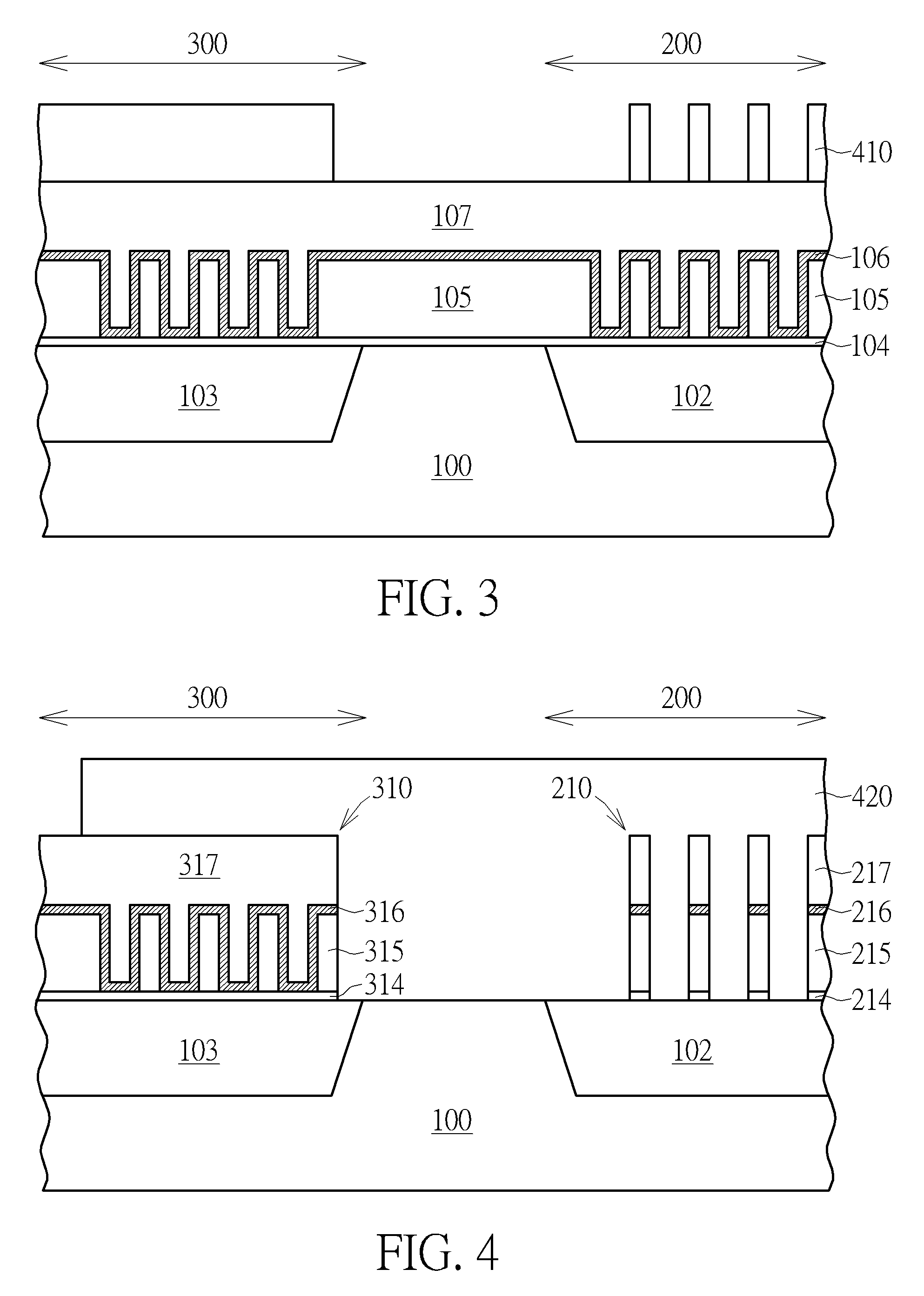

Double-polysilicon planar SOI (silicon on insulator) BiCMOS (bipolar complementary metal oxide semiconductor) integrated device and preparation method

InactiveCN102738172AImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingP channelIntegrated circuit

The invention discloses a double-polysilicon planar SOI BiCMOS integrated device and a preparation method. The preparation method growing N-Si on a SOI substrate as the collector region of a bipolar device, etching a base region by lithography, growing P-SiGe, i-Si and i-Poly-Si on the base region, preparing deep trench isolation, and preparing an emitter, a base and a collector to obtain a SiGe HBT (heterojunction bipolar transistor) device; etching a trench on the active region of an NMOS (n-channel metal oxide semiconductor) device by lithography, and growing four material layers in the trench; etching a trench on the active region of a PMOS (p-channel metal oxide semiconductor) device, growing three material layers in the trench, and preparing a drain and a gate on the active region of MOS (metal oxide semiconductor) to obtain an MOS device; and etching leads by lithography to obtain the double-polysilicon planar SOI BiCMOS integrated device and circuit. According to the invention, the double-polysilicon planar SOI BiCMOS integrated circuit prepared by the method is enhanced in performance by fully utilizing the characteristics that the electron mobility of a tensile strained Si material is higher than that of a bulk Si material and that the hole mobility of a compressive strained SiGe material is higher than that of the bulk Si material.

Owner:XIDIAN UNIV

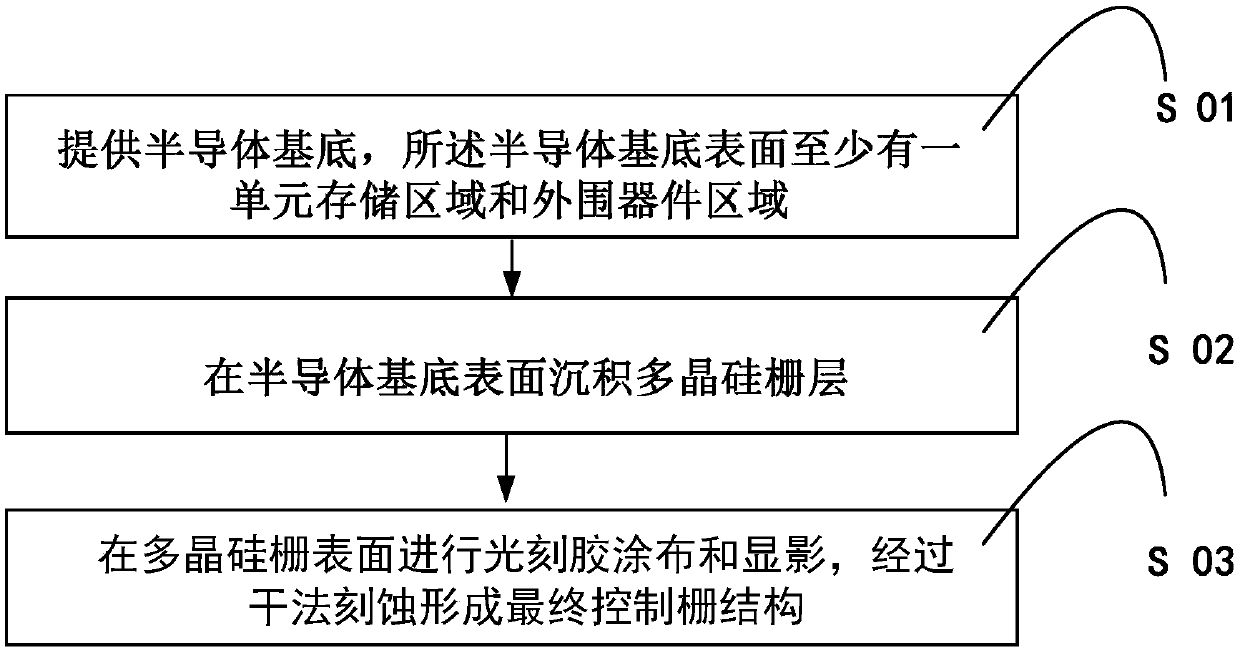

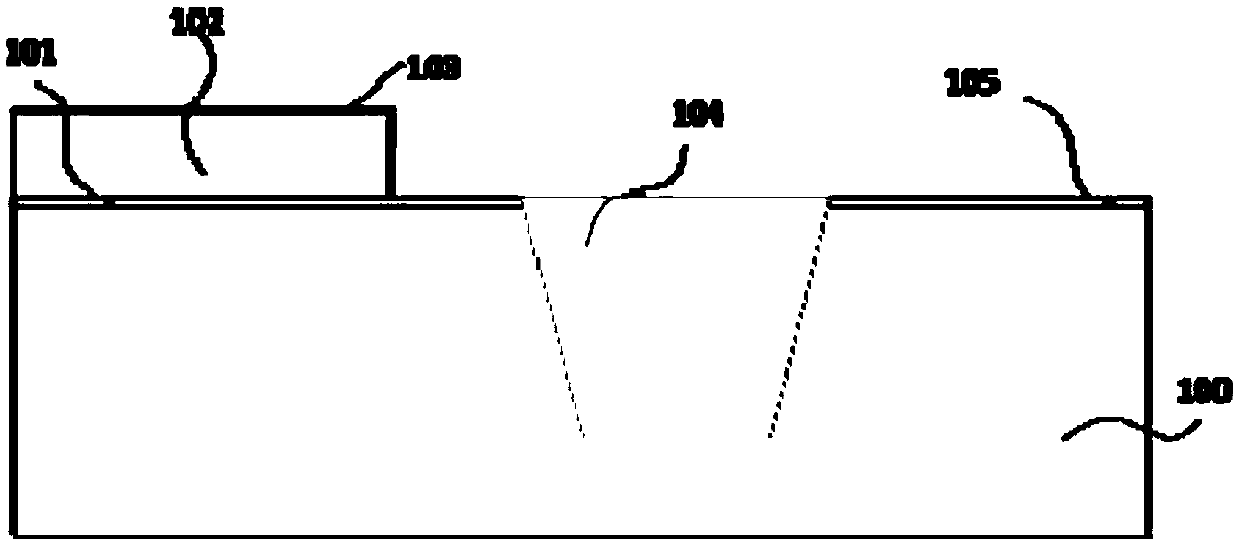

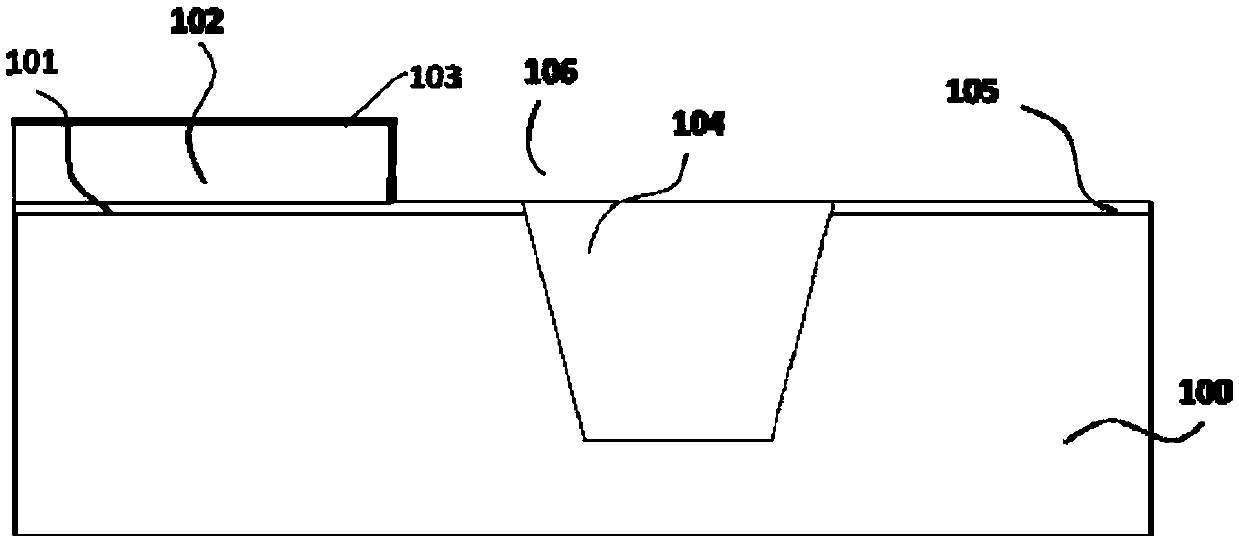

A process method for increasing ild filling window with adjustable control grid

ActiveCN106328656BReduce aspect ratioThinning the Control Gate ThicknessSolid-state devicesSemiconductor devicesEngineeringSilicon oxide

A process method for increasing an ILD filling window with an adjustable control gate, which includes: providing a base with a unit storage area and a peripheral device area; depositing a first polysilicon gate layer on the surface of the base; Grow a silicon oxide barrier layer; apply photoresist and develop on the surface of the silicon oxide barrier layer to expose the peripheral device area, and only etch and remove the silicon oxide barrier layer in the peripheral device area; the silicon oxide barrier layer in the cell storage area Deposit a second polysilicon gate layer on the surface of the first polysilicon gate layer in the peripheral device area; perform photoresist coating and development on the surface of the second polysilicon gate layer to expose the cell storage area, and etch to remove only the cell The second polysilicon gate layer in the storage area; etch to remove the remaining silicon oxide barrier layer; perform photoresist coating and development on the surface of the polysilicon gate in the unit storage area and peripheral device area, and dry etch to form the final Double polysilicon gate structure.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A kind of bipolycrystalline planar soi BiCMOS integrated device and its preparation method

InactiveCN102738172BImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingIntegrated circuitHeterojunction bipolar transistor

The invention discloses a double-polysilicon planar SOI BiCMOS integrated device and a preparation method. The preparation method growing N-Si on a SOI substrate as the collector region of a bipolar device, etching a base region by lithography, growing P-SiGe, i-Si and i-Poly-Si on the base region, preparing deep trench isolation, and preparing an emitter, a base and a collector to obtain a SiGe HBT (heterojunction bipolar transistor) device; etching a trench on the active region of an NMOS (n-channel metal oxide semiconductor) device by lithography, and growing four material layers in the trench; etching a trench on the active region of a PMOS (p-channel metal oxide semiconductor) device, growing three material layers in the trench, and preparing a drain and a gate on the active region of MOS (metal oxide semiconductor) to obtain an MOS device; and etching leads by lithography to obtain the double-polysilicon planar SOI BiCMOS integrated device and circuit. According to the invention, the double-polysilicon planar SOI BiCMOS integrated circuit prepared by the method is enhanced in performance by fully utilizing the characteristics that the electron mobility of a tensile strained Si material is higher than that of a bulk Si material and that the hole mobility of a compressive strained SiGe material is higher than that of the bulk Si material.

Owner:XIDIAN UNIV