Patents

Literature

36results about How to "Excellent characteristic frequency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

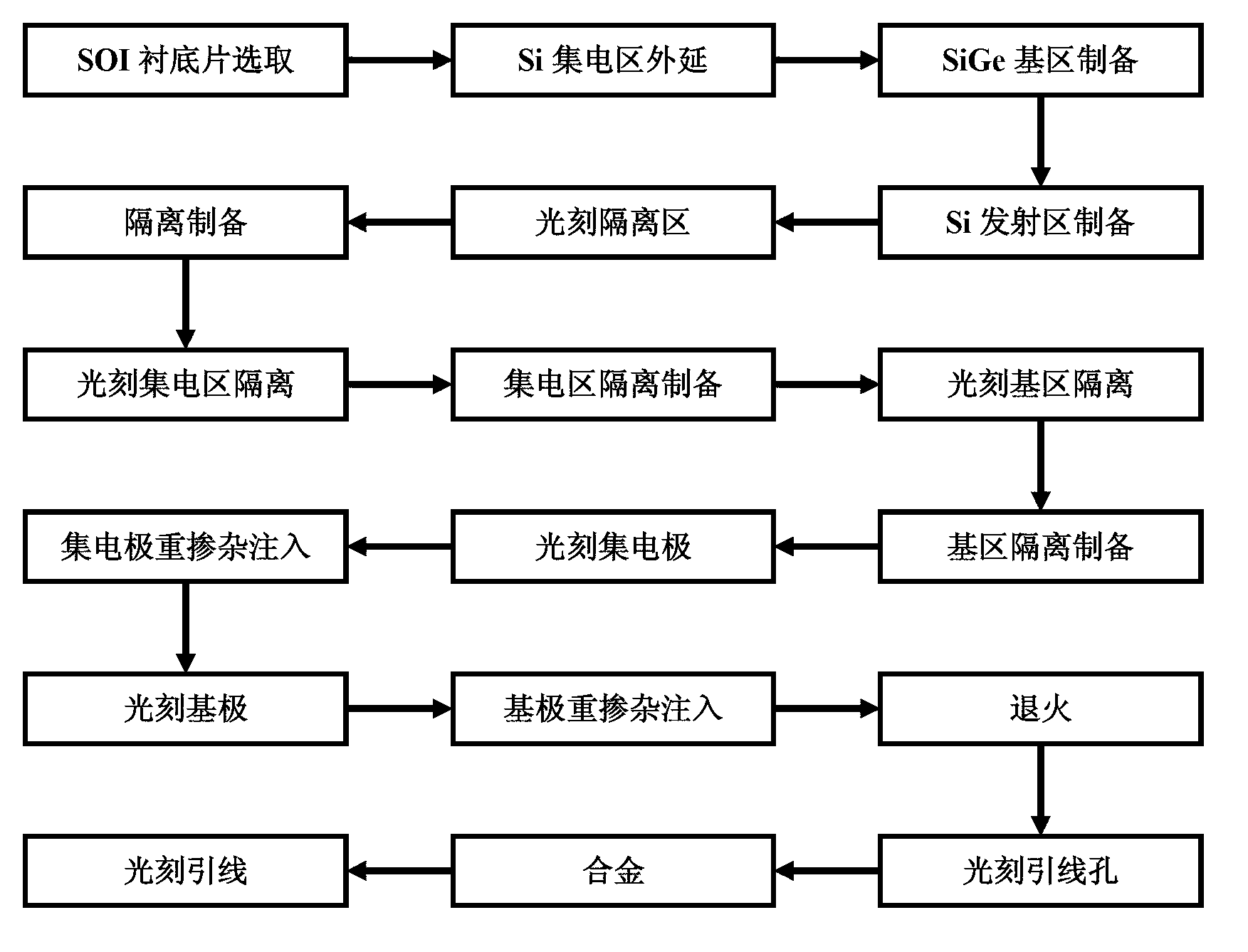

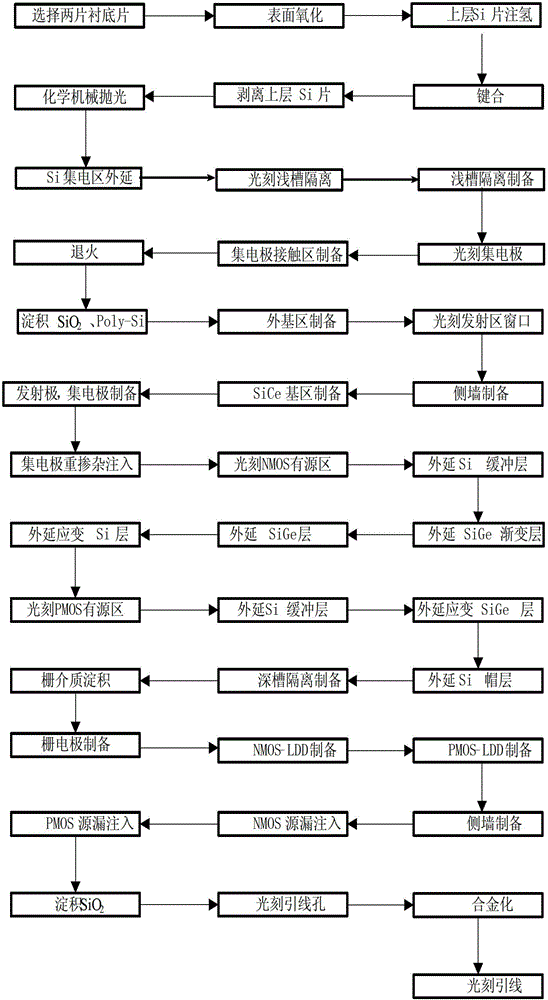

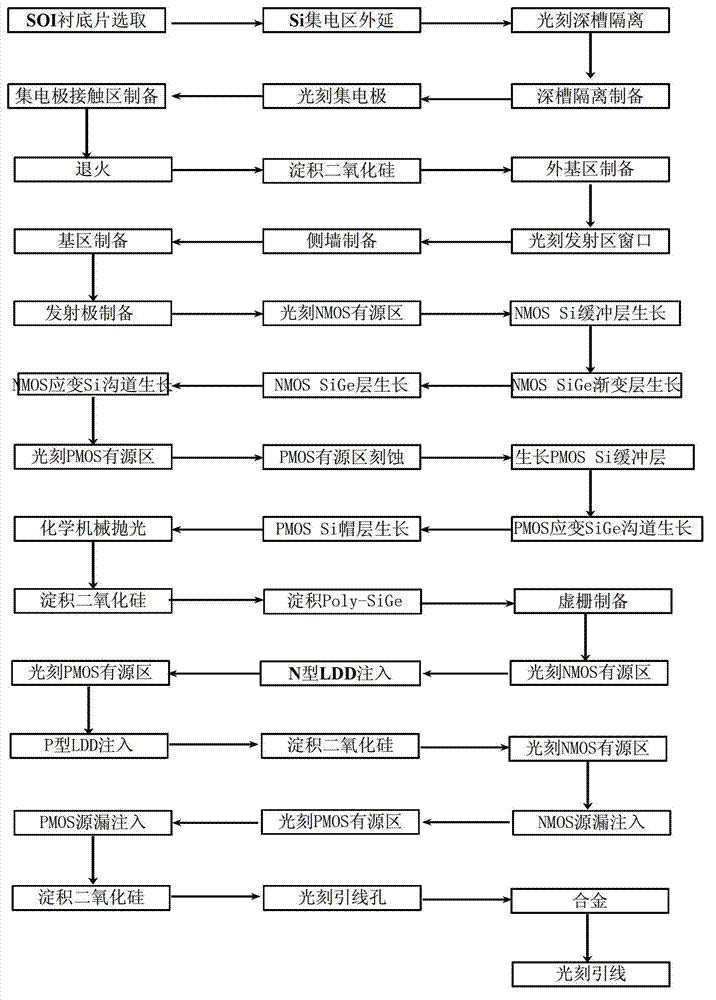

Self-aligned-technology-based tri-polycrystal SOI (Silicon On Insulator), SiGe and HBT (Heterojunction Bipolar Transistor) integrated device and preparation method thereof

InactiveCN102723361AImprove reverse breakdown voltageExcellent characteristic frequencySemiconductor/solid-state device manufacturingSemiconductor devicesElectrode ContactIntegrated circuit

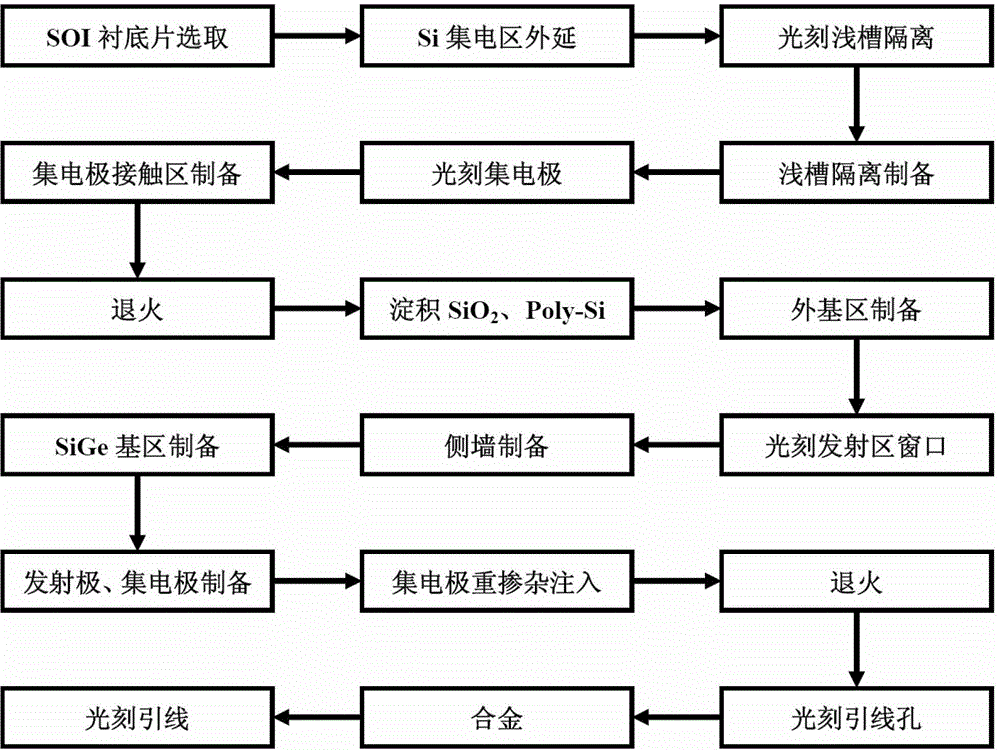

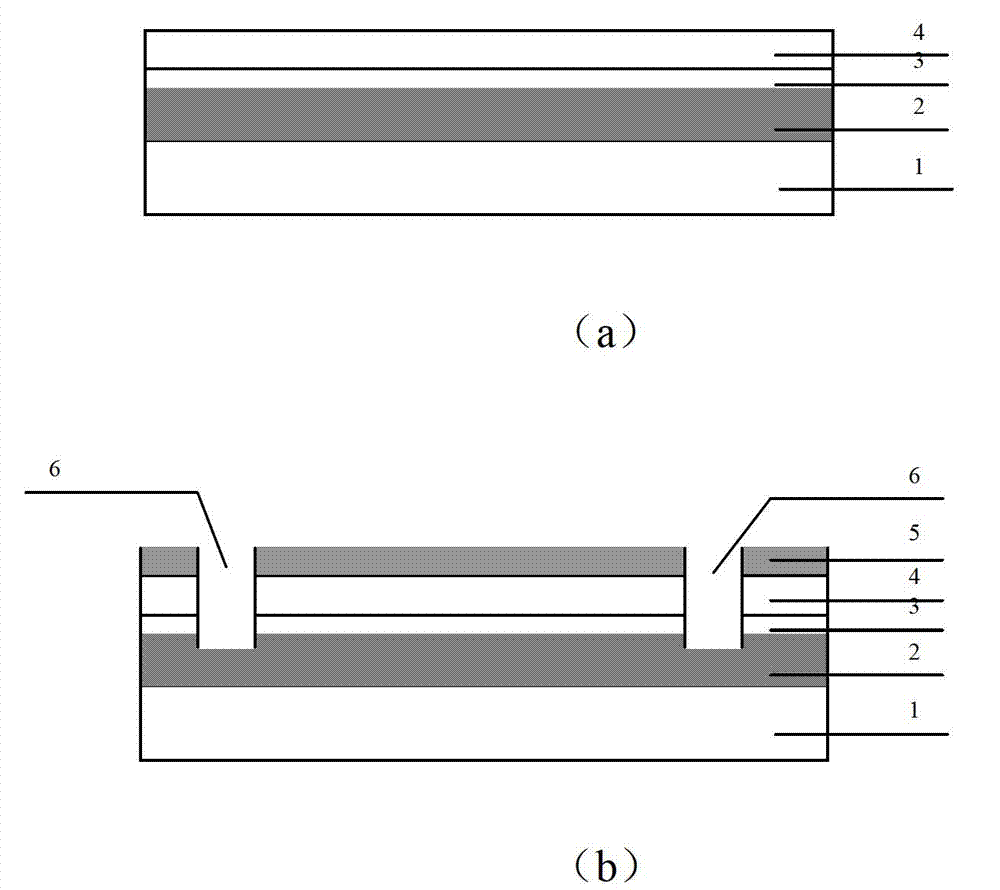

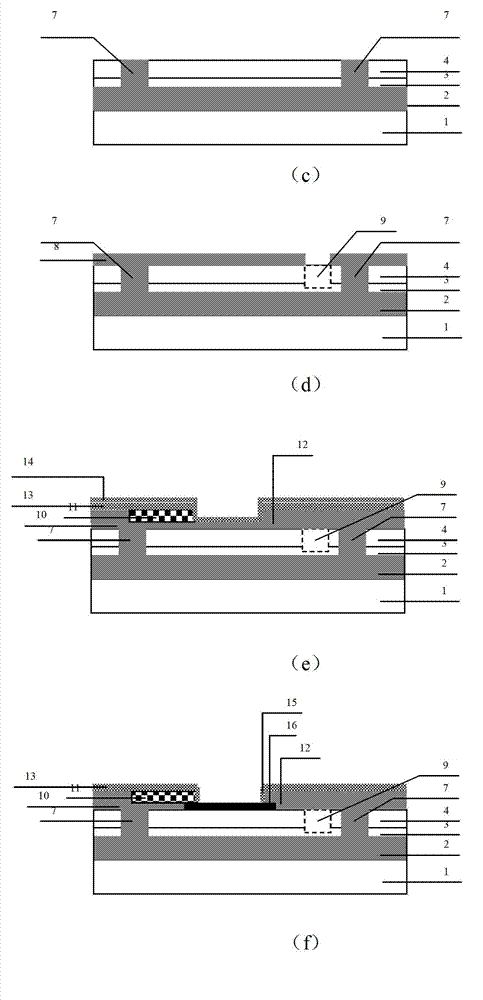

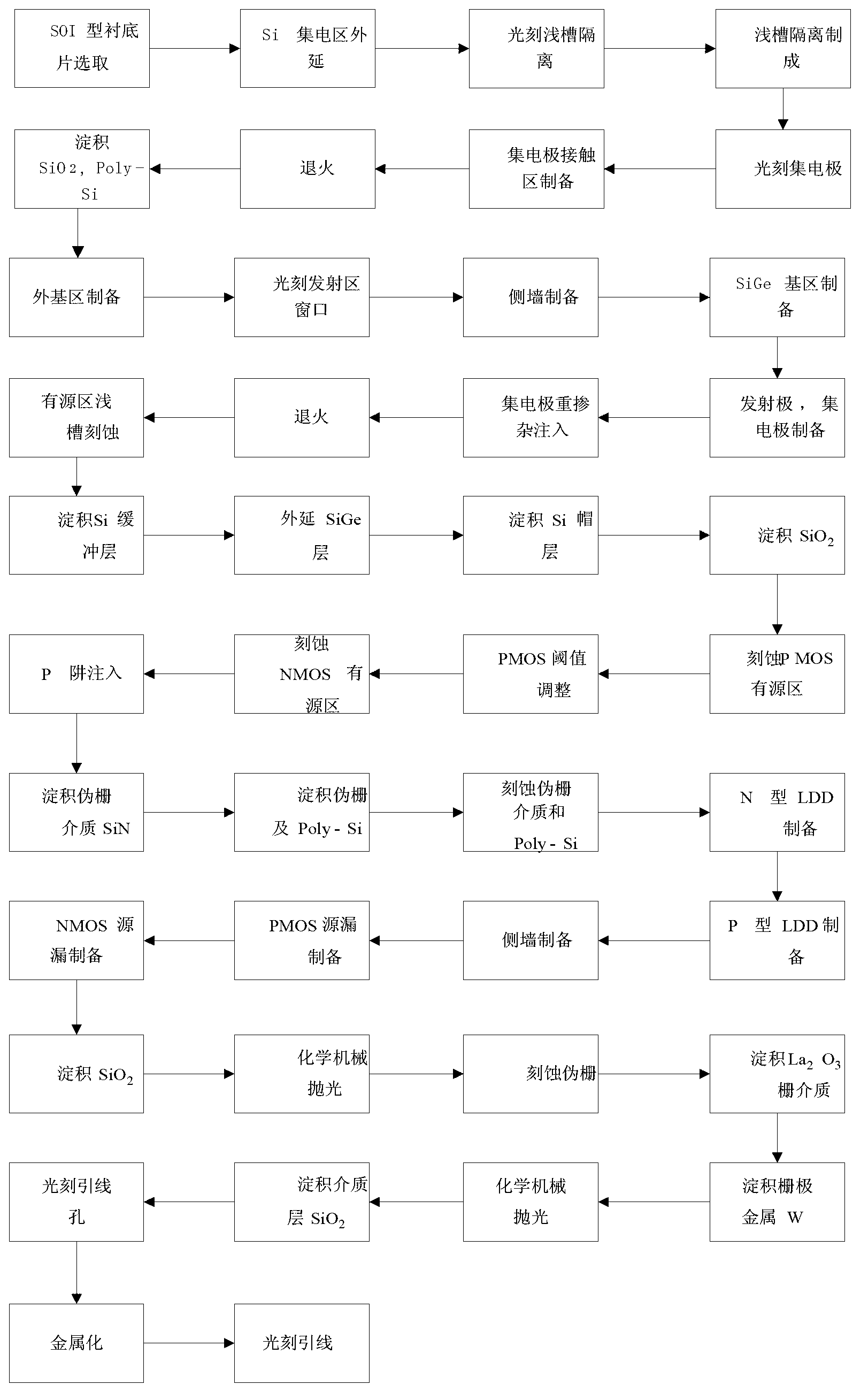

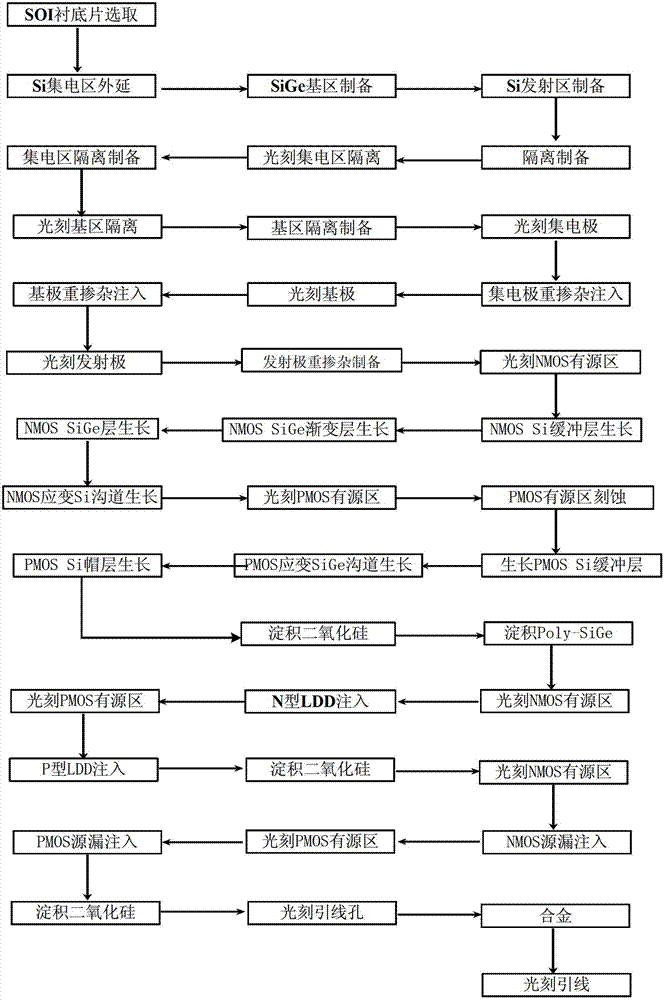

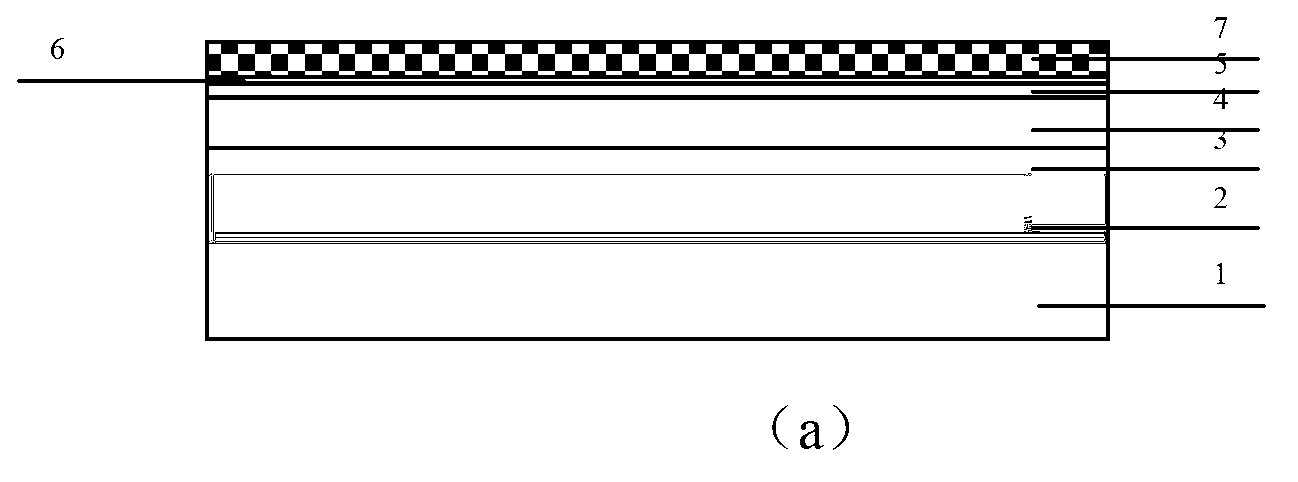

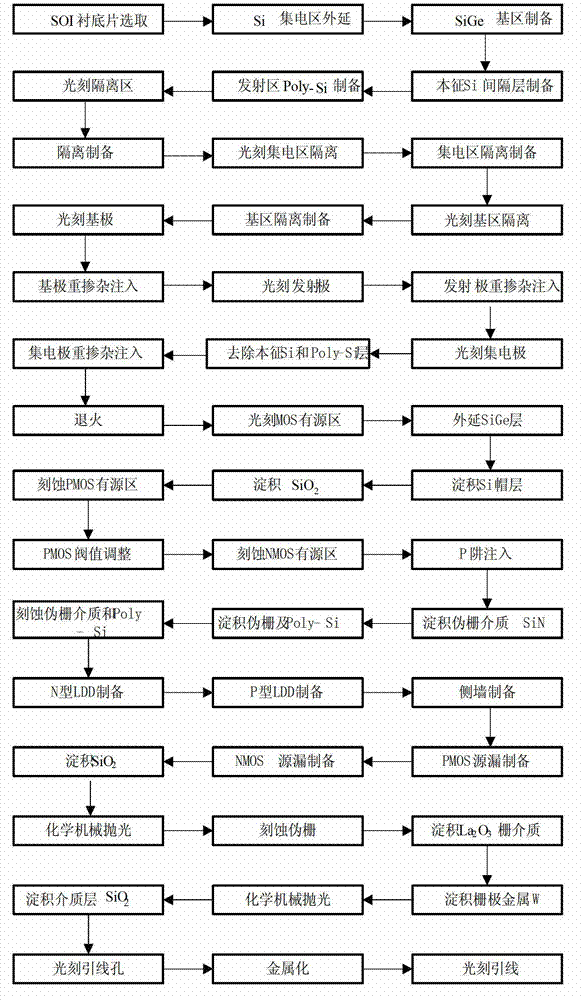

The invention is suitable for the technical field of semiconductor integrated circuits, and provides a self-aligned-technology-based tri-polycrystal SOI (Silicon On Chip), SiGe and HBT (Heterojunction Bipolar Transistor) integrated device and a preparation method of the device. The preparation process is as follows: growing N type Si epitaxy on an SOI substrate, conducting photoetching on shallow-trench isolation region, preparing a shallow-trench isolator, etching and implanting phosphorous ions so as to form an electrode contact region, sequentially depositing SiO2, P-Poly-Si, SiO2 and nitride, etching a window in a base region, selectively growing a SiGe base region, conducting photoetching on a collector electrode window, depositing N type Poly-Si, removing Poly-Si except an emitting electrode and the collector electrode to form an HBT device, and finally forming an HBT integrated circuit with the base region being 20-60nm in thickness. The process method provided by the invention is compatible with a conventional processing process of CMOS (Complementary Metal-Oxide-Semiconductor) integrated circuit, so that the SOI-based SIGeBi CMOS device and an integrated circuit can be prepared, and furthermore, the performance of a conventional analogue and digital-analogue mixed integrated circuit is improved greatly.

Owner:XIDIAN UNIV

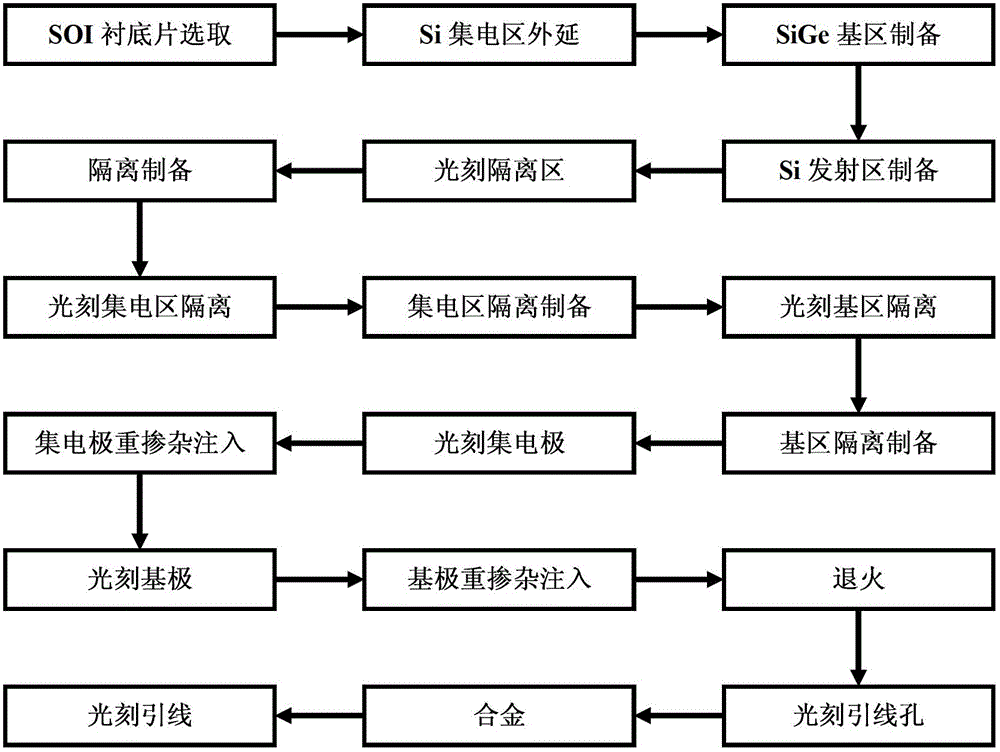

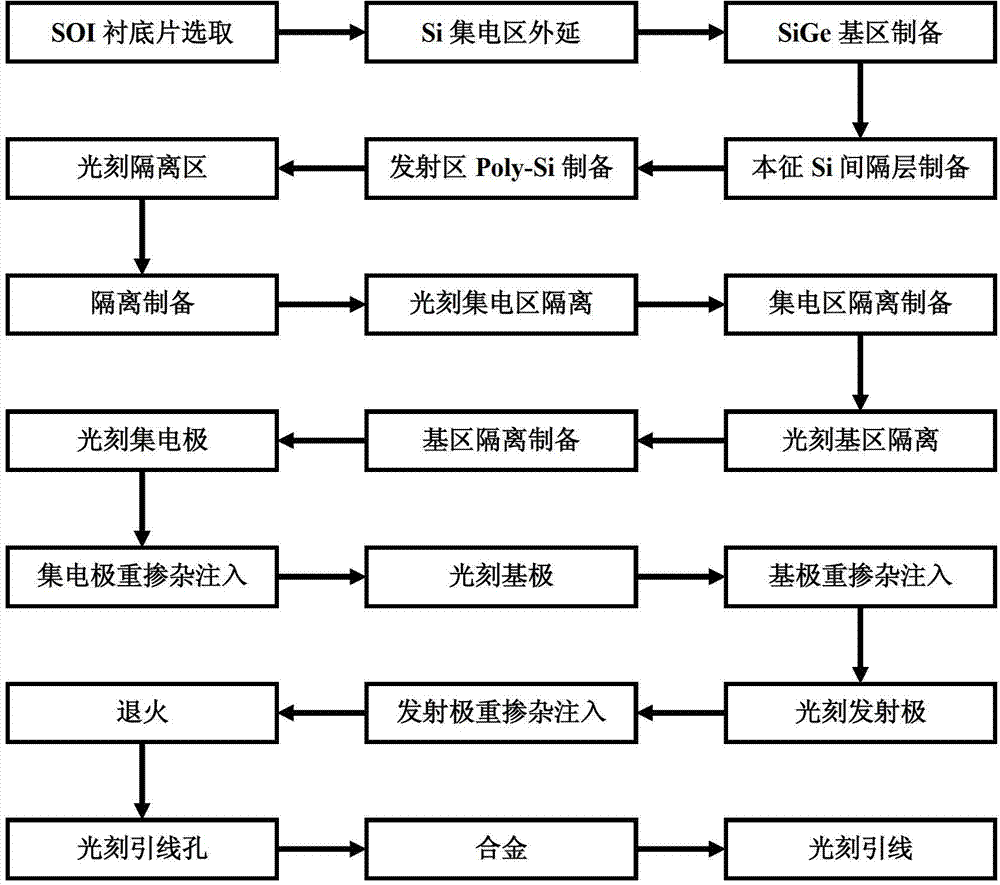

Double-polysilicon SOI (Silicon On Insulator) SiGe HBT (Heterojunction Bipolar Transistor) integrated device based on self-aligned technology and preparation method thereof

InactiveCN102738178AImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingPhosphoniumEngineering

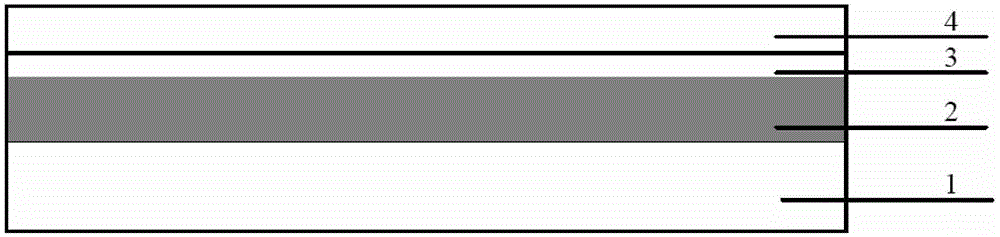

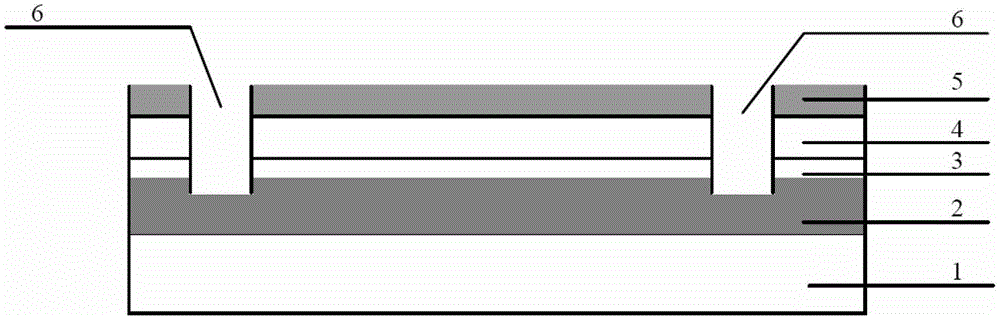

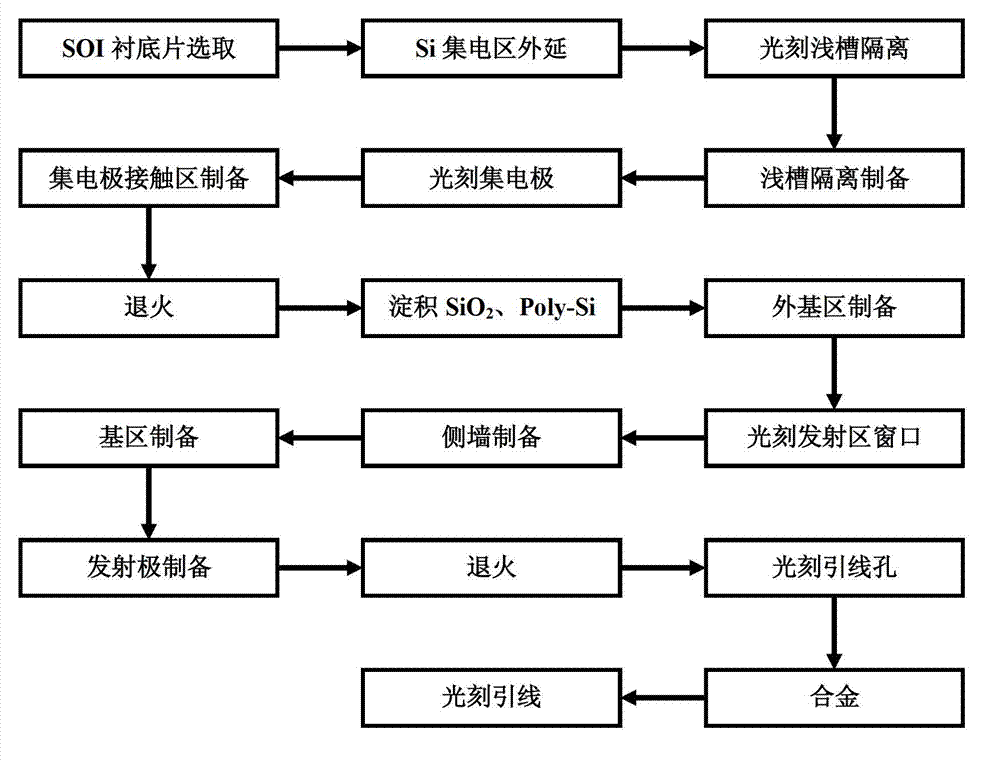

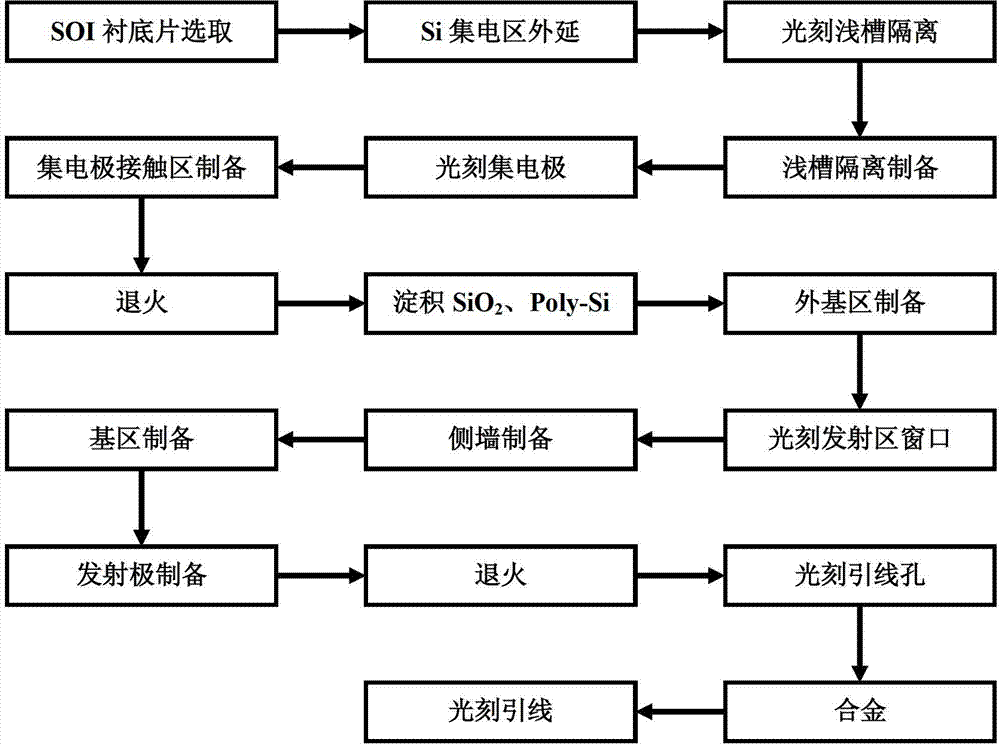

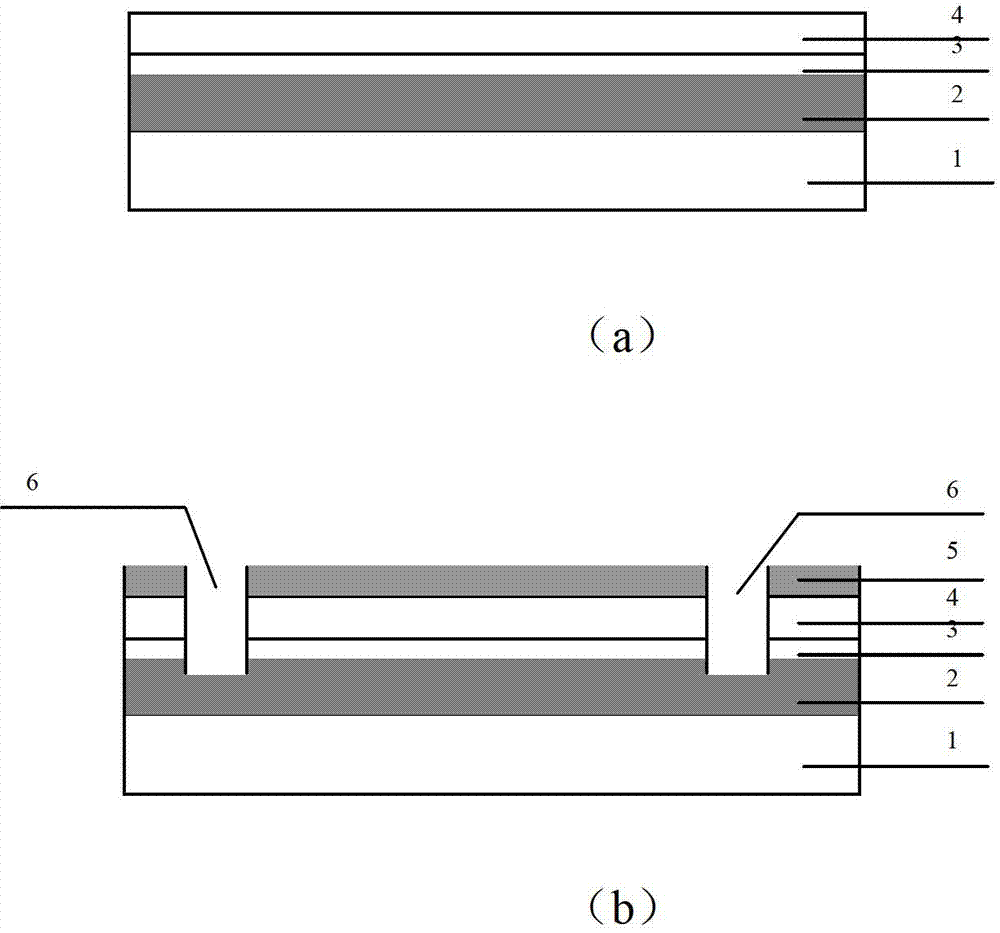

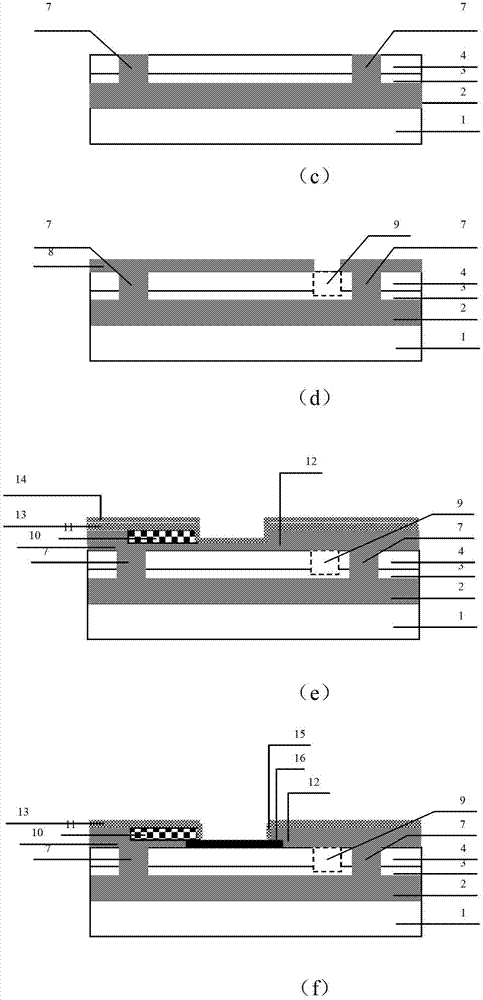

The invention is suitable for the technical field of semiconductor integrated circuit and provides a double-polysilicon SOI (Silicon On Insulator) SiGe HBT (Heterojunction Bipolar Transistor) integrated device based on self-aligned technology and a preparation method thereof. The preparation method comprises the following steps: growing N-type Si epitaxy on an SOI substrate; photoetching a shallow slot isolation region; preparing shallow slot isolation; etching and injecting phosphonium ions to form a collector contact region; depositing SiO2, P-Poly-Si, SiO2 and nitride in sequence; carrying out dry etching to form a nitride side wall; carrying out wet etching to form a base region window; selectively growing a SiGe base region; depositing N-type Poly-Si; then removing Poly-Si outside an emitter to form an HBT (Heterojunction Bipolar Transistor); and finally photoetching an emitter region, the base region and a collector region pin hole, metalizing, photoetching a lead wire to form an HBT integrated circuit in which the thickness of the base region is 20-60nm. The technique provided by the invention is compatible with the existing CMOS (Complementary Metal-Oxide-Semiconductor) integrated circuit processing technology, and can prepare the integrated circuit of a BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor) device based on SOI under the condition of little capital and equipment investment so that the performance of the existing analog and digital-analog hybrid integrated circuit is greatly improved.

Owner:XIDIAN UNIV

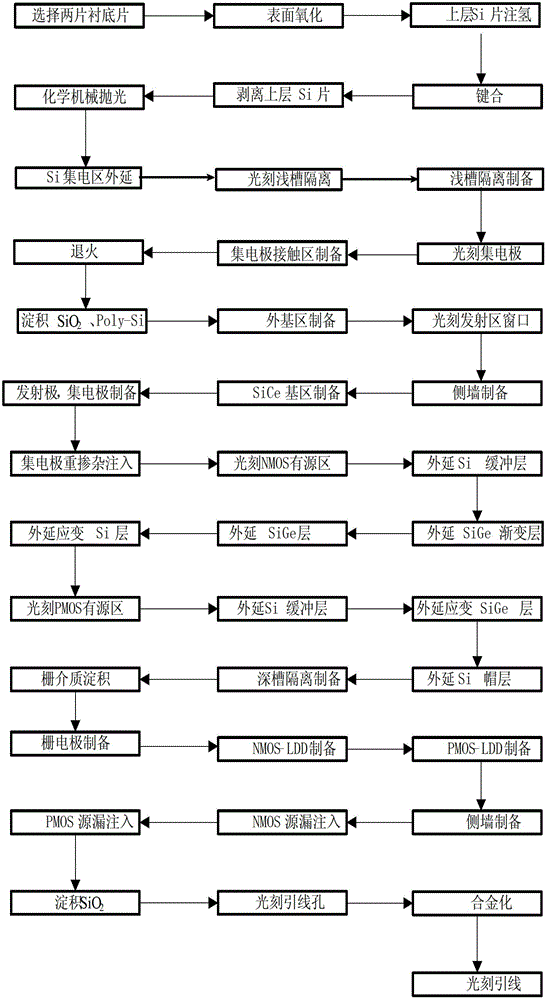

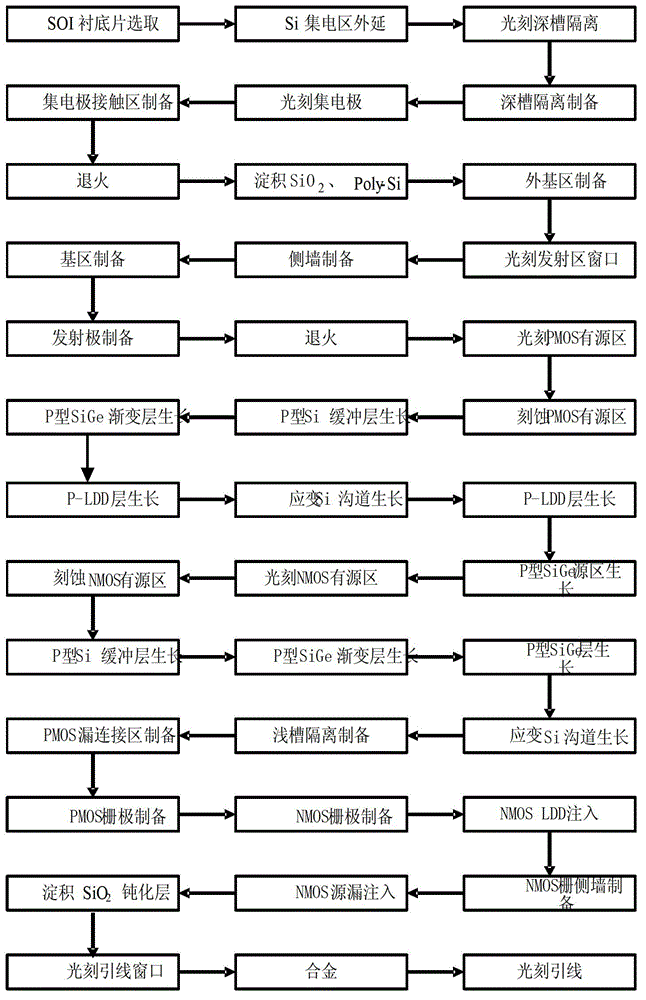

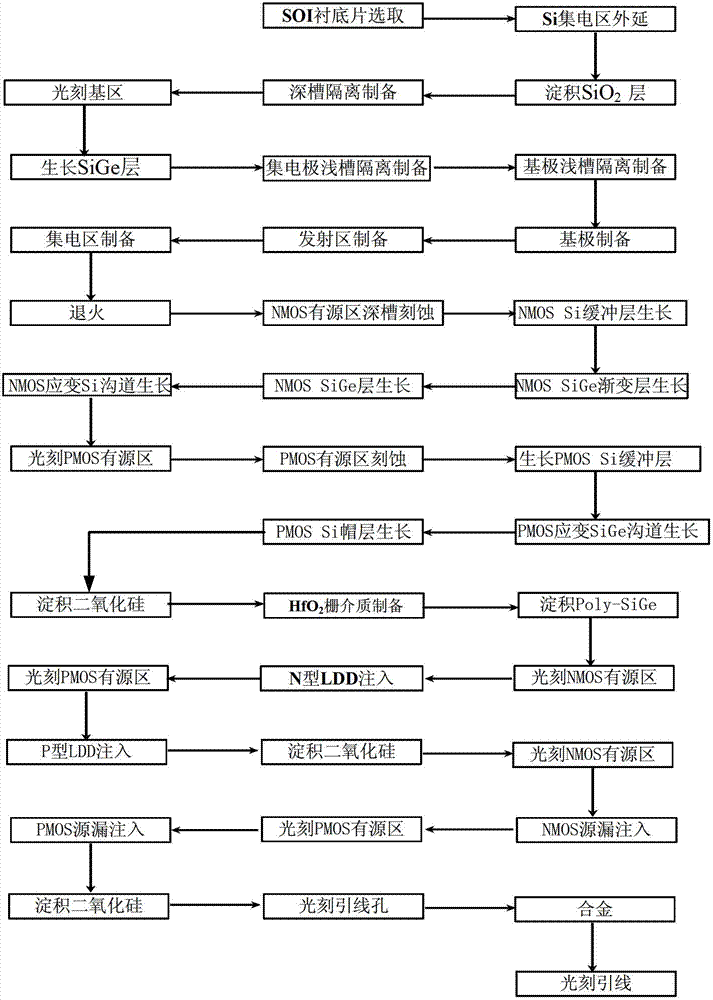

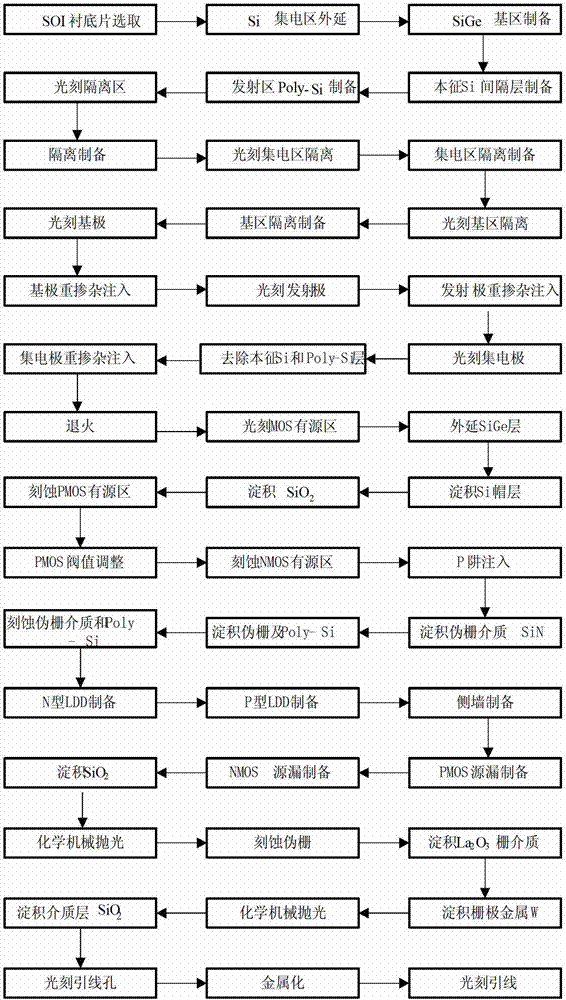

Silicon on insulator (SOI) SiGe bipolar complementary metal oxide semiconductor (BiCMOS) integrated device and preparation method thereof

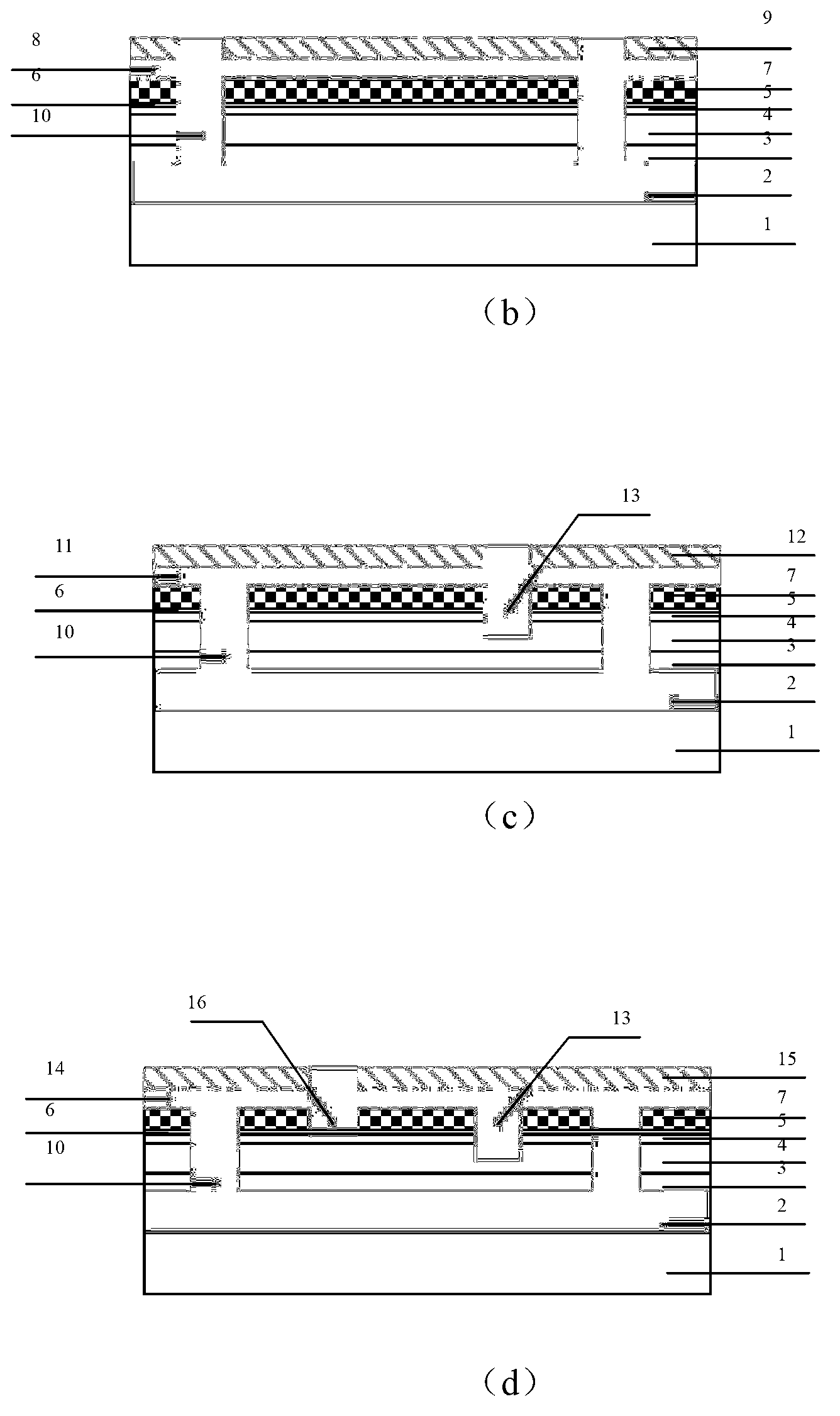

InactiveCN102800681AInhibition effectHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingEtchingGate dielectric

The invention discloses a silicon on insulator (SOI) SiGe bipolar complementary metal oxide semiconductor (BiCMOS) integrated device and a preparation method of the SOI SiGe BiCMOS integrated device. The method comprises the following steps of: growing an N-type Si epitaxial layer on an SOI substrate, preparing shallow-trench isolation, forming a collector contact region, etching to form a side wall, performing wet etching to form a base region window, selectively growing a SiGe base region, photoetching a collector window, depositing an N-type Poly-Si, removing the Poly-Si, and forming a SiGe HBT device; growing a strain SiGe material on the substrate, isolating an active region of the device, photoetching an active region of an N-channel metal oxide semiconductor (NMOS) device, performing P-type ion implantation, preparing a pseudo grid, self-aligning to grow a source drain region of a metal oxide semiconductor (MOS) device, removing the pseudo grid, preparing a lanthanum oxide material to form gate dielectric and preparing metal tungsten to form a gate in a stamping groove at the pseudo grid, photoetching a lead, and preparing the integrated device and the circuit. According to the method, the characteristics of SiGe are fully utilized, and due to the prepared integrated circuit, the performance of the conventional analog and digital / analog mixed integrated circuit is greatly improved.

Owner:XIDIAN UNIV

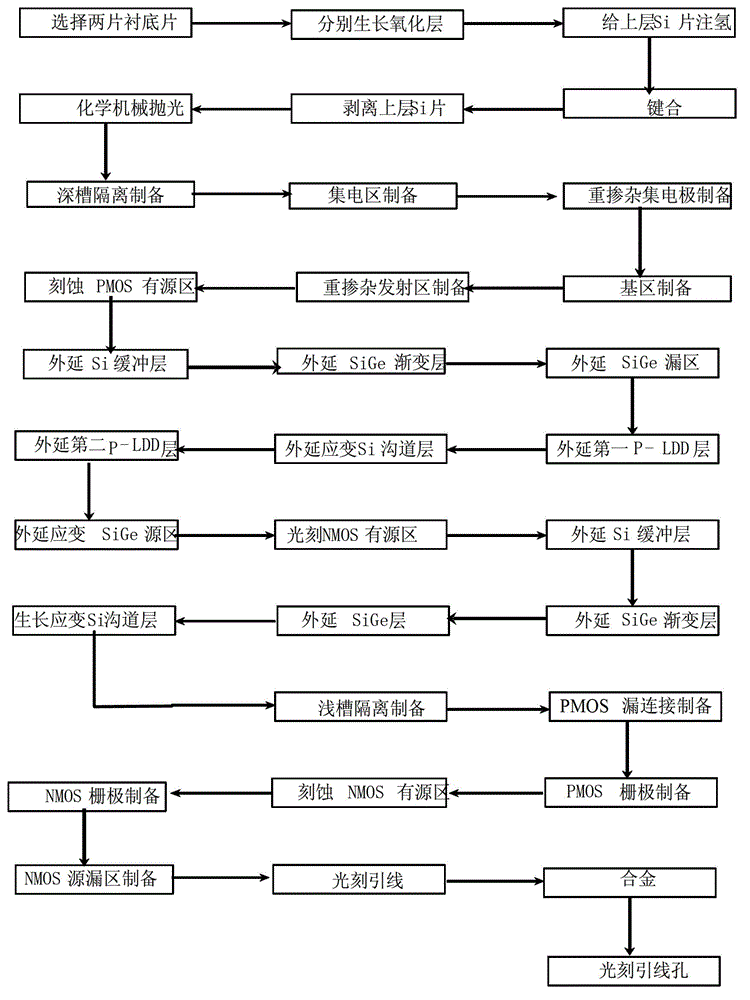

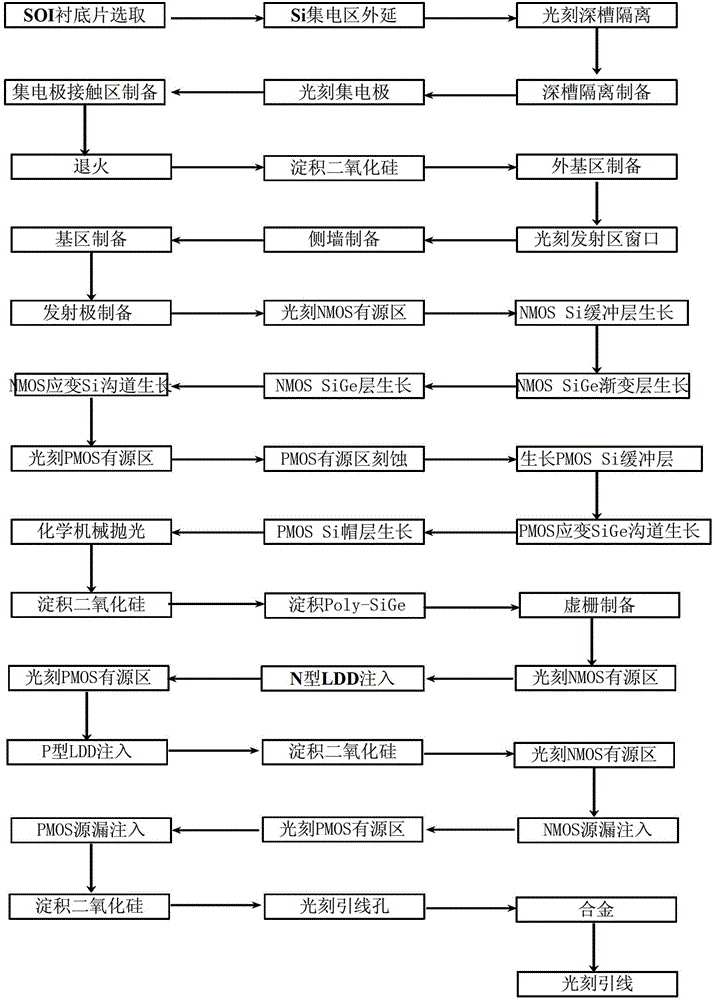

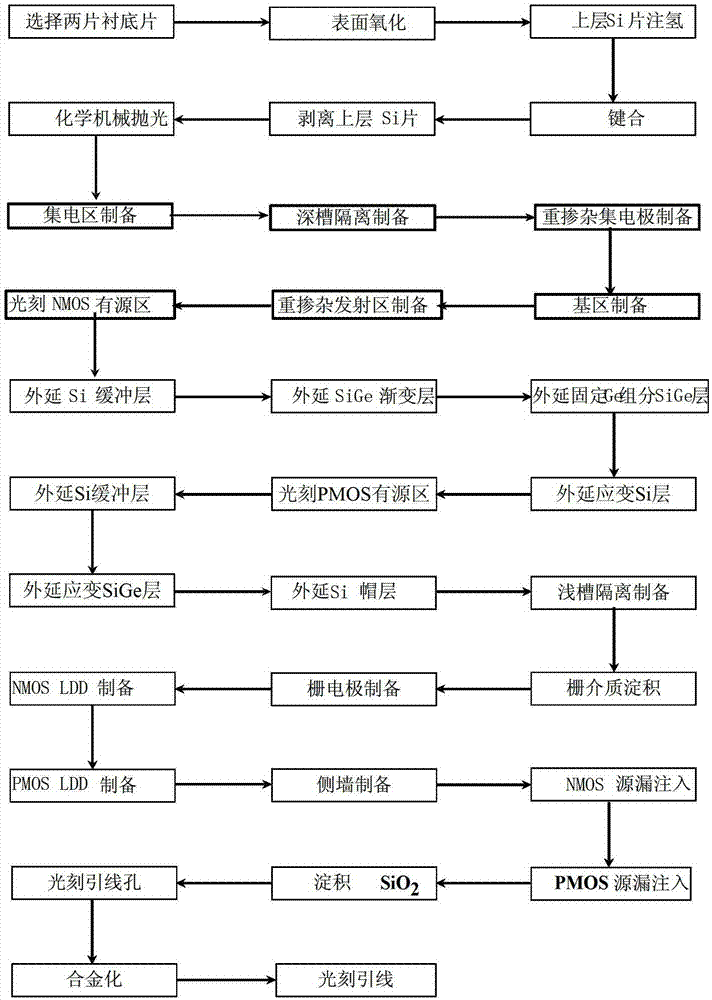

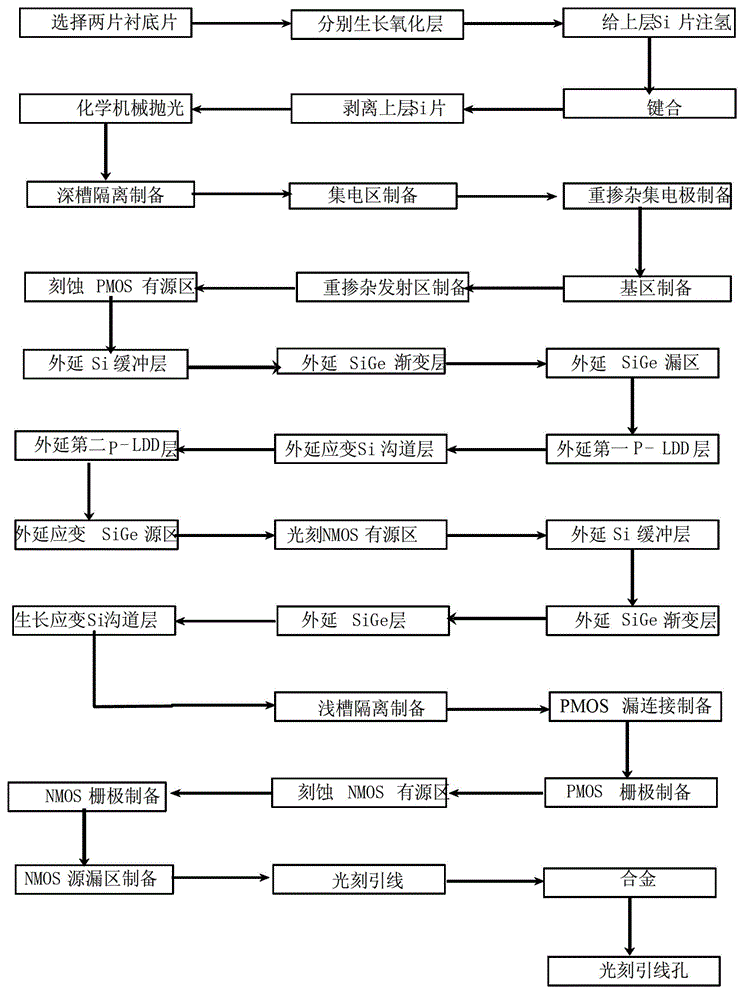

Strain Si BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device based on SOI SiGe HBT (Heterojunction Bipolar Transistor) and preparation method thereof

InactiveCN102916015AImprove performanceHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingHemt circuitsDevice Grid

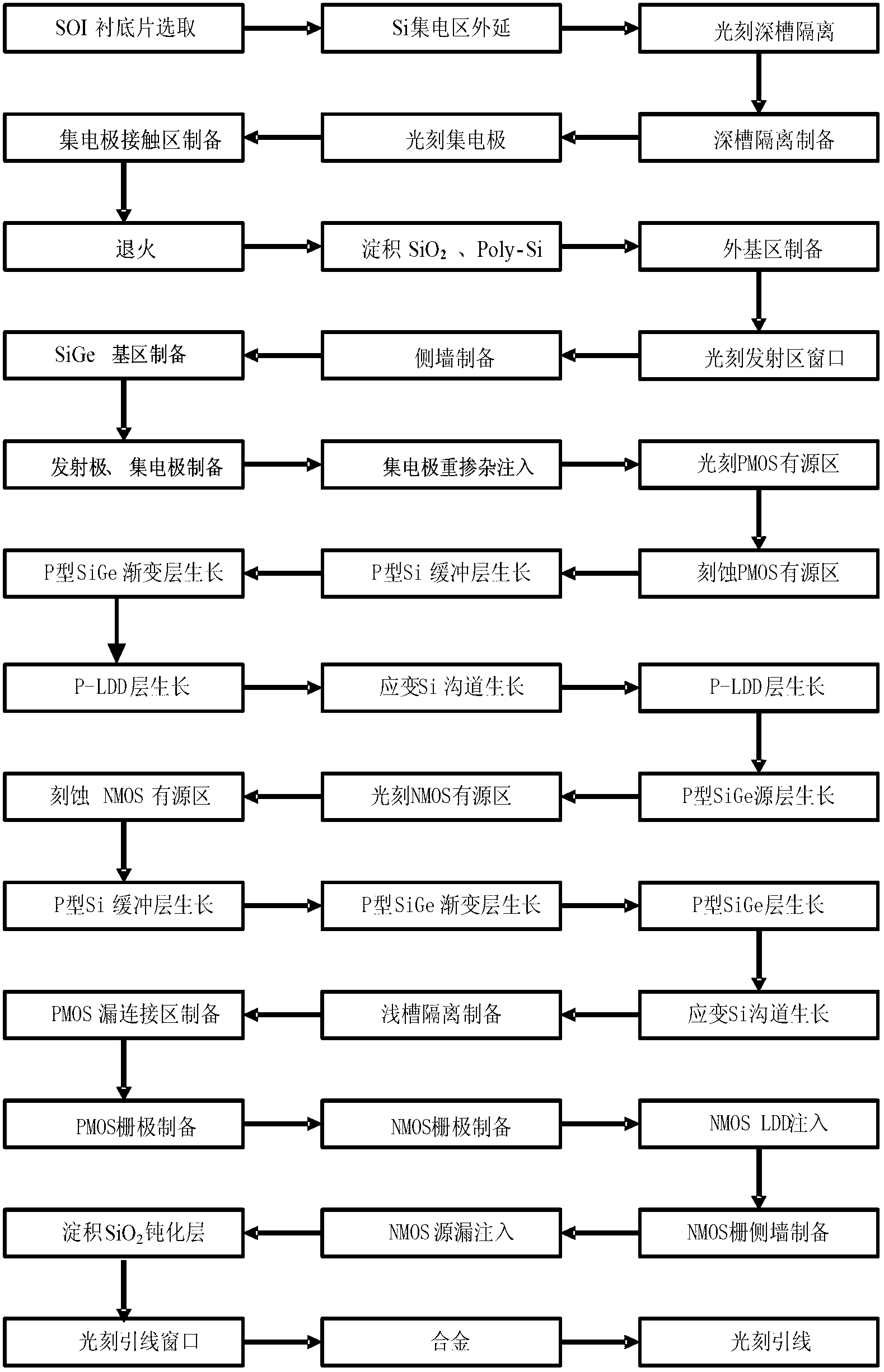

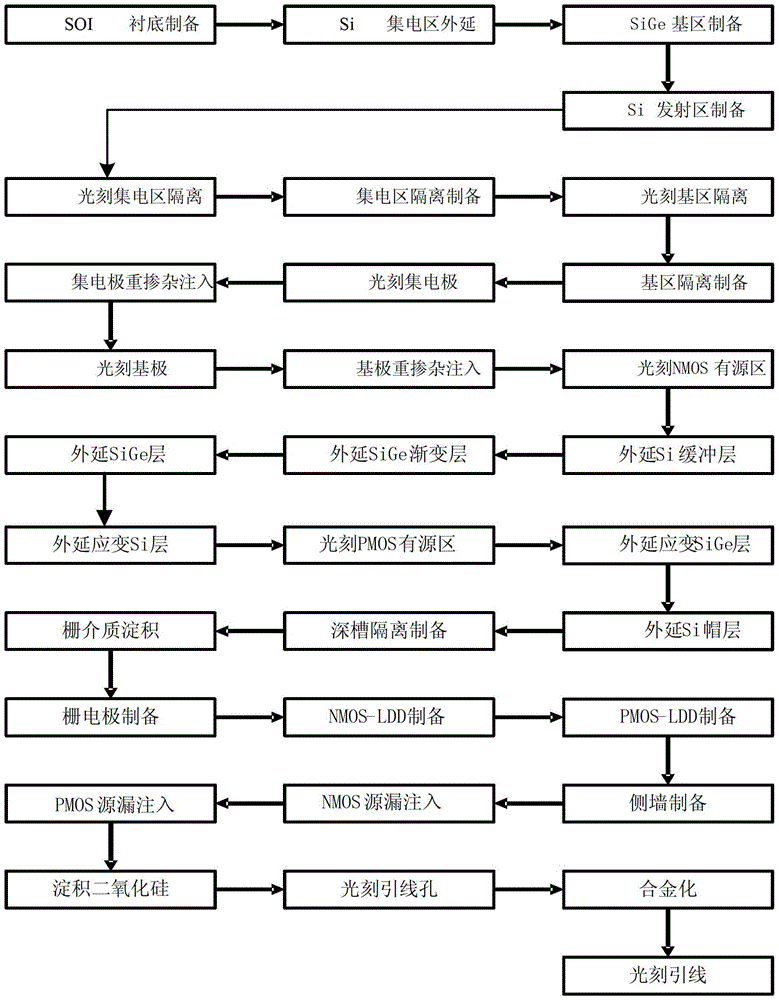

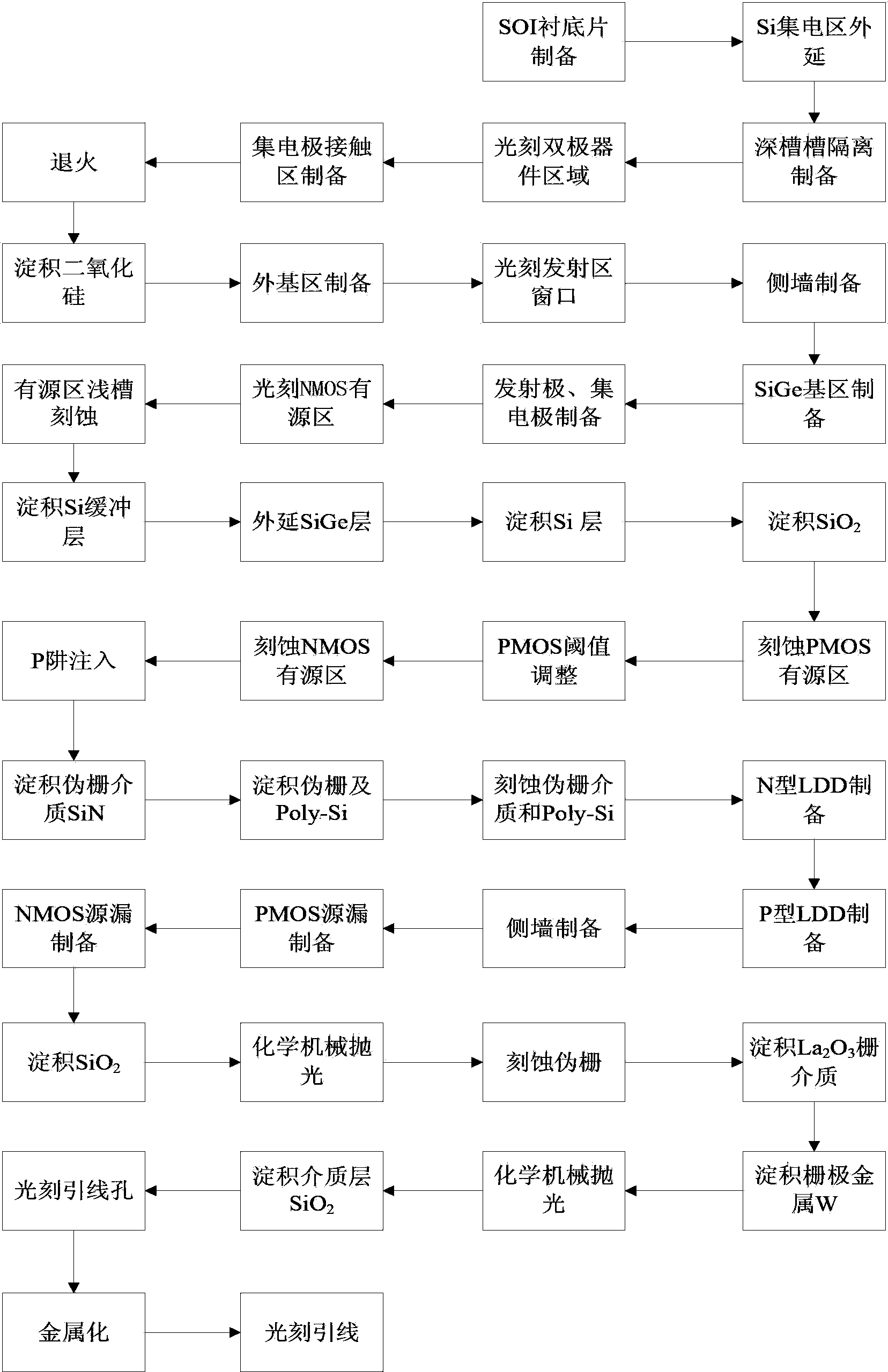

The invention discloses a strain Si BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device based on SOI SiGe HBT (Heterojunction Bipolar Transistor) and a preparation method thereof. The preparation method comprises the following steps: growing N-type Si epitaxy on a substrate, preparing a deep-trench isolator, forming a collector contact region, dryly etching to form a nitride side wall, wetly etching to form a base window, selectively growing a SiGe base region, and photoetching a collector window, removing Poly-Si to form a SiGe HBT device; photoetching an MOS (Metal Oxide Semiconductor) device active area groove, respectively and continuously growing Si buffer layer, gradient SiGe layer, fixed component SiGe layer, N-type strain Si channel layer, Si buffer layer and the like in the MOS device active area groove, and preparing a drain electrode and a grid electrode to form a PMOS (Positive channel Metal Oxide Semiconductor) device; and preparing an NMOS (Negative channel Metal Oxide Semiconductor) device grid dielectric layer and a grid polycrystal to form an NMOS device. The characteristic of tension strain Si material such as mobility anisotropy is fully utilized to prepare the BiCMOS integrated device with strengthened performance and a circuit thereof.

Owner:XIDIAN UNIV

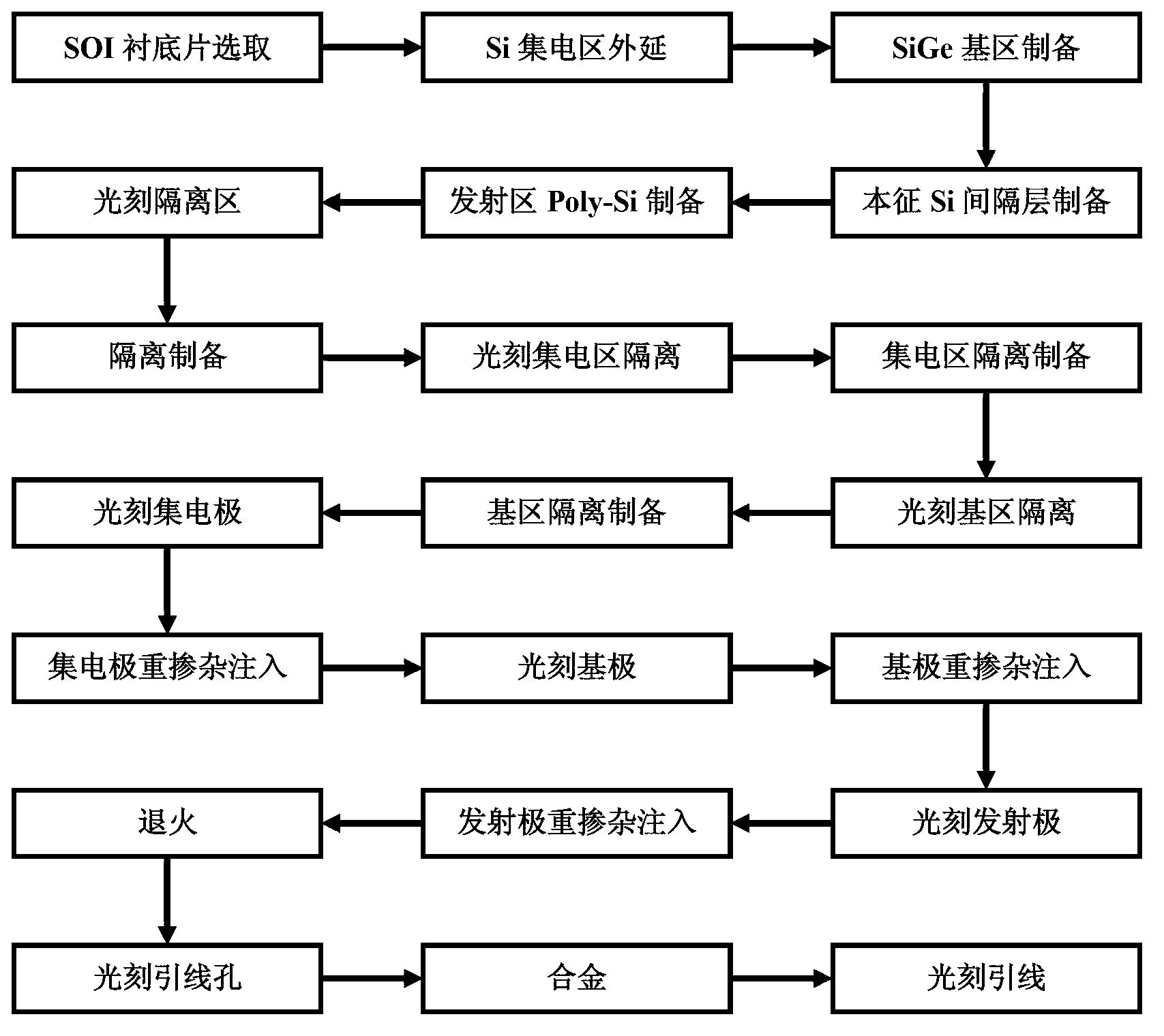

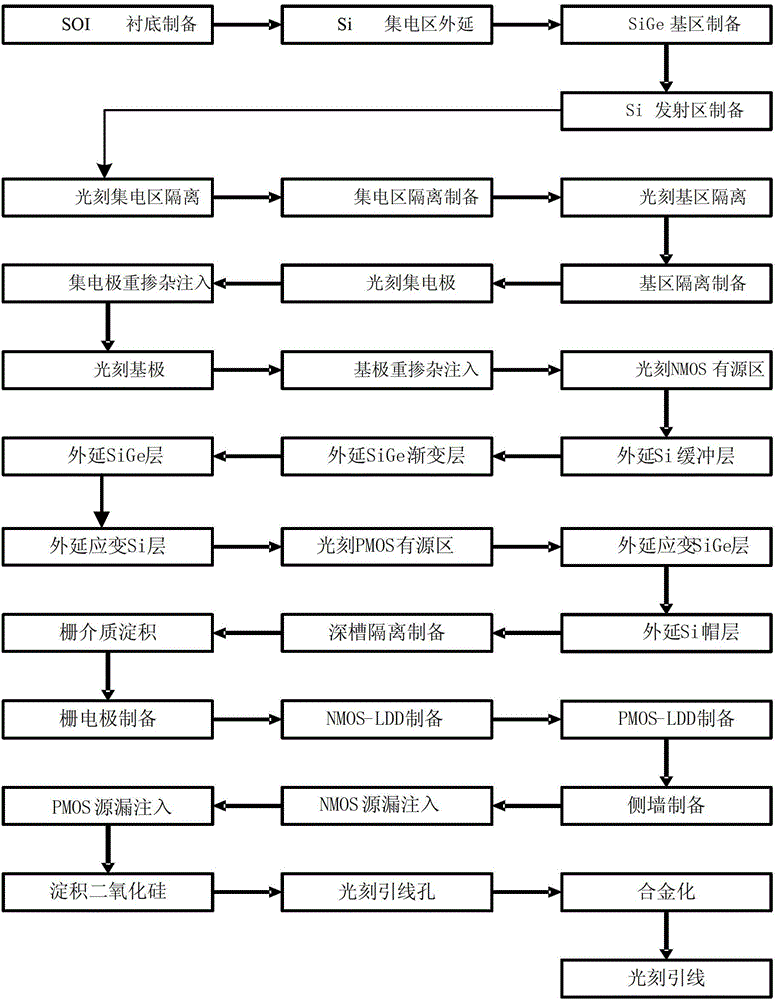

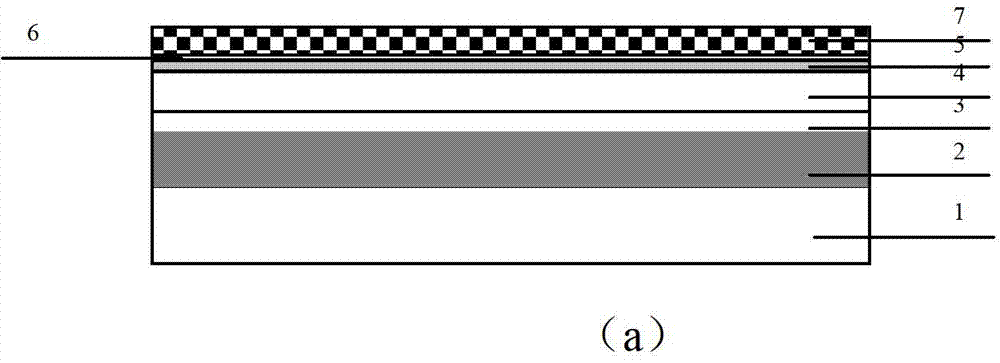

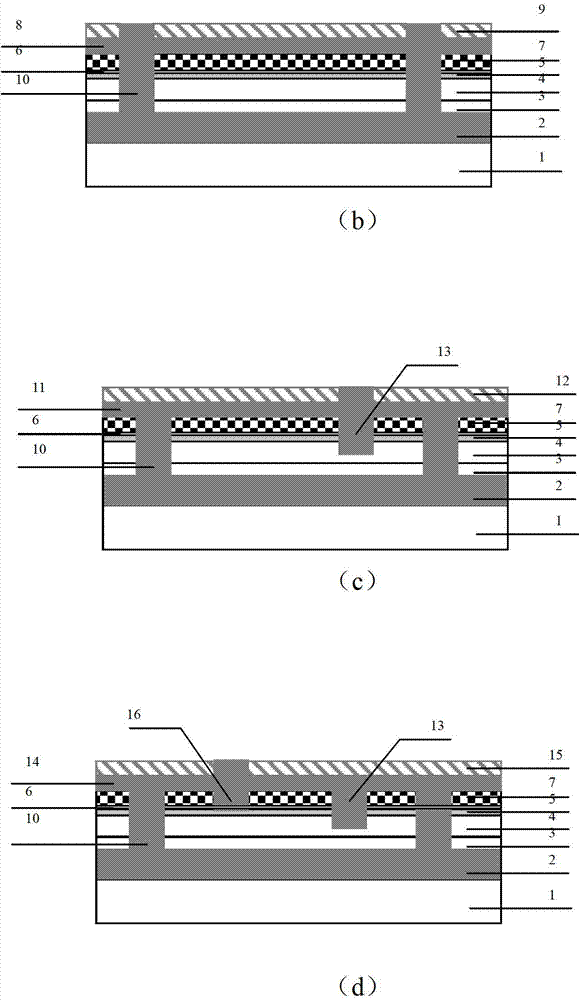

Silicon-on-insulator silicon germanium heterojunction bipolar transistor (SOI SiGe HBT) planar integrated device and preparation method thereof

ActiveCN102842600AImprove reverse breakdown voltageExcellent characteristic frequencySemiconductor/solid-state device manufacturingSemiconductor devicesElectrode ContactIon implantation

The invention discloses a silicon-on-insulator silicon germanium heterojunction bipolar transistor (SOI SiGe HBT0 planar integrated device and a preparation method thereof. The preparation method comprises following steps of continuously growing N-channel silicon (N-Si), P-channel silicon germanium (P-SiGe) and an N-channel silicon (N-Si) layer to deposit a dielectric layer to prepare shallow-trench isolation, photo-etching a collector region shallow-trench isolation area, preparing a collector region shallow-trench isolation, etching and depositing a dielectric layer, photo-etching a base-region shallow-trench isolation area, preparing a base-region shallow-trench isolation, photo-etching a collector region and injecting phosphorous ions to form a collector electrode contact region, photo-etching a base region and injecting boron ions to form a base electrode contact area, finally forming a SiGe HBT device, finally photo-etching a transmitting region lead hole, a base region lead holeand a collector region lead hole, metalizing, photo-etching leads, and forming an HBT integrated circuit with the thickness of the base region of 20 to 60nm. The technical method provided by the invention is compatible with the processing technique of the traditional CMOS integrated circuit, so that under the situation that the fund and the equipment investment are small, the SOI-based bipolar complementary metal-oxide semiconductor (BiCMOS) device and an integrated circuit are prepared, and the performance of the traditional analog and digital mixed integrated circuit is greatly improved.

Owner:陕西半导体先导技术中心有限公司

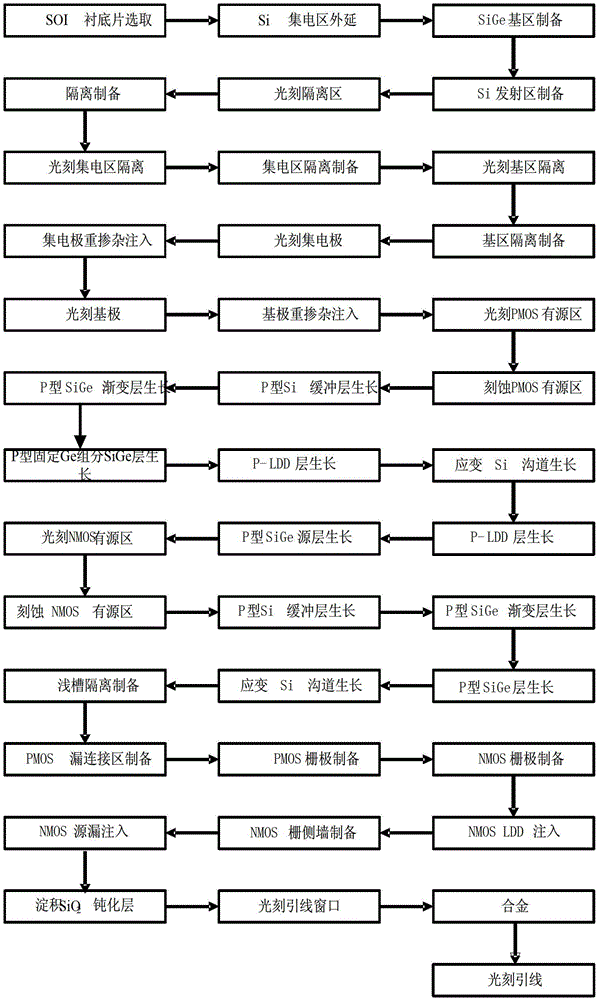

Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device with mixed crystal plane and Si vertical channel and preparation method thereof

InactiveCN102723341AImprove mobilityHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingCrystal planeP channel

The invention discloses a Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device with a mixed crystal plane and a Si vertical channel and a preparation method of the device. The preparation process is as follows: preparing an SOI (Silicon-On-Insulator) substrate, taking upper-layer base material as a crystal plane (100) and taking lower-layer base material as a crystal plane (110); growing N type Si epitaxy on a substrate sheet to prepare a deep-trench isolator, and manufacturing a conventional Si bipolar transistor in a bipolar device region; etching a deep trench in an active region of a PMOS (P-Channel Metal Oxide Semiconductor) device, selectively growing an active layer of a strain Si PMOS device, and preparing a compressive strain PMOS device with a vertical channel on the active layer; and etching a deep trench in an active region of an NMOS (N-Channel Metal Oxide Semiconductor) device, selectively growing an active layer of a strain Si NMOS device, and preparing a tensile strain NMOS device with a plane channel on an epitaxial layer. According to the Bi CMOS integrated device with the mixed crystal plane and the Si vertical channel and the preparation method, the characteristics that the mobility ratio of strain Si material is higher than the stress of body Si material and the strain Si material, and the mobility ratio is anisotropic are utilized, and based on the SOI substrate, the Bi CMOS integrated device with the mixed crystal plane and the Si vertical channel and a circuit, which are excellent in performance, are prepared.

Owner:XIDIAN UNIV

Crystal plane-based Tri-polycrystal-plane Bi CMOS (Complentary Metal-Oxide-Semiconductor) integrated device and preparation method thereof

InactiveCN102723343AImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingHemt circuitsCrystal plane

The invention discloses a crystal plane-based tri-polycrystal-plane Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device and a preparation method of the device. The preparation process is as follows: preparing an SOI (Silicon On Insulator) substrate; growing N type Si epitaxy and preparing a deep-trench isolator so as to form a collector electrode contact region and a nitride side wall, etching a window in a base region, growing a SiGe base region, conducting photoetching on a collector electrode window, depositing N type Poly-Si, and preparing an emitting electrode and the collector electrode to form an HBT (Heterojunction Bipolar Transistor) device; etching a deep trench in an NMOS (N-Channel Metal Oxide Semiconductor) device region, selectively growing a strain Si epitaxial layer with a crystal plane (100) to prepare an NMOS device with a Si channel; selectively growing a strain SiGe epitaxial layer with a crystal plane (110) to prepare a PMOS (P-Channel Metal Oxide Semiconductor) device with a SiGe channel, and thus forming the crystal plane-based tri-polycrystal-plane Bin CMOS integrated device and a circuit. According to the crystal plane-based tri-polycrystal-plane Bi CMOS integrated device and the preparation method, the characteristics that the electronic mobility of tensile strain Si material is higher than that of Si material, the electronic mobility of strain SiGe material is higher than of that of body Si material, and the electronic mobility is anisotropic are utilized, and based on the SOI substrate, the plane Bi CMOS integrated circuit is prepared, and the performance of the Bi CMOS integrated device is enhanced.

Owner:XIDIAN UNIV

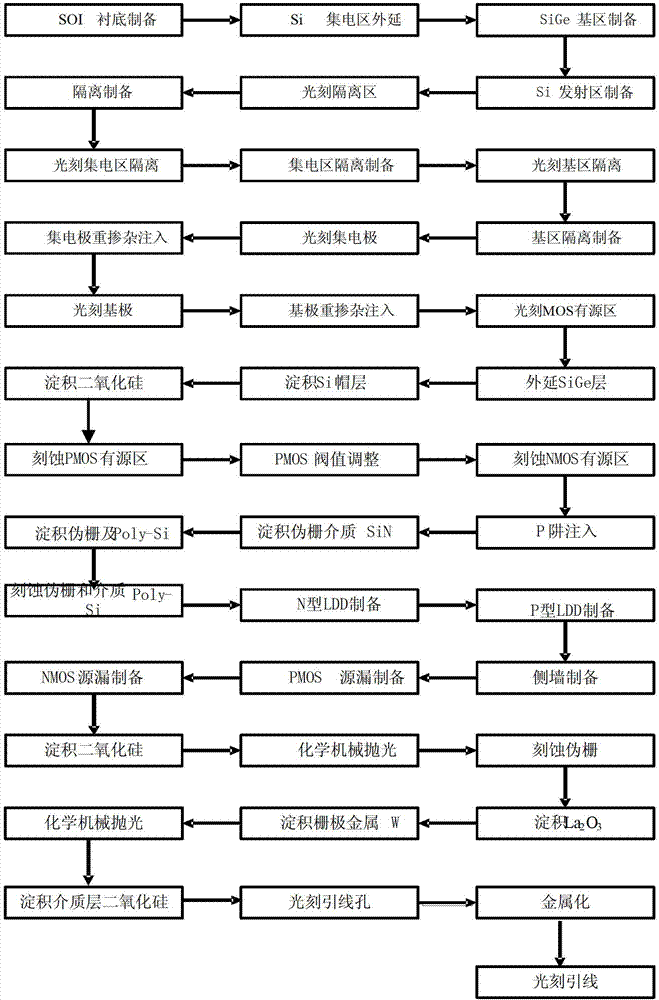

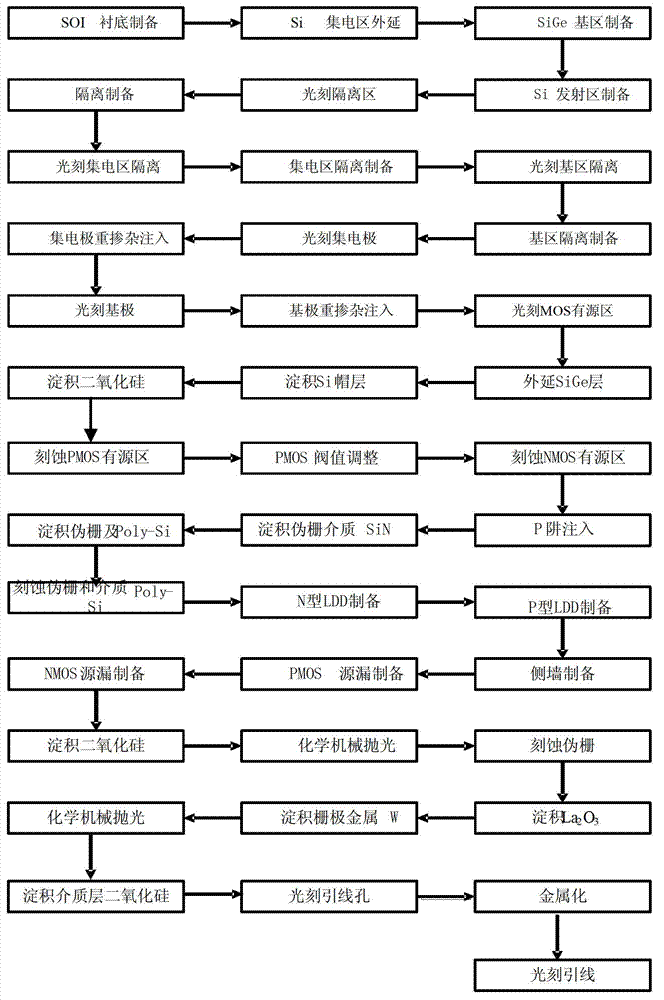

A dual-strain bicmos integrated device based on soi substrate and its preparation method

InactiveCN102810544BSuppress performance impactInhibition effectSolid-state devicesSemiconductor/solid-state device manufacturingPhosphoniumTransmitter

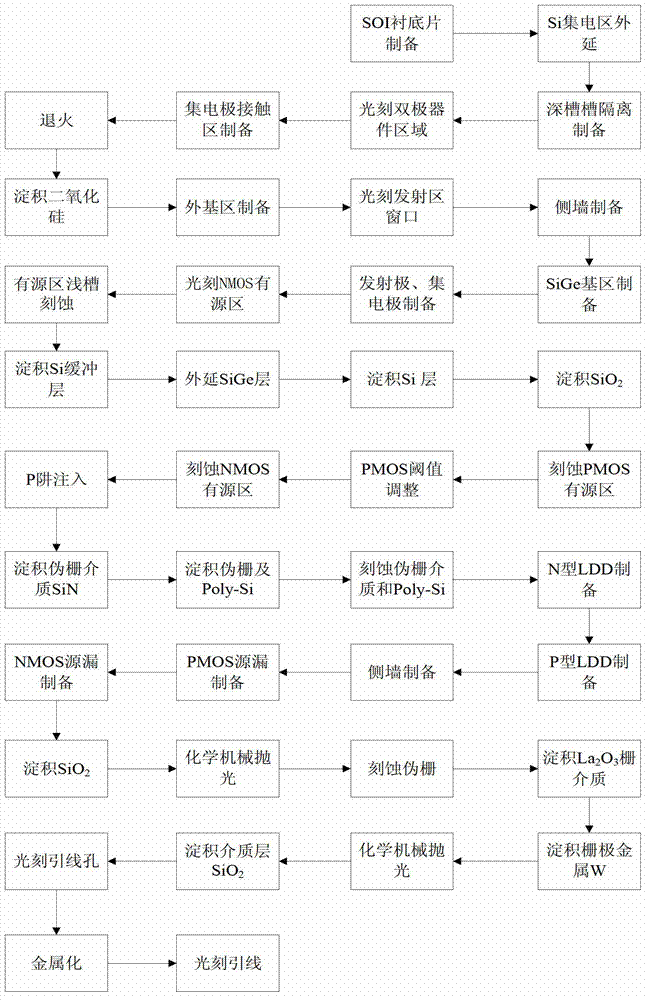

The invention discloses a dual-strain bipolar complementary metal-oxide semiconductor (BiCMOS) integration device based on a silicon on insulator (SOI) substrate and a preparation method thereof. The preparation method comprises following steps that a negative-silicon (N-Si) layer, a positive-silicon germanium (P-SiGe) layer and an N-Si layer continuously grow on the SOI substrate, a deep groove isolator is prepared, a collector zone shallow groove isolator and a base zone shallow groove isolator are prepared, a collector zone is photo-etched, phosphonium ions are injected to form a collector electrode, a base electrode and a transmitter electrode, and a SiGe heterojunction bipolar transistor (HBT) device is formed; a strain SiGe material grow on the substrate, an N-channel MOS (NMOS) device active region and a P-channel MOS (PMOS) device active region are formed, a pseudo grid is prepared, a source drain region of the NMOS and the PMOS devices is respectively generated in a self-aligning way, the pseudo grid is eliminated, a lanthanum oxide (La2O3) material is prepared in a pressing groove at the pseudo grid to form a grid medium and metal tungsten (W) to form a grid electrode, a lead is photo-etched, and a dual-strain plane BiCMOS integration device and a circuit based on the SOI substrate are formed. According to the method, the characteristic that a hole mobility of the strain SiGe material is higher than that of the bulk-Si material is adequately utilized to prepare the dual-strain plane BiCMOS integration circuit based on the SOI substrate, so that the performance of the existing analog and digital-analog mixed integrated circuit is greatly improved.

Owner:XIDIAN UNIV

Crystal plane-based Tri-polycrystal-plane Bi CMOS (Complentary Metal-Oxide-Semiconductor) integrated device and preparation method thereof

InactiveCN102723343BImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingCrystal planeElectrode Contact

The invention discloses a crystal plane-based tri-polycrystal-plane Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device and a preparation method of the device. The preparation process is as follows: preparing an SOI (Silicon On Insulator) substrate; growing N type Si epitaxy and preparing a deep-trench isolator so as to form a collector electrode contact region and a nitride side wall, etching a window in a base region, growing a SiGe base region, conducting photoetching on a collector electrode window, depositing N type Poly-Si, and preparing an emitting electrode and the collector electrode to form an HBT (Heterojunction Bipolar Transistor) device; etching a deep trench in an NMOS (N-Channel Metal Oxide Semiconductor) device region, selectively growing a strain Si epitaxial layer with a crystal plane (100) to prepare an NMOS device with a Si channel; selectively growing a strain SiGe epitaxial layer with a crystal plane (110) to prepare a PMOS (P-Channel Metal Oxide Semiconductor) device with a SiGe channel, and thus forming the crystal plane-based tri-polycrystal-plane Bin CMOS integrated device and a circuit. According to the crystal plane-based tri-polycrystal-plane Bi CMOS integrated device and the preparation method, the characteristics that the electronic mobility of tensile strain Si material is higher than that of Si material, the electronic mobility of strain SiGe material is higher than of that of body Si material, and the electronic mobility is anisotropic are utilized, and based on the SOI substrate, the plane Bi CMOS integrated circuit is prepared, and the performance of the Bi CMOS integrated device is enhanced.

Owner:XIDIAN UNIV

Silicon-on-insulator silicon germanium heterojunction bipolar transistor (SOI SiGe HBT) planar integrated device and preparation method thereof

ActiveCN102842600BImprove reverse breakdown voltageExcellent characteristic frequencySemiconductor/solid-state device manufacturingSemiconductor devicesElectrode ContactP channel

The invention discloses a silicon-on-insulator silicon germanium heterojunction bipolar transistor (SOI SiGe HBT0 planar integrated device and a preparation method thereof. The preparation method comprises following steps of continuously growing N-channel silicon (N-Si), P-channel silicon germanium (P-SiGe) and an N-channel silicon (N-Si) layer to deposit a dielectric layer to prepare shallow-trench isolation, photo-etching a collector region shallow-trench isolation area, preparing a collector region shallow-trench isolation, etching and depositing a dielectric layer, photo-etching a base-region shallow-trench isolation area, preparing a base-region shallow-trench isolation, photo-etching a collector region and injecting phosphorous ions to form a collector electrode contact region, photo-etching a base region and injecting boron ions to form a base electrode contact area, finally forming a SiGe HBT device, finally photo-etching a transmitting region lead hole, a base region lead holeand a collector region lead hole, metalizing, photo-etching leads, and forming an HBT integrated circuit with the thickness of the base region of 20 to 60nm. The technical method provided by the invention is compatible with the processing technique of the traditional CMOS integrated circuit, so that under the situation that the fund and the equipment investment are small, the SOI-based bipolar complementary metal-oxide semiconductor (BiCMOS) device and an integrated circuit are prepared, and the performance of the traditional analog and digital mixed integrated circuit is greatly improved.

Owner:陕西半导体先导技术中心有限公司

A double polycrystalline strained si BiCMOS integrated device and its preparation method

InactiveCN102738152BImprove performanceHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingHeterojunction bipolar transistorIntegrated devices

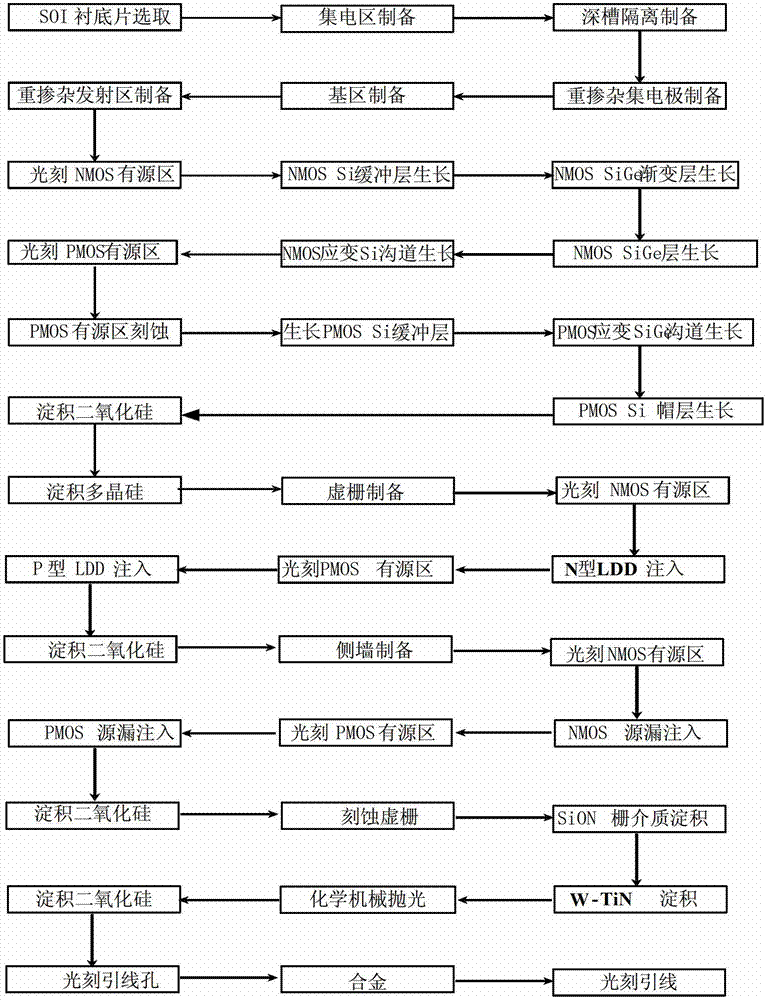

The invention discloses a double-polysilicon strained Si BiCMOS integrated device and a preparation method. The preparation method comprises growing an N-type Si epitaxial layer on an SOI (silicon on insulator) substrate to serve as the collector region of the bipolar device, preparing deep trench isolation, and sequentially preparing a base polysilicon, a base region and an emitter region to obtain a HBT (heterojunction bipolar transistor) device; etching an active region trench of an NMOS (N-channel metal oxide semiconductor) and PMOS (P-channel metal oxide semiconductor) device by lithography, continuously growing a Si buffer layer, a gradient SiGe layer, a fixed-component SiGe layer, an N-type strained Si channel layer and a Si buffer layer, a gradient SiGe layer, a fixed-component SiGe layer, a strained Si P-LDD (lightly doped drain) layer, a strained Si channe layer, a strained Si P-LDD layer, and a fixed-component SiGe layer in the active region trench of the NMOS and PMOS devices respectively, and preparing a drain and a gate to obtain the PMOS device; preparing a gate dielectric layer and gate polysilicon of the NMOS device to obtain the NMOS device; and preparing the strained Si BiCMOS integrated device and circuit with a MOS conductive channel of 22 to 45nm. According to the invention, the method can prepare the strained Si BiCMOS integrated device with enhanced performance at 600 to 800 DEG C by fully using the characteristics of mobility anisotropy of the strained Si material.

Owner:XIDIAN UNIV

Dual-strain bipolar complementary metal-oxide semiconductor (BiCMOS) integration device based on silicon on insulator (SOI) substrate and preparation method thereof

InactiveCN102810544ASuppress performance impactInhibition effectSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorIon

The invention discloses a dual-strain bipolar complementary metal-oxide semiconductor (BiCMOS) integration device based on a silicon on insulator (SOI) substrate and a preparation method thereof. The preparation method comprises following steps that a negative-silicon (N-Si) layer, a positive-silicon germanium (P-SiGe) layer and an N-Si layer continuously grow on the SOI substrate, a deep groove isolator is prepared, a collector zone shallow groove isolator and a base zone shallow groove isolator are prepared, a collector zone is photo-etched, phosphonium ions are injected to form a collector electrode, a base electrode and a transmitter electrode, and a SiGe heterojunction bipolar transistor (HBT) device is formed; a strain SiGe material grow on the substrate, an N-channel MOS (NMOS) device active region and a P-channel MOS (PMOS) device active region are formed, a pseudo grid is prepared, a source drain region of the NMOS and the PMOS devices is respectively generated in a self-aligning way, the pseudo grid is eliminated, a lanthanum oxide (La2O3) material is prepared in a pressing groove at the pseudo grid to form a grid medium and metal tungsten (W) to form a grid electrode, a lead is photo-etched, and a dual-strain plane BiCMOS integration device and a circuit based on the SOI substrate are formed. According to the method, the characteristic that a hole mobility of the strain SiGe material is higher than that of the bulk-Si material is adequately utilized to prepare the dual-strain plane BiCMOS integration circuit based on the SOI substrate, so that the performance of the existing analog and digital-analog mixed integrated circuit is greatly improved.

Owner:XIDIAN UNIV

Three-strained fully planar SOI (silicon on insulator) BiCMOS (bipolar complementary metal oxide semiconductor) integrated device and preparation method

InactiveCN102738174AImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricIon implantation

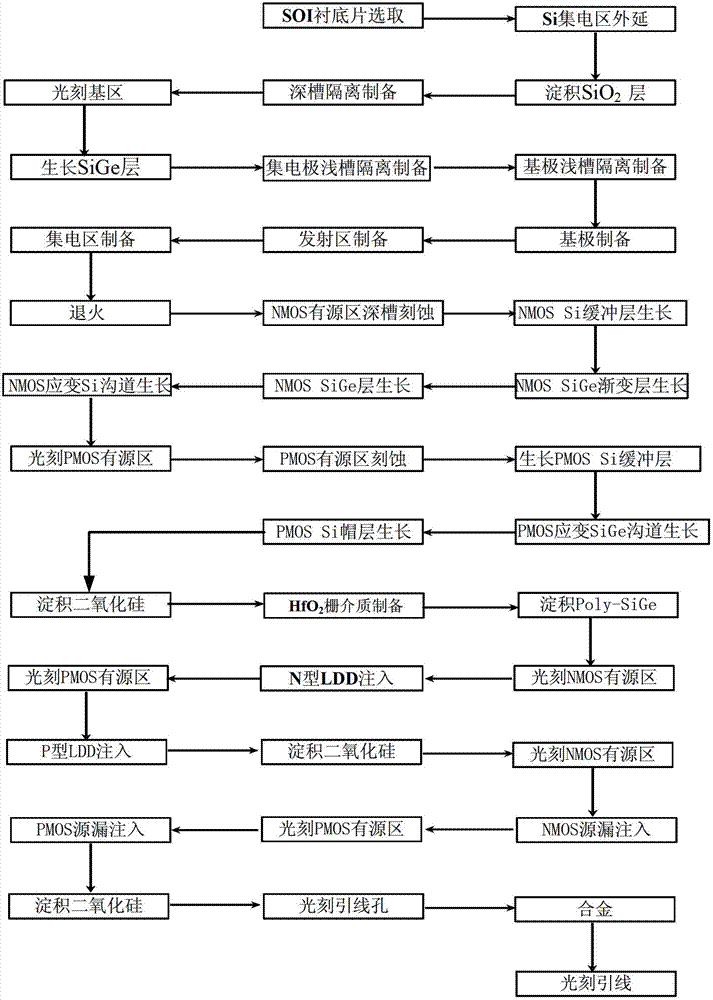

The invention discloses a three-strained fully planar SOI BiCMOS integrated device and a preparation method. The preparation method comprises continuously growing an N-Si layer, a P-SiGe layer and an N-Si layer on an SOI substrate, preparing deep trench isolation, etching a collector region, a base region and a shallow trench isolation region by lithography respectively, carrying out ion implantation, forming a collector, base and emitter contact region, and finally forming a SiGe HBT (heterojunction bipolar transistor) device; etching a trench in the active region of an NMOS (n-type metal oxide semiconductor) by lithography, growing four material layers in the trench, and preparing a gate dielectric layer and gate polysilicon on the active region of the NMOS device to obtain the NMOS device; etching a trench in the active region of a PMOS (p-type metal oxide semiconductor) by lithography, growing three material layers in the trench, and preparing a drain and a gate on the active region of the PMOS device to obtain the PMOS device; and etching leads by lithography to obtain the three-strained fully planar SOI BiCMOS integrated device and circuit. The preparation method provided by the invention adopts the self-alignment process, and fully utilizes the characteristics that the electron mobility of a tensile strained Si material is higher than that of a bulk Si material and that the hole mobility of a compressive strained SiGe material is higher than that of the bulk Si material so as to prepare the performance-enhanced three-strained fully planar SOI BiCMOS integrated circuit.

Owner:XIDIAN UNIV

A kind of double polycrystalline soi SiGe HBT integrated device and preparation method based on self-alignment process

InactiveCN102738178BImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingPhosphoniumIntegrated circuit

The invention is suitable for the technical field of semiconductor integrated circuit and provides a double-polysilicon SOI (Silicon On Insulator) SiGe HBT (Heterojunction Bipolar Transistor) integrated device based on self-aligned technology and a preparation method thereof. The preparation method comprises the following steps: growing N-type Si epitaxy on an SOI substrate; photoetching a shallow slot isolation region; preparing shallow slot isolation; etching and injecting phosphonium ions to form a collector contact region; depositing SiO2, P-Poly-Si, SiO2 and nitride in sequence; carrying out dry etching to form a nitride side wall; carrying out wet etching to form a base region window; selectively growing a SiGe base region; depositing N-type Poly-Si; then removing Poly-Si outside an emitter to form an HBT (Heterojunction Bipolar Transistor); and finally photoetching an emitter region, the base region and a collector region pin hole, metalizing, photoetching a lead wire to form an HBT integrated circuit in which the thickness of the base region is 20-60nm. The technique provided by the invention is compatible with the existing CMOS (Complementary Metal-Oxide-Semiconductor) integrated circuit processing technology, and can prepare the integrated circuit of a BiCMOS (Bipolar-Complementary Metal-Oxide-Semiconductor) device based on SOI under the condition of little capital and equipment investment so that the performance of the existing analog and digital-analog hybrid integrated circuit is greatly improved.

Owner:XIDIAN UNIV

A three-strain soi Si-based BiCMOS integrated device based on crystal plane selection and its preparation method

InactiveCN102751289BImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingHemt circuitsCrystal plane

The invention discloses a tri-strain SOI (Silicon On Insulator) Si based BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device based on crystal face selection and a preparation method thereof. The preparation method comprises the steps of: preparing a SOI substrate; continuously growing an N-Si layer, a P-SiGe layer and an N-Si layer and depositing a dielectric layer to prepare a shallow trench isolation region of a collecting region and a shallow trench isolation region of a base region; carrying out photo-etching on the collecting region and phosphorous ion injection, forming a collecting electrode contact region and a base electrode contact region and forming a SiGe HBT (Heterojunction Bipolar Transistor) device; etching the deep trench in an NMOS (N-channel Metal Oxide Semiconductor) region, selectively growing a strain Si epitaxial layer with the crystal face (100), and preparing a strain Si channel NMOS device; selectively growing a strain Si epitaxial layer with the crystal face (110) in an active region of a PMOS (P-channel Metal Oxide Semiconductor), and preparing a compression strain SiGe channel PMOS device; and forming the tri-strain SOI Si based BiCMOS integrated device based on crystal face selection and a circuit. According to the tri-strain SOI Si based BiCMOS integrated device based on crystal face selection and the preparation method of the tri-strain SOI Si based BiCMOS integrated device based on crystal face selection, a performance-enhanced planar BiCMOS integrated circuit is prepared based on the SOI substrate by means of characteristics that the electronic mobility of the strain Si material is higher than that of the body strain Si material and the hole mobility of the compression strain Si material is higher than that of the body strain Si material and the mobility is anisotropic adequately.

Owner:XIDIAN UNIV

Tri-polycrystal strain SiGe BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and preparation method

InactiveCN102820306ASuppress performance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingDielectricSoi substrate

The invention discloses a tri-polycrystal strain SiGe BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and a preparation method. The preparation method comprises the steps of: firstly, preparing an SOI (Silicon On Insulator) substrate; etching a bipolar device region; preparing a tri-polycrystal SiGe HBT (Heterojunction Bipolar Transistor) device in the region; then photoetching an MOS (Metal Oxide Semiconductor) active region; continuously growing an Si buffer layer, a strain SiGe layer and an intrinsic Si layer in the region; respectively forming active regions of an NMOS (N-channel Metal Oxide Semiconductor) device and a PMOS (P-channel Metal Oxide Semiconductor) device; depositing SiO2 and polycrystalline silicon on the active region of the MOS device; preparing a pseudo grid by etching; forming a light dope source drain and a source drain of the MOS device by a self-aligning process; then removing the pseudo grid; preparing grid dielectric lanthanum oxide and tungsten to form the grid; and finally metalizing and photoetching a lead to prepare the integrated device and a circuit. The preparation process provided by the the invention adopts the self-aligning process, and the light dope source drain structure is adopted in the MOS structure so that the influence of hot carriers on the performance of the device is effectively inhibited and the reliability of the device is improved.

Owner:XIDIAN UNIV

A kind of soi BJT dual-strain plane BiCMOS integrated device and its preparation method

InactiveCN102723340BImprove electrical performanceHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingComposite gridTin

The invention discloses an SOI (Silicon-On-Insulator)-BJT (Bipolar Junction Transistor) double-strain-plane Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device and a preparation method of the device. The preparation process is as follows: growing an N type Si epitaxial collector region on an SOI substrate sheet, preparing a deep-trench isolator, and manufacturing a conventional Si bipolar transistor in a bipolar device region; etching a deep trench in an active region of an MOS (Metal Oxide Semiconductor) device by utilizing a dry etching process, and respectively and selectively growing a P type Si layer, a P type SiGe gradual change layer, a P type SiGe layer, a P type strain Si layer which are taken as an active region of an NMOS (N-Channel Metal Oxide Semiconductor) device, an N type Si layer, an N type strain SiGe layer and an N type Si cap layer which are taken as an active region of a PMOS (P-Channel Metal Oxide Semiconductor) device in the trench in an epitaxial manner; and preparing a virtual grid electrode, respectively injecting LDD (Laser Detector Diode) of the MOS device, depositing SiO2, preparing a side wall, and conducting self alignment to form source drain of the NMOS device and the PMOS device; and etching a virtual grid, depositing a SiON grid dielectric layer and a W-TiN composite grid, and thus finally forming the Bi CMOS integrated device with the channel being 22-45nm. According to the method, the tensile strain Si with high electronic mobility and compressive strain SiGe with high hole mobility are respectively taken as conducting channels of the NMOS device and the PMOS device, so that the performances of the Bi CMOS integrated device and a circuit are improved greatly.

Owner:XIDIAN UNIV

Double-polysilicon planar SOI (silicon on insulator) BiCMOS (bipolar complementary metal oxide semiconductor) integrated device and preparation method

InactiveCN102738172AImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingP channelIntegrated circuit

The invention discloses a double-polysilicon planar SOI BiCMOS integrated device and a preparation method. The preparation method growing N-Si on a SOI substrate as the collector region of a bipolar device, etching a base region by lithography, growing P-SiGe, i-Si and i-Poly-Si on the base region, preparing deep trench isolation, and preparing an emitter, a base and a collector to obtain a SiGe HBT (heterojunction bipolar transistor) device; etching a trench on the active region of an NMOS (n-channel metal oxide semiconductor) device by lithography, and growing four material layers in the trench; etching a trench on the active region of a PMOS (p-channel metal oxide semiconductor) device, growing three material layers in the trench, and preparing a drain and a gate on the active region of MOS (metal oxide semiconductor) to obtain an MOS device; and etching leads by lithography to obtain the double-polysilicon planar SOI BiCMOS integrated device and circuit. According to the invention, the double-polysilicon planar SOI BiCMOS integrated circuit prepared by the method is enhanced in performance by fully utilizing the characteristics that the electron mobility of a tensile strained Si material is higher than that of a bulk Si material and that the hole mobility of a compressive strained SiGe material is higher than that of the bulk Si material.

Owner:XIDIAN UNIV

Double poly-crystal plane strain BiCMOS integrated device based on SOI (Silicon On Insulator) substrate and preparation method

InactiveCN102820307AImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorHeterojunction bipolar transistor

The invention discloses a double poly-crystal plane strain BiCMOS integrated device based on a SOI (Silicon On Insulator) substrate and a preparation method. The preparation method comprises the following steps: preparing a deep slot isolator on the SOI substrate; forming a collector contact region, a nitride side wall and a base region window; growing SiGe and Poly-Si on the base region, thereby forming a SiGe HBT (Heterojunction Bipolar Transistor) device; etching a slot on a NMOS (N-channel Metal Oxide Semiconductor) device active region, preparing a grid dielectric layer and a grid poly-crystal on the NMOS device active region, thereby forming a NMOS device; etching a slot on a PMOS (P-channel Metal Oxide Semiconductor) device active region and preparing a drain and a grid on the PMOS device active region, thereby forming a PMOS device; and photo-etching a lead, thereby preparing a BiCMOS integrated device and a circuit. According to the preparation method, a BiCMOS integrated circuit with an enhanced property is prepared by adopting a self-aligning technology and fully utilizing the characteristics that the electronic mobility of a spreading strain Si material is higher than that of a semiconductor Si material and the hole mobility of a compressive strain SiGe material is higher than that of the semiconductor Si material.

Owner:XIDIAN UNIV

A kind of bipolycrystalline planar soi BiCMOS integrated device and its preparation method

InactiveCN102738172BImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingIntegrated circuitHeterojunction bipolar transistor

The invention discloses a double-polysilicon planar SOI BiCMOS integrated device and a preparation method. The preparation method growing N-Si on a SOI substrate as the collector region of a bipolar device, etching a base region by lithography, growing P-SiGe, i-Si and i-Poly-Si on the base region, preparing deep trench isolation, and preparing an emitter, a base and a collector to obtain a SiGe HBT (heterojunction bipolar transistor) device; etching a trench on the active region of an NMOS (n-channel metal oxide semiconductor) device by lithography, and growing four material layers in the trench; etching a trench on the active region of a PMOS (p-channel metal oxide semiconductor) device, growing three material layers in the trench, and preparing a drain and a gate on the active region of MOS (metal oxide semiconductor) to obtain an MOS device; and etching leads by lithography to obtain the double-polysilicon planar SOI BiCMOS integrated device and circuit. According to the invention, the double-polysilicon planar SOI BiCMOS integrated circuit prepared by the method is enhanced in performance by fully utilizing the characteristics that the electron mobility of a tensile strained Si material is higher than that of a bulk Si material and that the hole mobility of a compressive strained SiGe material is higher than that of the bulk Si material.

Owner:XIDIAN UNIV

Double poly-crystal plane strain BiCMOS integrated device based on SOI (Silicon On Insulator) substrate and preparation method

InactiveCN102820307BImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingHemt circuitsEngineering

Owner:XIDIAN UNIV

Tri-polycrystal SOI SiGe HBT (Heterojunction Bipolar Transistor) planar integrated device and preparation method thereof

InactiveCN102916040AImprove reverse breakdown voltageExcellent characteristic frequencySemiconductor/solid-state device manufacturingSemiconductor devicesIonCMOS

The invention is suitable for the field of semiconductor integrated circuit, and provides a tri-polycrystal SOI (Silicon-On-Insulator) SiGe HBT (Heterojunction Bipolar Transistor) integrated device and a preparation method thereof. The preparation method comprises the following steps: continuously growing N-Si, P-SiGe, i-Si, i-Poly-Si on an SOI substrate; depositing a dielectric layer; preparing a shallow-trench isolator; photoetching a collecting zone shallow-trench isolation region; preparing a collecting zone shallow-trench isolator; etching and depositing the dielectric layer; photoetching a base region shallow-trench isolation region; preparing a base region shallow-trench isolator; photoetching a collector and implanting phosphonium ions; photoetching a base electrode and implanting boron ions; photoetching an emitter and implanting phosphonium ions; forming the contact regions of the collector, the base electrode and the emitter; and finally forming the HBT device to compose HBT integrated circuit in which the thickness of the base region is 20-60nm. The technique provided by the invention is compatible with the processing technique of the existing CMOS integrated circuit; under the condition of very few fund and equipment investments, the BiCMOS integrated device and circuit based on SOI can be prepared so that the performance of the existing analog and digital-analog hybrid integrated circuit is greatly improved.

Owner:XIDIAN UNIV

Strain SiGe plane Si-based BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device on basis of SOI (Silicon On Insulator) substrate and preparation method

InactiveCN102738176APerformance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionP channel

The invention discloses a strain SiGe plane Si-based BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device on the basis of a SOI (Silicon On Insulator) substrate and a preparation method. The preparation method has the following preparation process of: growing an N-Si layer on the SOI substrate to form a bipolar device collector region, photoetching a base region, regionally growing a P-SiGe layer, an i-Si layer and an i-Poly-Si layer in the base region, preparing a deep-trench isolation, forming an emitting electrode, a base electrode and a collector electrode and forming a SiGe HBT (Heterojunction Bipolar Trthissistor) device; and growing a strain SiGe material on the substrate, forming active regions of NMOS (N-channel Metal Oxide Semiconductor) and PMOS (P-channel Metal Oxide Semiconductor) devices, preparing a pseudo-gate, carrying out self-aligning to generate source drain regions of the NMOS and PMOS devices, removing the pseudo-gate, preparing a grid electrode and photoetching leads to form the strain SiGe plane Si-based BiCMOS integrated device on the basis of the SOI substrate and a circuit. According to the method, the SOI SiGe BiCMOS integrated circuit is prepared by sufficiently utilizing the characteristic that the hole mobility of a SiGe material is higher than that of a common Si material, so that the performance of the existing analog and analog-digital mixed integrated circuit is greatly improved.

Owner:XIDIAN UNIV

Tri-polycrystal strain SiGe BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device and preparation method

InactiveCN102820306BHigh frequencyImprove current drive capabilitySolid-state devicesSemiconductor/solid-state device manufacturingDielectricHemt circuits

Owner:XIDIAN UNIV

A hybrid crystal plane plane strain bicmos integrated device and preparation method

InactiveCN102738165BReduce power consumptionImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingHemt circuitsEngineering

The invention discloses a manufacturing method of a mixed crystal plane strain BiCMOS (Bipolar Complementary Metal Oxide Semiconductor Transistor) integrated device and a circuit. The method comprises the steps of manufacturing an SOI (Silicon on Insulator) substrate, with the base material of the upper layer being a (110) crystal face, and the base material of the lower layer being a (100) crystal face; manufacturing a conventional Si (Silicon) bipolar transistor in a bipolar device area; selectively growing a strain Si epitaxial layer with the crystal face as (100) in an NMOS (N-channel Metal Oxide Semiconductor) device area to manufacture a strain Si channel NMOS device; selectively growing a strain SiGe (Silicon Germanium) epitaxial layer with the crystal face as (110) in a PMOS (P-channel Metal Oxide Semiconductor) device active area to manufacture a compression strain SiGe channel PMOS device of a channel; and photoetching a lead, so as to form the mixed crystal plane strain BiCMOS integrated device with a 22-45nm MOS (Metal Oxide Semiconductor) device conducting channel. According to the invention, the characteristics that the electron mobility of a tensile strain Si material is higher than the electron mobility of a body Si material, and the electron mobility of a compression strain SiGe material is higher than the electron mobility of the body Si material, and the characteristic of mobility aeolotropy are made full use of to manufacture the mixed crystal plane strain BiCMOS integrated device and the circuit with enhanced performances based on the SOI substrate.

Owner:XIDIAN UNIV

A strained SiGe planar Si-based Bicmos integrated device based on SOI substrate and its preparation method

InactiveCN102738176BPerformance impactHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionP channel

The invention discloses a strain SiGe plane Si-based BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device on the basis of a SOI (Silicon On Insulator) substrate and a preparation method. The preparation method has the following preparation process of: growing an N-Si layer on the SOI substrate to form a bipolar device collector region, photoetching a base region, regionally growing a P-SiGe layer, an i-Si layer and an i-Poly-Si layer in the base region, preparing a deep-trench isolation, forming an emitting electrode, a base electrode and a collector electrode and forming a SiGe HBT (Heterojunction Bipolar Trthissistor) device; and growing a strain SiGe material on the substrate, forming active regions of NMOS (N-channel Metal Oxide Semiconductor) and PMOS (P-channel Metal Oxide Semiconductor) devices, preparing a pseudo-gate, carrying out self-aligning to generate source drain regions of the NMOS and PMOS devices, removing the pseudo-gate, preparing a grid electrode and photoetching leads to form the strain SiGe plane Si-based BiCMOS integrated device on the basis of the SOI substrate and a circuit. According to the method, the SOI SiGe BiCMOS integrated circuit is prepared by sufficiently utilizing the characteristic that the hole mobility of a SiGe material is higher than that of a common Si material, so that the performance of the existing analog and analog-digital mixed integrated circuit is greatly improved.

Owner:XIDIAN UNIV

Tri-strain SOI (Silicon On Insulator) Si based BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device based on crystal face selection and preparation method thereof

InactiveCN102751289AImprove reverse breakdown voltageExcellent characteristic frequencySolid-state devicesSemiconductor/solid-state device manufacturingElectrode ContactIon implantation

The invention discloses a tri-strain SOI (Silicon On Insulator) Si based BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor Transistor) integrated device based on crystal face selection and a preparation method thereof. The preparation method comprises the steps of: preparing a SOI substrate; continuously growing an N-Si layer, a P-SiGe layer and an N-Si layer and depositing a dielectric layer to prepare a shallow trench isolation region of a collecting region and a shallow trench isolation region of a base region; carrying out photo-etching on the collecting region and phosphorous ion injection, forming a collecting electrode contact region and a base electrode contact region and forming a SiGe HBT (Heterojunction Bipolar Transistor) device; etching the deep trench in an NMOS (N-channel Metal Oxide Semiconductor) region, selectively growing a strain Si epitaxial layer with the crystal face (100), and preparing a strain Si channel NMOS device; selectively growing a strain Si epitaxial layer with the crystal face (110) in an active region of a PMOS (P-channel Metal Oxide Semiconductor), and preparing a compression strain SiGe channel PMOS device; and forming the tri-strain SOI Si based BiCMOS integrated device based on crystal face selection and a circuit. According to the tri-strain SOI Si based BiCMOS integrated device based on crystal face selection and the preparation method of the tri-strain SOI Si based BiCMOS integrated device based on crystal face selection, a performance-enhanced planar BiCMOS integrated circuit is prepared based on the SOI substrate by means of characteristics that the electronic mobility of the strain Si material is higher than that of the body strain Si material and the hole mobility of the compression strain Si material is higher than that of the body strain Si material and the mobility is anisotropic adequately.

Owner:XIDIAN UNIV

BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device on basis of SOI (Silicon On Insulator) substrate and preparation method

InactiveCN102738175BImprove performanceHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionGate dielectric

The invention discloses a BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) integrated device on the basis of a SOI (Silicon On Insulator) substrate and a preparation method. The preparation method comprises the following steps of: firstly, continuously growing an N-Si layer, a P-SiGe layer and an N-Si layer on the SOI substrate, depositing a medium layer, preparing a collector region shallow-trench isolation and a base region shallow-trench isolation, photoetching a collector region and implanting phosphorous ions into the collector region to form a collector electrode contact region, photoetching a base region and implanting boron ions into the base region to form a base electrode contact region and forming a SiGe HBT (Heterojunction Bipolar Trthissistor) device; photoetching active region grooves of NMOS (N-channel Metal Oxide Semiconductor) and PMOS (P-channel Metal Oxide Semiconductor) devices, respectively and continuously growing a Si buffer layer, a gradient SiGe layer, a fixed component SiGe layer and an N-type strain Si groove layer and a Si buffer layer, a gradient SiGe layer, a fixed component SiGe layer, a strain Si P-LDD (Laser Detector Diode) layer, a strain Si groove layer, a strain Si P-LDD layer and the like in the active region grooves and preparing a drain electrode and a grid electrode of the PMOS device to form the PMOS device; and preparing a gate dielectric layer and gate polycrystal of the NMOS device to form the NMOS device so as to form the BiCMOS integrated device and a circuit. According to the invention, the performance-enhanced BiCMOS integrated circuit is prepared at a temperature of 600 to 800 DEG C by sufficiently utilizing the characteristic of anisotropism of the mobility ratio of the strain Si material.

Owner:XIDIAN UNIV

A kind of three-polycrystalline soi SiGe HBT planar integrated device and its preparation method

InactiveCN102916040BImprove reverse breakdown voltageExcellent characteristic frequencySemiconductor/solid-state device manufacturingSemiconductor devicesPhosphoniumIntegrated circuit

The invention is suitable for the field of semiconductor integrated circuit, and provides a tri-polycrystal SOI (Silicon-On-Insulator) SiGe HBT (Heterojunction Bipolar Transistor) integrated device and a preparation method thereof. The preparation method comprises the following steps: continuously growing N-Si, P-SiGe, i-Si, i-Poly-Si on an SOI substrate; depositing a dielectric layer; preparing a shallow-trench isolator; photoetching a collecting zone shallow-trench isolation region; preparing a collecting zone shallow-trench isolator; etching and depositing the dielectric layer; photoetching a base region shallow-trench isolation region; preparing a base region shallow-trench isolator; photoetching a collector and implanting phosphonium ions; photoetching a base electrode and implanting boron ions; photoetching an emitter and implanting phosphonium ions; forming the contact regions of the collector, the base electrode and the emitter; and finally forming the HBT device to compose HBT integrated circuit in which the thickness of the base region is 20-60nm. The technique provided by the invention is compatible with the processing technique of the existing CMOS integrated circuit; under the condition of very few fund and equipment investments, the BiCMOS integrated device and circuit based on SOI can be prepared so that the performance of the existing analog and digital-analog hybrid integrated circuit is greatly improved.

Owner:XIDIAN UNIV

A mixed crystal plane strain Si vertical channel Bicmos integrated device and its preparation method

InactiveCN102723341BImprove mobilityHigh frequencySolid-state devicesSemiconductor/solid-state device manufacturingCrystal planeP channel

The invention discloses a Bi CMOS (Complementary Metal-Oxide-Semiconductor) integrated device with a mixed crystal plane and a Si vertical channel and a preparation method of the device. The preparation process is as follows: preparing an SOI (Silicon-On-Insulator) substrate, taking upper-layer base material as a crystal plane (100) and taking lower-layer base material as a crystal plane (110); growing N type Si epitaxy on a substrate sheet to prepare a deep-trench isolator, and manufacturing a conventional Si bipolar transistor in a bipolar device region; etching a deep trench in an active region of a PMOS (P-Channel Metal Oxide Semiconductor) device, selectively growing an active layer of a strain Si PMOS device, and preparing a compressive strain PMOS device with a vertical channel on the active layer; and etching a deep trench in an active region of an NMOS (N-Channel Metal Oxide Semiconductor) device, selectively growing an active layer of a strain Si NMOS device, and preparing a tensile strain NMOS device with a plane channel on an epitaxial layer. According to the Bi CMOS integrated device with the mixed crystal plane and the Si vertical channel and the preparation method, the characteristics that the mobility ratio of strain Si material is higher than the stress of body Si material and the strain Si material, and the mobility ratio is anisotropic are utilized, and based on the SOI substrate, the Bi CMOS integrated device with the mixed crystal plane and the Si vertical channel and a circuit, which are excellent in performance, are prepared.

Owner:XIDIAN UNIV