A kind of three-polycrystalline soi SiGe HBT planar integrated device and its preparation method

A technology of integrated devices and collector regions, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve the problems of difficult process, low mechanical strength and high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

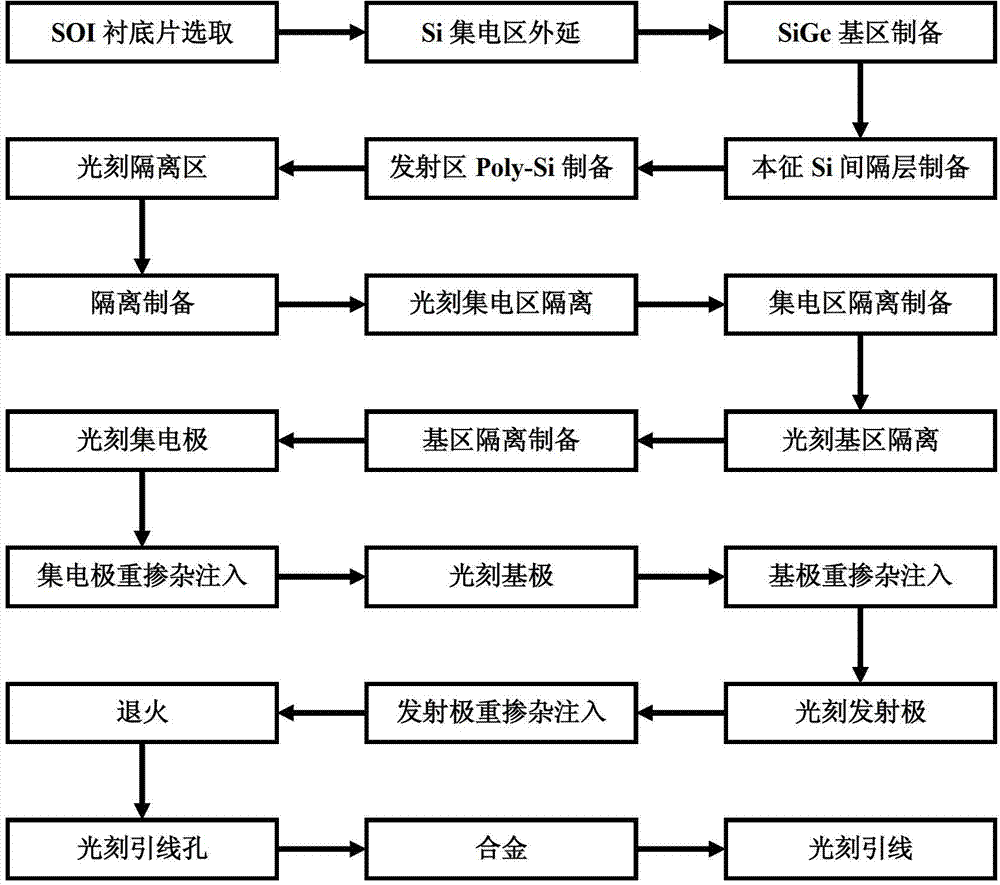

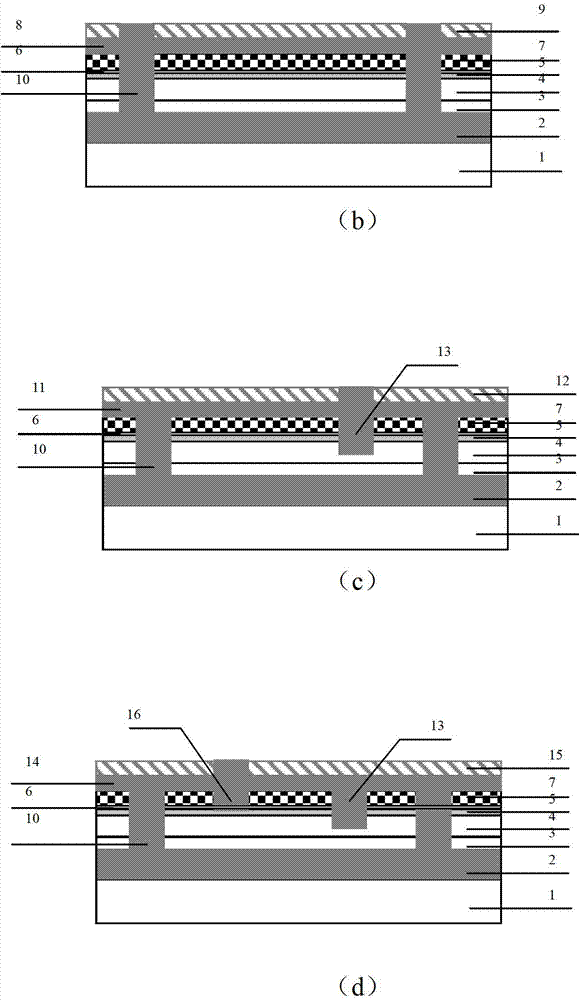

[0077] Embodiment 1: preparation of a three-polycrystalline SOI SiGe HBT planar integrated device and circuit method with a base thickness of 20nm, the specific steps are as follows:

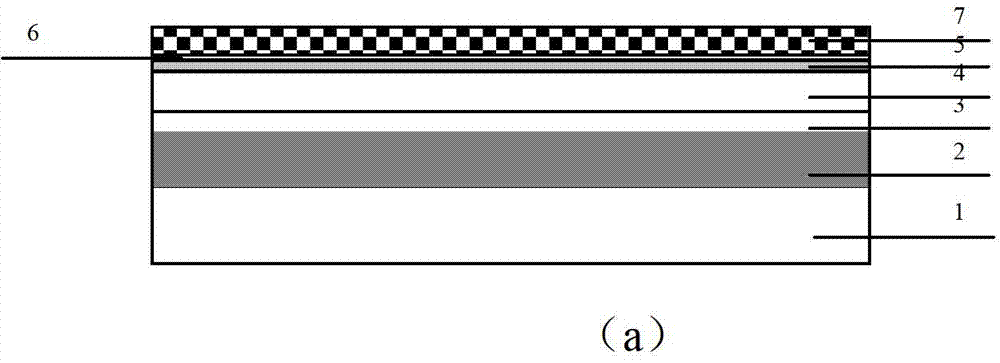

[0078] Step 1, epitaxial material preparation, such as figure 2 (a) shown.

[0079] (1a) Select an SOI substrate, the support material 1 of the lower layer of the substrate is Si, and the middle layer 2 is SiO 2 , the thickness is 150nm, and the upper layer material 3 has a doping concentration of 1×10 16 cm -3 N-type Si with a thickness of 100nm;

[0080] (1b) Using the method of chemical vapor deposition (CVD), grow a layer of N-type epitaxial Si layer 4 with a thickness of 50nm on the upper Si material at 600°C as the collector region, and the doping concentration of this layer is 1 ×10 16 cm -3 ;

[0081] (1c) A SiGe layer 5 with a thickness of 20nm is grown on the substrate at 600°C by chemical vapor deposition (CVD). As the base region, the Ge composition of this layer is 15%, and ...

Embodiment 2

[0115] Embodiment 2: The preparation of a three-polycrystalline SOI SiGe HBT planar integrated device and circuit method with a base thickness of 40nm, the specific steps are as follows:

[0116] Step 1, epitaxial material preparation, such as figure 2 (a) shown.

[0117] (1a) Select an SOI substrate, the support material 1 of the lower layer of the substrate is Si, and the middle layer 2 is SiO 2 , the thickness is 300nm, and the upper material 3 has a doping concentration of 5×10 16 cm -3 N-type Si with a thickness of 120nm;

[0118] (1b) Using the method of chemical vapor deposition (CVD), grow an N-type epitaxial Si layer 4 with a thickness of 80nm on the upper Si material at 700°C as the collector region, and the doping concentration of this layer is 5 ×10 16 cm -3 ;

[0119] (1c) Using chemical vapor deposition (CVD), at 700°C, grow a layer of SiGe layer 5 with a thickness of 40nm on the substrate, as the base region, the Ge composition of this layer is 20%, and ...

Embodiment 3

[0153] Embodiment 3: preparation of a three-polycrystalline SOI SiGe HBT planar integrated device and circuit method with a base thickness of 60 nm, the specific steps are as follows:

[0154] Step 1, epitaxial material preparation, such as figure 2 (a) shown.

[0155] (1a) Select an SOI substrate, the support material 1 of the lower layer of the substrate is Si, and the middle layer 2 is SiO 2 , the thickness is 400nm, and the upper material 3 has a doping concentration of 1×10 17 cm -3 N-type Si with a thickness of 150nm;

[0156] (1b) Using the method of chemical vapor deposition (CVD), grow a layer of N-type epitaxial Si layer 4 with a thickness of 100 nm on the upper Si material at 750 ° C, as the collector region, and the doping concentration of this layer is 1 ×10 17 cm -3 ;

[0157] (1c) Using the chemical vapor deposition (CVD) method, at 750°C, grow a layer of SiGe layer 5 with a thickness of 60nm on the substrate, as the base region, the Ge composition of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More