A kind of double polycrystalline soi SiGe HBT integrated device and preparation method based on self-alignment process

A self-aligned process and integrated device technology, which is applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., and can solve the problems of lack of wide application and development, incompatibility of Si process, and more complicated preparation process than Si process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

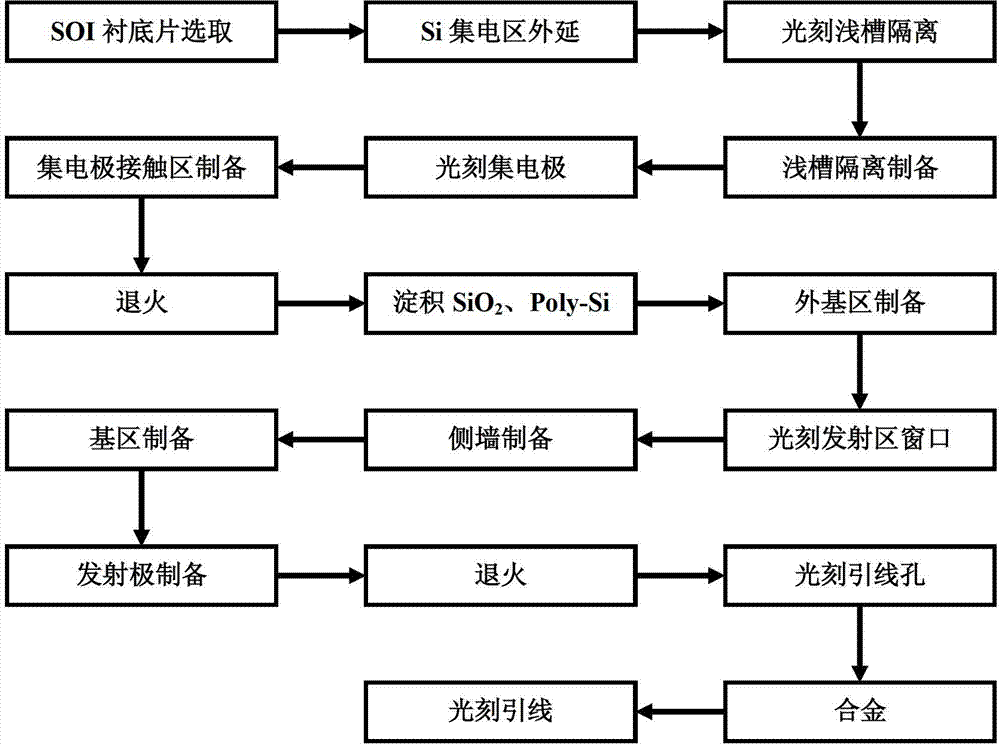

[0075] Embodiment 1: The method for preparing a double-polycrystalline SOI SiGe HBT integrated device and circuit with a base thickness of 20nm by using a self-alignment process provided, the specific steps are as follows:

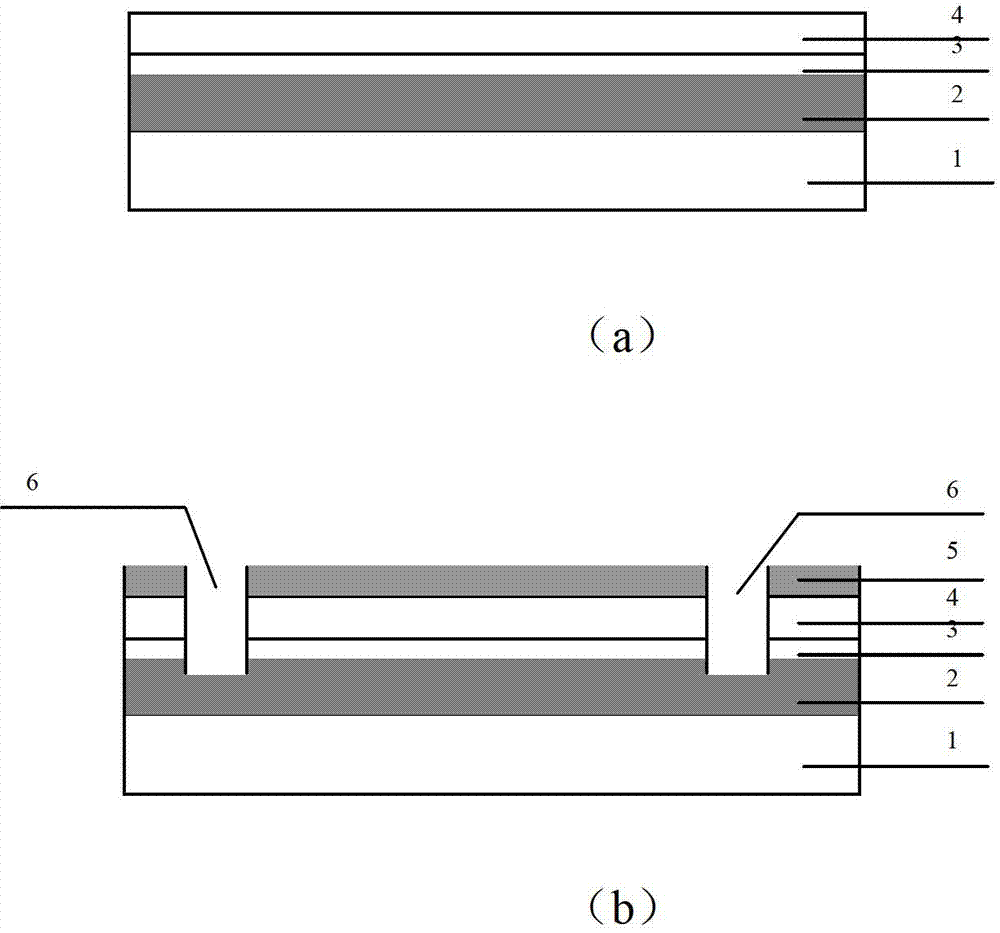

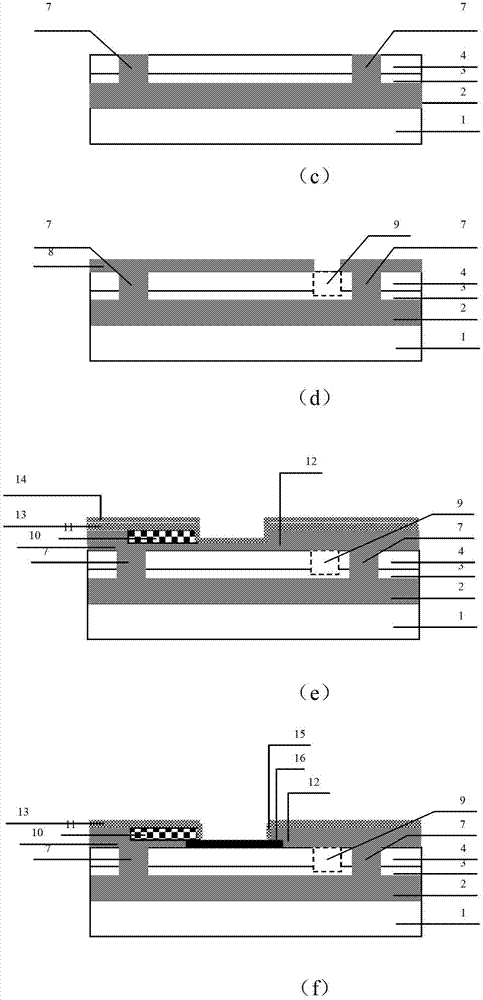

[0076] Step 1, epitaxial growth, such as figure 2 (a) shown.

[0077] (1a) Select the SOI substrate sheet, the support material 1 of the lower layer of the substrate is Si, and the intermediate layer 2 is SiO 2 , the thickness is 150nm, and the upper layer material 3 has a doping concentration of 1×10 16 cm -3 N-type Si with a thickness of 100nm;

[0078] (1b) Using the chemical vapor deposition (CVD) method, at 600 ° C, grow a layer of N-type epitaxial Si layer 4 with a thickness of 50 nm on the upper Si material, as the collector region, and the doping concentration of this layer is 1 ×10 16 cm -3 .

[0079] Step 2, shallow trench isolation preparation, such as figure 2 (b), (c) shown.

[0080] (2a) Deposit a layer of SiO with a thickness of 3...

Embodiment 2

[0109] Embodiment 2: The method for preparing a double-polycrystalline SOISiGeHBT integrated device and circuit with a base thickness of 40 nm by using a self-alignment process is provided, and the specific steps are as follows:

[0110] Step 1, epitaxial growth, such as figure 2 (a) shown.

[0111] (1a) Select the SOI substrate sheet, the support material 1 of the lower layer of the substrate is Si, and the intermediate layer 2 is SiO 2 , the thickness is 300nm, and the upper material 3 has a doping concentration of 5×10 16 cm -3 N-type Si with a thickness of 120nm;

[0112] (1b) Using the chemical vapor deposition (CVD) method, at 700 ° C, grow an N-type epitaxial Si layer 4 with a thickness of 80 nm on the upper Si material as the collector region, and the doping concentration of this layer is 5 ×10 16 cm -3 .

[0113] Step 2, shallow trench isolation preparation, such as figure 2 (b), (c) shown.

[0114] (2a) Deposit a layer of SiO with a thickness of 400nm on t...

Embodiment 3

[0143] Embodiment 3: The method for preparing a dual-polycrystalline SOI SiGeHBT integrated device and circuit with a base thickness of 60 nm by using a self-alignment process is provided, and the specific steps are as follows:

[0144] Step 1, epitaxial growth, such as figure 2 (a) shown.

[0145] (1a) Select the SOI substrate sheet, the support material 1 of the lower layer of the substrate is Si, and the intermediate layer 2 is SiO 2 , the thickness is 400nm, and the upper material 3 has a doping concentration of 1×10 17 cm -3 N-type Si with a thickness of 150nm;

[0146] (1b) Using the chemical vapor deposition (CVD) method, at 750 ° C, grow a layer of N-type epitaxial Si layer 4 with a thickness of 100 nm on the upper Si material, as the collector region, and the doping concentration of this layer is 1 ×10 17 cm -3 .

[0147] Step 2, shallow trench isolation preparation, such as figure 2 (b), (c) shown.

[0148] (2a) Deposit a layer of SiO with a thickness of 5...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More