Double poly-crystal plane strain BiCMOS integrated device based on SOI (Silicon On Insulator) substrate and preparation method

A plane strain, integrated device technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve the problems of difficult preparation of large-diameter single crystals, poor heat dissipation performance, and low mechanical strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

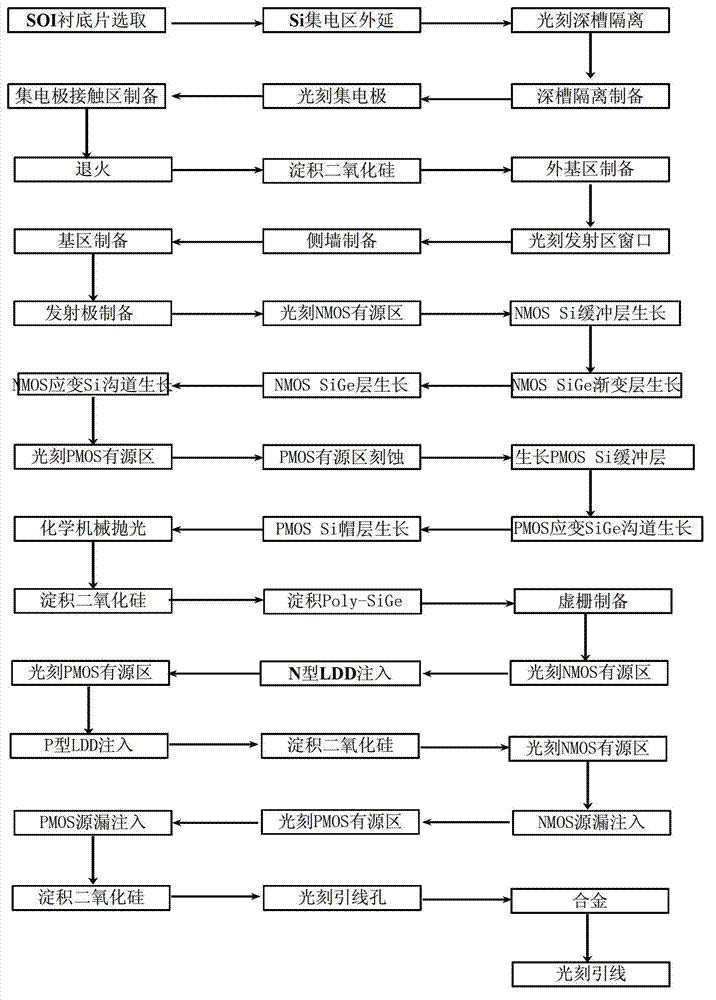

Method used

Image

Examples

Embodiment 1

[0111] Embodiment 1: A self-aligned process is used to prepare a dual-polycrystalline plane-strain BiCMOS integrated device and circuit based on an SOI substrate with a conductive channel of 22nm. The specific steps are as follows:

[0112] Step 1, epitaxial growth.

[0113] (1a) Select the SOI substrate, the support material of the lower layer of the substrate is Si, and the middle layer is SiO 2 , with a thickness of 150nm, and the upper material is doped with a concentration of 1×10 16 cm -3 N-type Si with a thickness of 100nm;

[0114] (1b) Using chemical vapor deposition (CVD), grow a layer of N-type epitaxial Si layer with a thickness of 50nm on the upper Si material at 600°C, as the collector region, and the doping concentration of this layer is 1× 10 16 cm -3 .

[0115] Step 2, isolation area preparation.

[0116] (2a) Deposit a layer of SiO with a thickness of 300nm on the surface of the epitaxial Si layer at 600°C by chemical vapor deposition (CVD). 2 layer; ...

Embodiment 2

[0169] Embodiment 2: A self-aligned process is used to prepare a dual-polycrystalline plane-strain BiCMOS integrated device and circuit based on an SOI substrate with a conductive channel of 30 nm. The specific steps are as follows:

[0170] Step 1, epitaxial growth.

[0171] (1a) Select the SOI substrate, the support material of the lower layer of the substrate is Si, and the middle layer is SiO 2 , with a thickness of 300nm, and the upper material is doped with a concentration of 5×10 16 cm -3 N-type Si with a thickness of 120nm;

[0172] (1b) Using chemical vapor deposition (CVD), grow an N-type epitaxial Si layer with a thickness of 80nm on the upper Si material at 700°C as the collector region, and the doping concentration of this layer is 5× 10 16 cm -3 .

[0173] Step 2, isolation area preparation.

[0174] (2a) Deposit a layer of SiO with a thickness of 400nm on the surface of the epitaxial Si layer at 700°C by chemical vapor deposition (CVD). 2 layer;

[0175...

Embodiment 3

[0227] Embodiment 3: A dual-polycrystalline plane-strain BiCMOS integrated device and circuit based on an SOI substrate with a conductive channel of 45nm prepared by a self-alignment process, the specific steps are as follows:

[0228] Step 1, epitaxial growth.

[0229] (1a) Select the SOI substrate, the support material of the lower layer of the substrate is Si, and the middle layer is SiO 2 , with a thickness of 400nm, and the upper material is doped with a concentration of 1×10 17 cm -3 N-type Si with a thickness of 150nm;

[0230] (1b) Using the method of chemical vapor deposition (CVD), grow a layer of N-type epitaxial Si layer with a thickness of 100nm on the upper layer of Si material at 750°C, as the collector region, and the doping concentration of this layer is 1× 10 17 cm -3 .

[0231] Step 2, the implementation method of isolation area preparation is:

[0232] (2a) Deposit a layer of SiO with a thickness of 500nm on the surface of the epitaxial Si layer at 8...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More