Error-free adder based on random calculation

A random calculation and adder technology, applied in CAD circuit design and other directions, can solve problems such as inability to meet high-precision scenarios, uncontrollable calculation errors, and low accuracy of calculation units, saving resources and power consumption, reducing resources and power consumption. , easy to achieve effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The core of the present invention is that the adder designed based on the random calculation method can be error-free and infinitely cascaded, the positions of "0" and "1" in the input sequence can be arbitrary, and the FPGA implementation of the adder is given.

[0029] Below in conjunction with accompanying drawing, specifically illustrate the present invention:

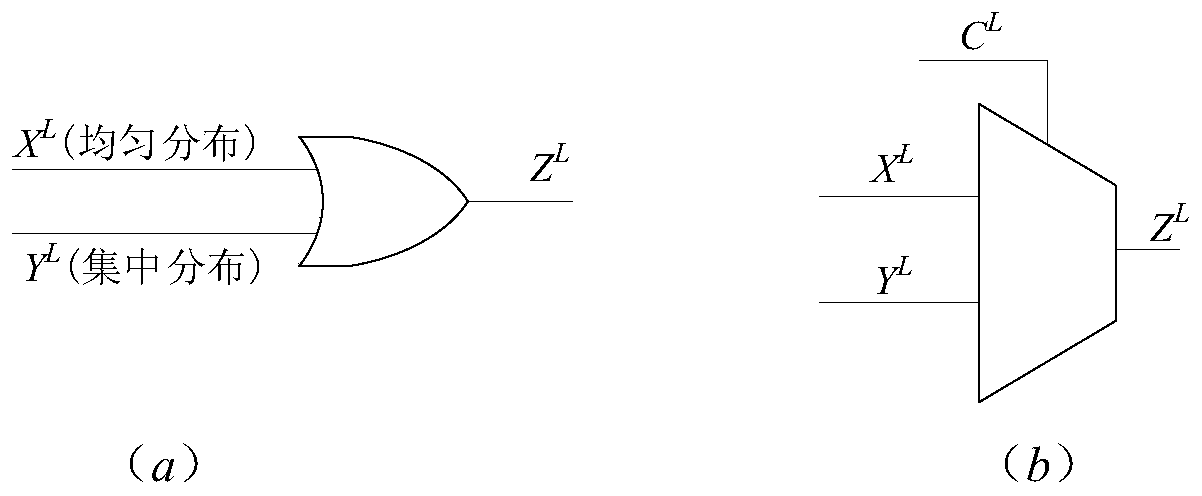

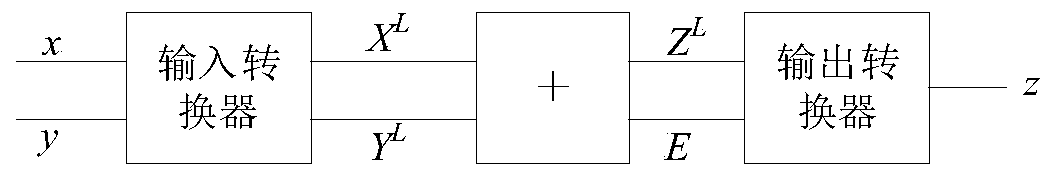

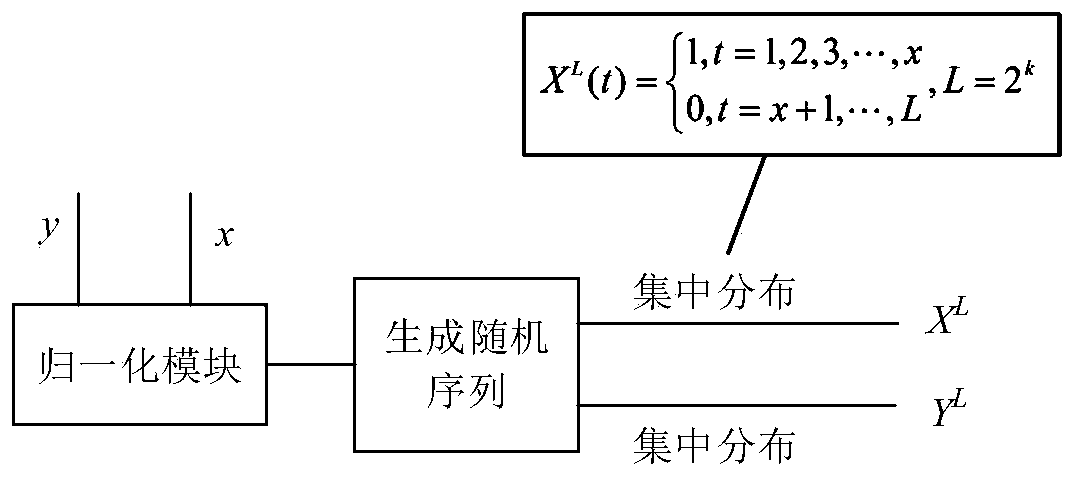

[0030] The functional function of the two-input adder is z=x+y, where x and y represent input data, and z is the output of the adder. The input data binary bit width is k bit. A traditional random adder consists of, for example, figure 1 The OR gate shown in (a) or as figure 1 The multi-way gate shown in (b) realizes, wherein the random adder that realizes by OR gate requires that two-way input random sequence one road is centralized distribution, another way is uniform distribution; And the random addition that is realized by multi-way gate device contains uncertainty. Errors will occur in the calculati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More