A non-volatile memory processing circuit and method

A technology of non-volatile memory and processing circuit, which is applied in the field of memory processing and can solve the problems of low reading accuracy of storage unit data and reading errors of storage unit data.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

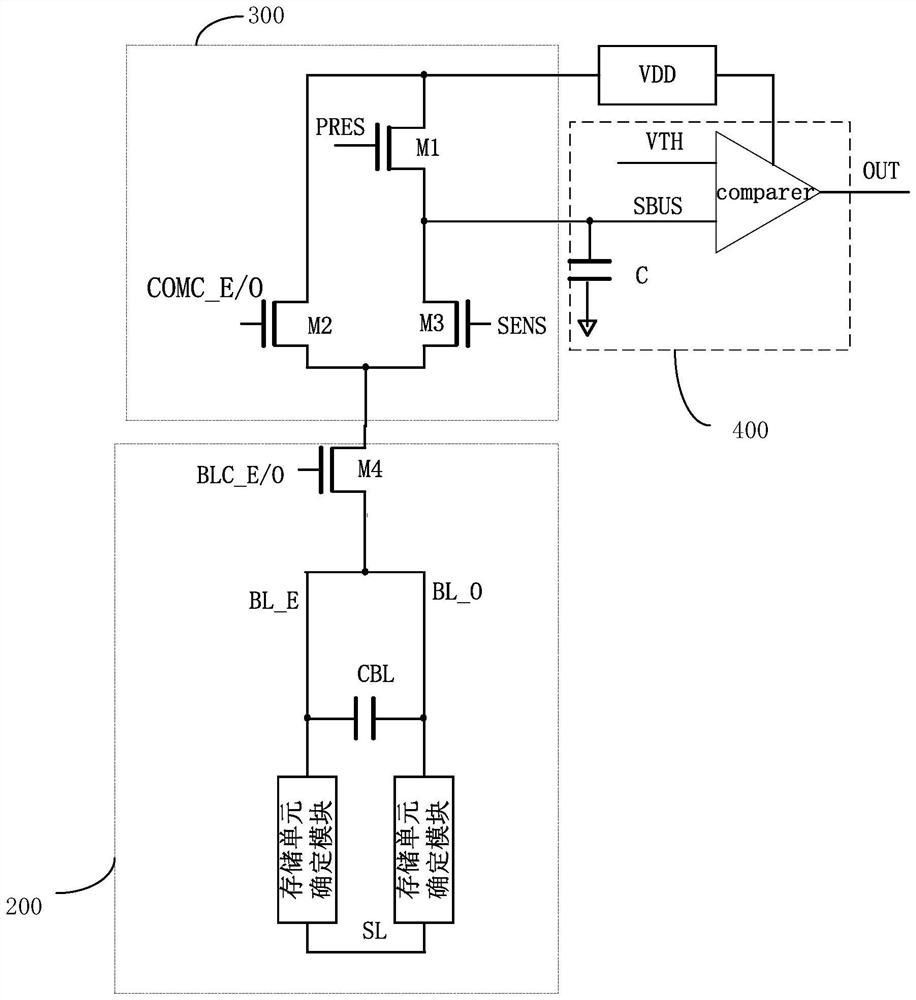

[0055] refer to figure 1 , shows a non-volatile memory processing circuit, which may specifically include: a charging circuit 300 , a comparison circuit 400 , and a storage unit selection circuit 200 .

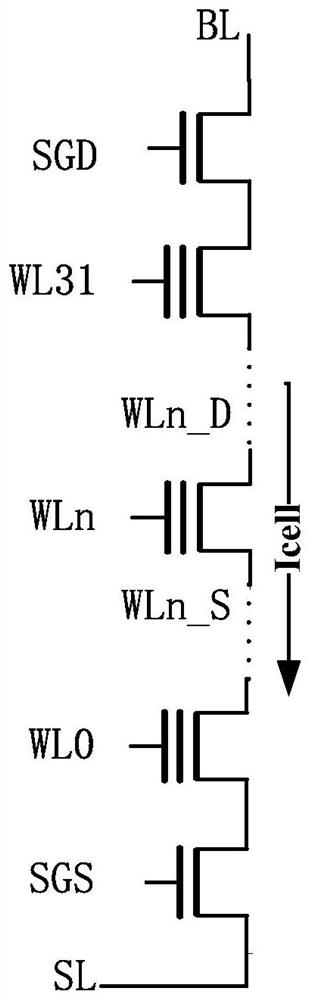

[0056]Wherein, the memory cell selection circuit includes at least one pair of memory cell strings; each pair of memory cell strings includes a first memory cell string and a second memory cell string, and the bit line BLO of the first memory cell string and the A capacitor CBL is connected between the bit lines BLE of the second memory cell string; each of the memory cell strings is connected to a source line SL.

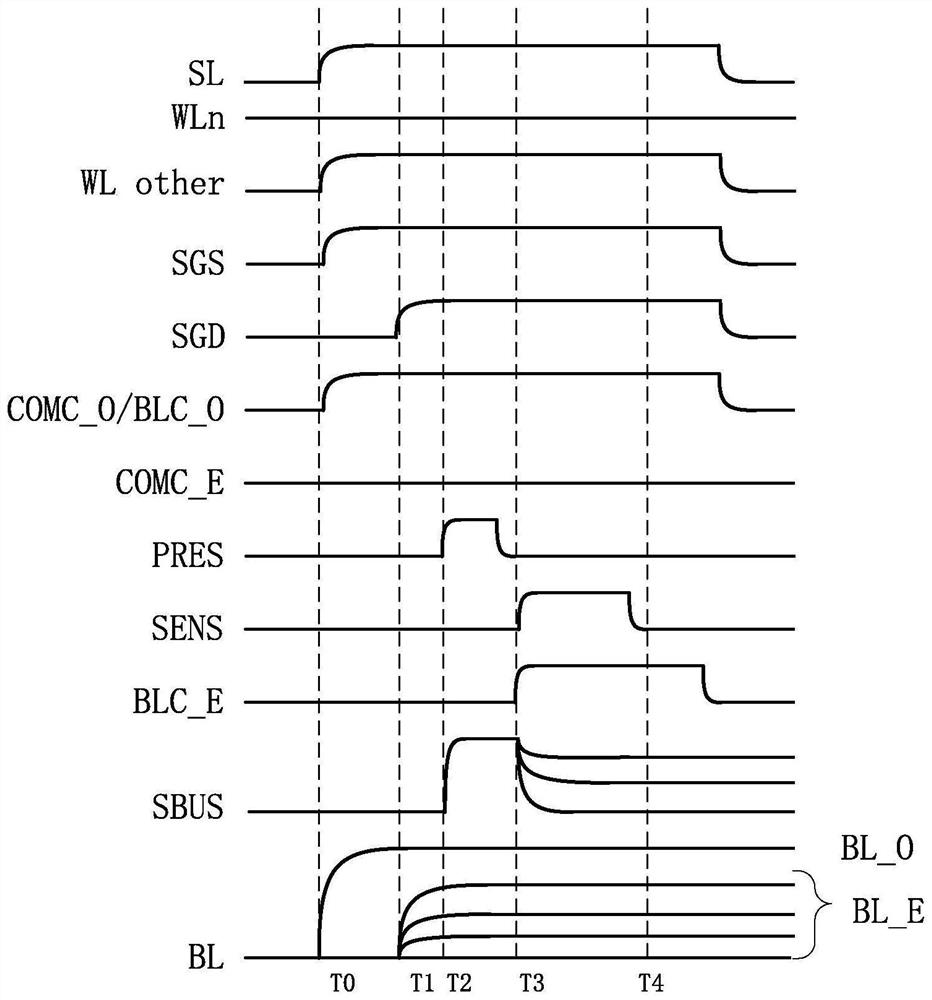

[0057] The charging circuit is connected to the storage unit selection circuit, and is used to initially charge the bit line BLO of the first storage unit string in the storage unit selection circuit; and charge the source line SL; After the bit line BLO of the first memory cell string is charged stably, charge the bit line BLE of the second memory cell string thr...

Embodiment 2

[0079] refer to Figure 4 , which shows a non-volatile memory processing method, which is applied to any of the above-mentioned non-volatile memory processing circuits, and may specifically include:

[0080] Step 401: Determine the storage unit to be detected in the storage unit selection circuit; wherein, the storage unit string where the storage unit to be detected is located is a second storage unit string.

[0081] In the embodiment of the present invention, the storage unit selection circuit can select the storage unit to be detected. In order to clearly illustrate the embodiment of the present invention when reading data from the storage unit, the paired storage unit strings are distinguished, so the storage unit to be detected is located The string of storage cells is called the second string of storage cells, and the string paired with the second string of storage cells is the first string of storage cells.

[0082]As a preferred implementation of the embodiment of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More