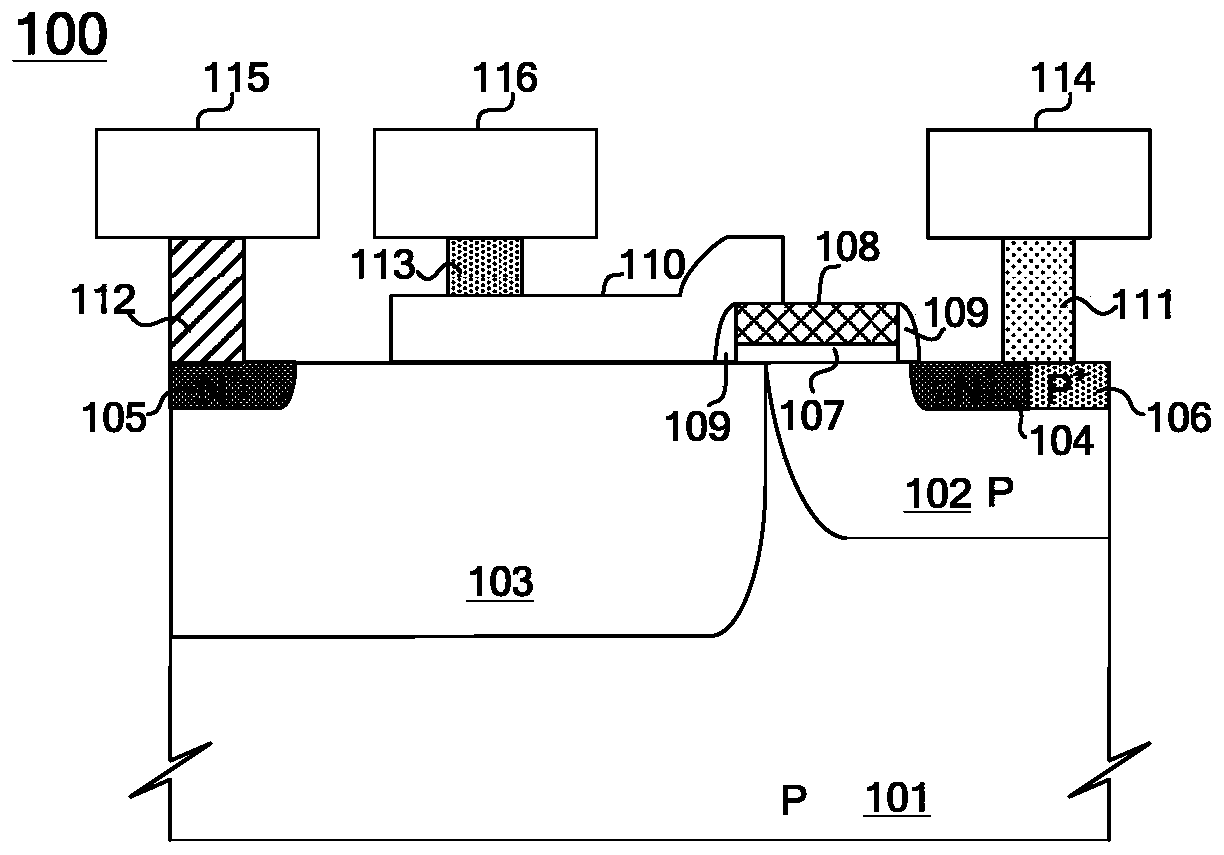

LDMOS device and manufacturing method thereof

A manufacturing method and device technology, which is applied in the field of laterally diffused metal oxide semiconductor devices, can solve the problems of reduced efficiency and power consumption of LDMOS devices, and achieve the effects of small gap, low ohmic loss, and improved breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] Specific embodiments of the present invention will be described in detail below, and it should be noted that the embodiments described here are only used for illustration and are not intended to limit the present invention. In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be apparent, however, to one of ordinary skill in the art that these specific details need not be employed to practice the present invention. In other instances, well-known circuits, materials or methods have not been described in detail in order to avoid obscuring the present invention.

[0015] Throughout this specification, reference to "one embodiment," "an embodiment," "an example," or "example" means that a particular feature, structure, or characteristic described in connection with the embodiment or example is included in the present invention. In at least one embodiment. Thus, appearances of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More