Flattening process method

A planarization process and process technology, applied in the field of planarization process, can solve problems such as reducing the performance of semiconductor devices, and achieve the effect of ensuring height and size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

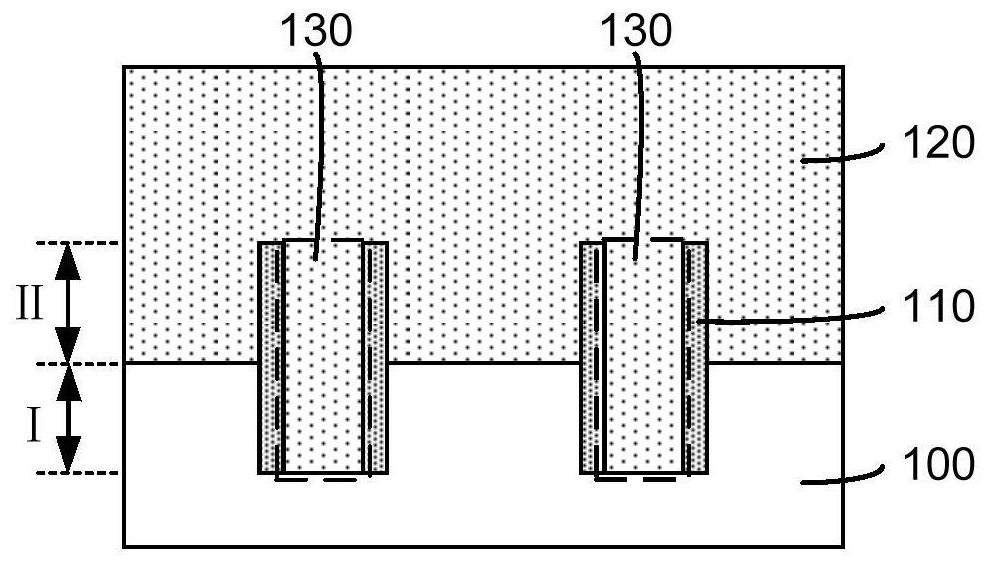

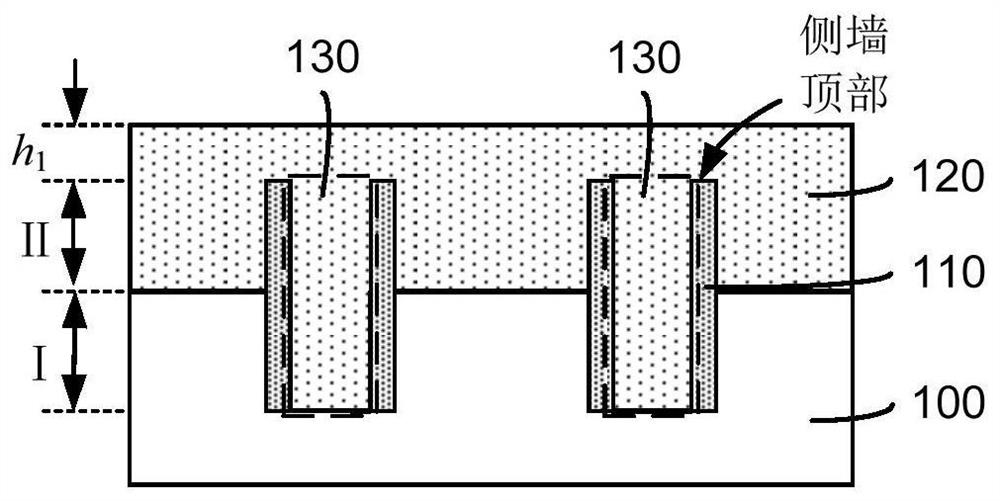

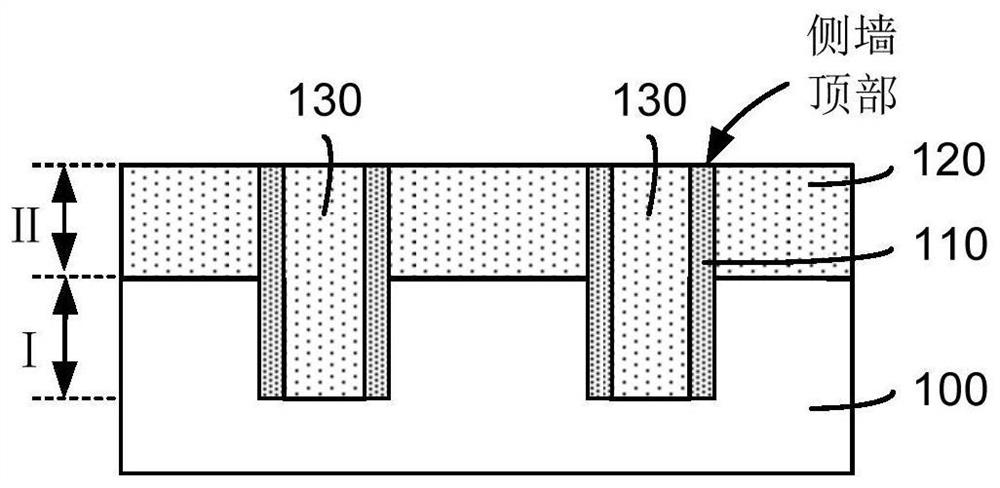

[0035] Please refer to figure 1 , a metal material layer 120 is formed on the semiconductor substrate 100 , and a metal gate 130 is formed in the semiconductor substrate 100 and the metal material layer 120 .

[0036] The semiconductor substrate 100 serves as a process basis for forming semiconductor devices. The material of the semiconductor substrate 100 is at least one of the following materials: polysilicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI), and silicon-on-insulator (S-SiGeOI) Silicon germanium (SiGeOI), etc. In the embodiment of the present invention, the material of the semiconductor substrate 100 is polysilicon, and the semiconductor substrate 100 also includes other structures, such as: metal plugs, metal connection layers, dielectric layers and other structures, or includes these structures. other semiconductor devices, which are not specifically limited here.

[0037] In the embodiment of the prese...

no. 2 example

[0072] The difference between the second embodiment and the first embodiment is that the first grinding process is used to directly grind the metal material layer, the sidewall spacers and the second part of part of the metal gate, so that the second part of the remaining metal gate has the first a height. The subsequent process steps are the same as in the first embodiment.

[0073] Please refer to Image 6 , providing a semiconductor substrate 200 , a spacer 210 , a metal material layer 220 and a metal gate 230 .

[0074] The structures, functions and positional relationships of the semiconductor substrate 200 , the sidewall spacers 210 , the metal material layer 220 and the metal gate 230 are the same as those of the first embodiment, and are not repeated here.

[0075] Please refer to Figure 7 , using the first grinding process to grind the metal material layer 220 , part of the second part of the metal gate 230 and the sidewall spacer 210 .

[0076] The purpose of pe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More