LDPC encoding method and LDPC encoder

An encoding method and encoder technology, applied in the field of LDPC encoding methods and LDPC encoders, can solve the problems of single encoding parallelism and high complexity, and achieve the effect of reasonable configuration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0049] Embodiment 1 of the present invention provides a kind of LDPC coding method, and this method comprises:

[0050] Step 1) The CCSDS near-Earth satellite communication standard adopts (8176,7154) LDPC codes with a coding efficiency of 7 / 8. This code has good structural characteristics, and its generation matrix G is a matrix with a size of 7154×8176:

[0051]

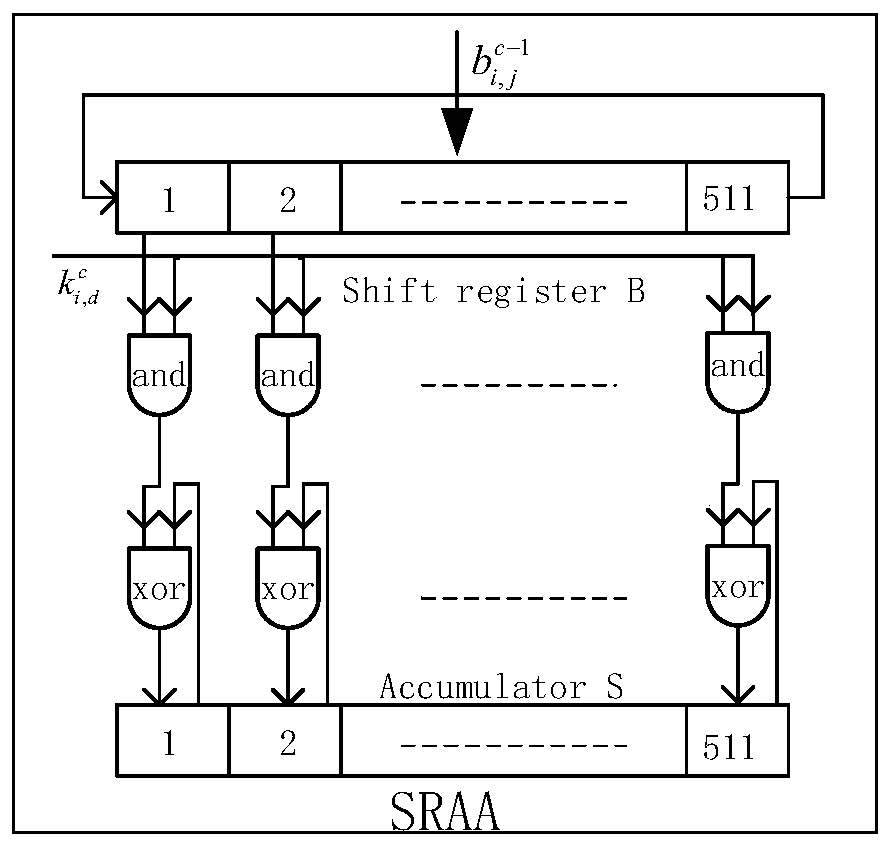

[0052] As shown in formula (1), the generator matrix G is composed of 14×16 circular matrices with a size of 511×511, where I is the unit matrix, 0 is the zero matrix, and B i,j (i=1,...14; j=1,2) is a circular matrix, b i,j for B i,j first line.

[0053] The generator matrix G corresponds to the codeword (u, C). The first 14 blocks of G correspond to the information bit vector u, and the last 2 blocks correspond to the check bit vector C.

[0054] Step 2) Take 511 bits as a segment, divide the information bit vector u into 14 sub-vectors A i =(u (i-1)×511+1 u (i-1)×511+2 … u i×511 ), and at the same ti...

Embodiment 2

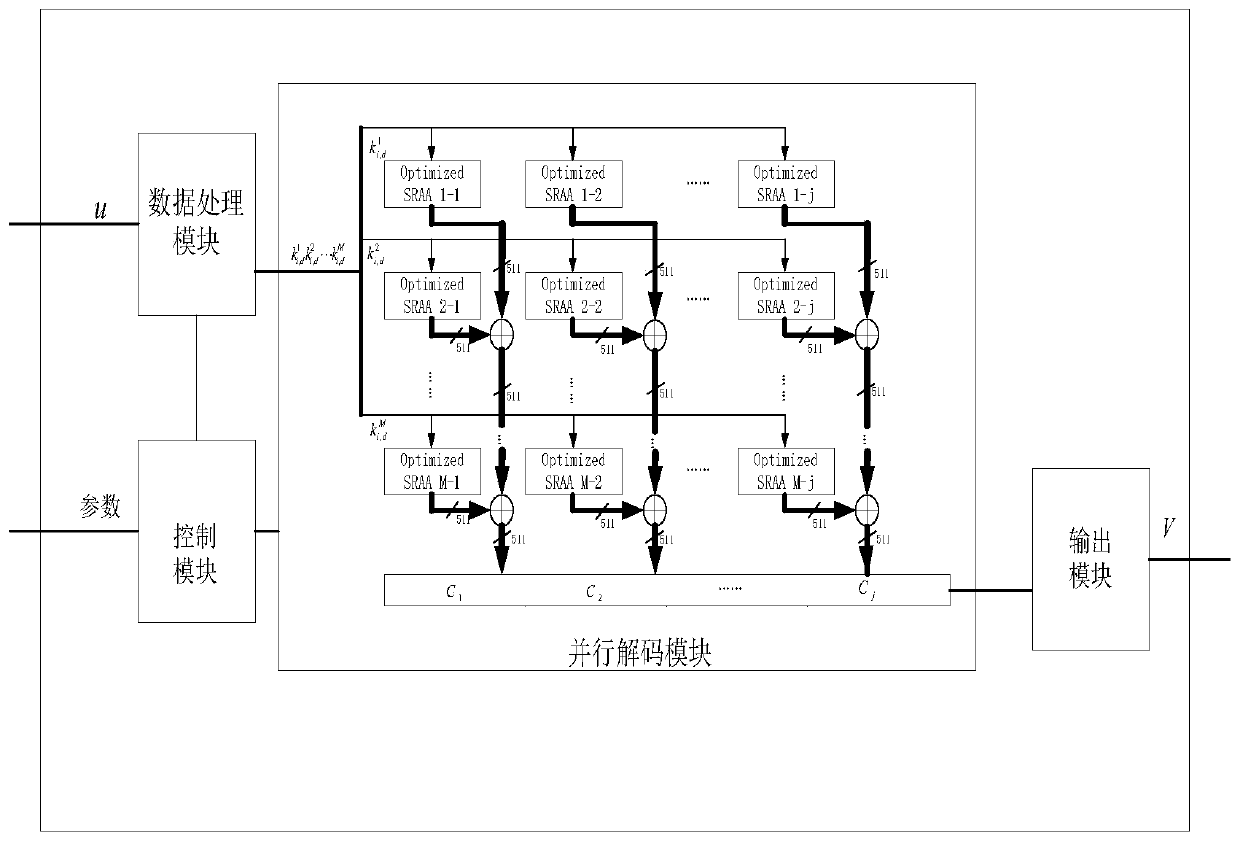

[0060] Embodiment 2 of the present invention proposes a low-complexity configurable LDPC encoder, its structure diagram is as follows figure 1 As shown, including: control module, data processing module, parallel coding module and output module;

[0061] The control module is used to control the output of the data processing module by M bits, and dynamically configure the parallel encoding module;

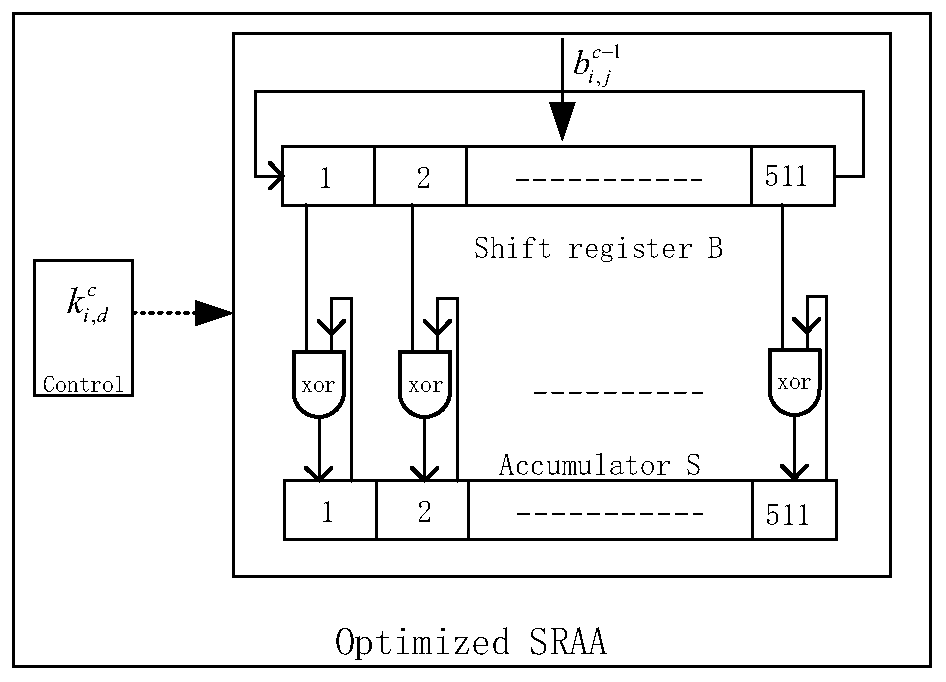

[0062] The data processing module is used to divide the information bit vector u into 14 sub-vectors A with a length of 511 1 ,…A 14 , and for each A i Perform 0-fill processing and expand it into an information bit vector E with a length of 512 i , according to the encoding parallelism M, the E i Divided into M sub-vectors with a length of N=512 / M bits i=1,2,...14, and encode M bits in parallel output to the parallel encoding module, where for The dth element, d=1,2,...N, c=1,2,...M;

[0063] The parallel encoding module is used to encode bits in parallel according to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More