RAID core computing device and method in SSD master control

A computing device and counter technology, applied in the direction of instruments, electrical digital data processing, etc., can solve the problem of no RAID core computing device and method, and achieve the effect of ensuring the correctness of data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] The characteristics of digital XOR logic are: the same gets 0, the different gets 1, any number XOR with 0 gets itself, XOR with 1 gets the opposite. Therefore, we can retrieve the currently lost value by performing an XOR operation on other items that participated in the XOR before and the previous XOR result. Specific operation: After the program data, the XOR result obtained through this device is also stored in the flash; when retrieving the data, first read out the previous related data (that is, other items participating in the XOR, determined by the raid level) and The previous XOR result, and then restore the lost data through the XOR operation.

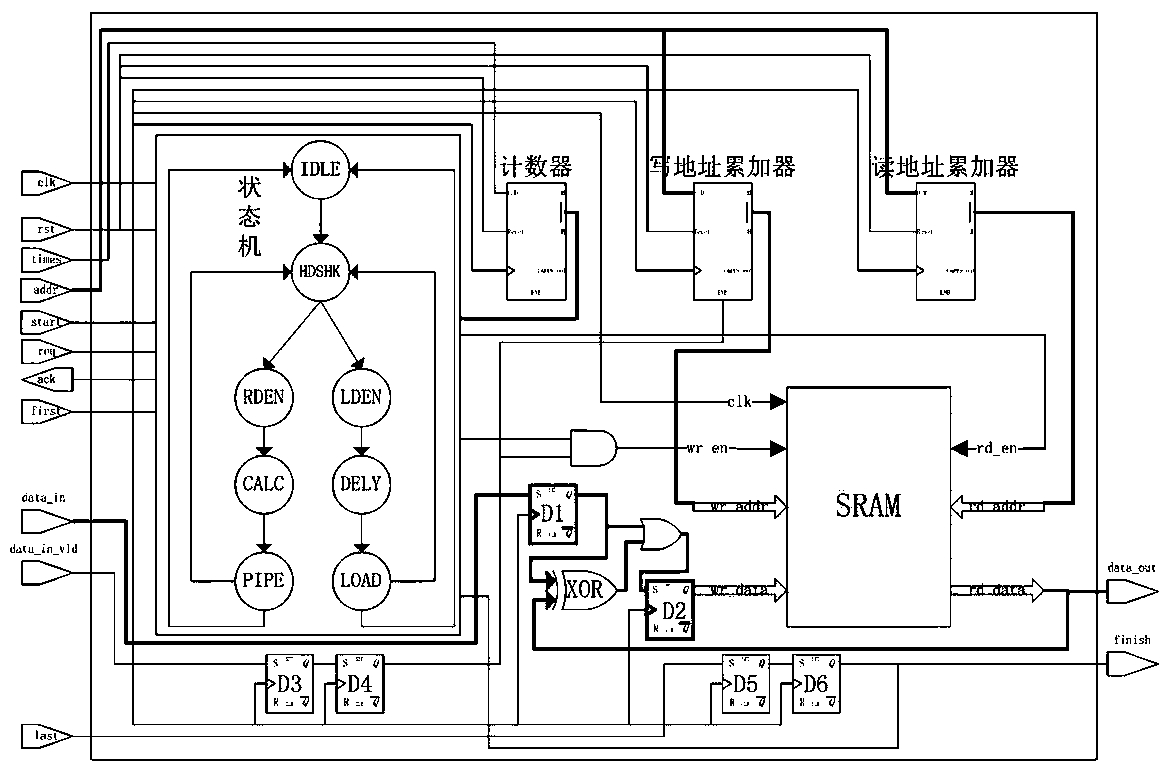

[0030] Utilizing the characteristic of XOR operation, the device realizes RAID core calculation by using state machine, dual-port SRAM, XOR operation unit and address accumulator circuit unit.

[0031] like figure 1 As shown, the RAID core computing device in the SSD master disclosed in this embodiment includes a sta...

Embodiment 2

[0042] This embodiment discloses a RAID core calculation method in the SSD master control, the RAID core calculation device described in Embodiment 1 of the method, specifically comprising the following steps:

[0043] The state machine is in the IDLE state: it detects that the external start signal is pulled high, and loads the number of cycles into the counter. The state machine enters the HDSHK state.

[0044] 2. The state machine is in the HDSHK state: it detects that the external req signal is pulled high and the ack feedback signal is pulled high to complete the handshake. It is decided to enter the LDEN or RDEN state according to whether the counter is the initial value of the number of cycles. The first round of the cycle (when the number of cycles is the initial value) is to enter the LDEN state, and then enter the DELY and LOAD states, because the first round only needs to write data to the SRAM; the second round to the last round of the cycle (the number of cycles ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More