Half-adder, full-adder and multiplier based on memristor array

A memristor and half adder technology, applied in the field of memristors, can solve the problems of data call and storage consumption power consumption, and achieve the effect of reducing extra power consumption, reducing computing time, and reducing data scheduling time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

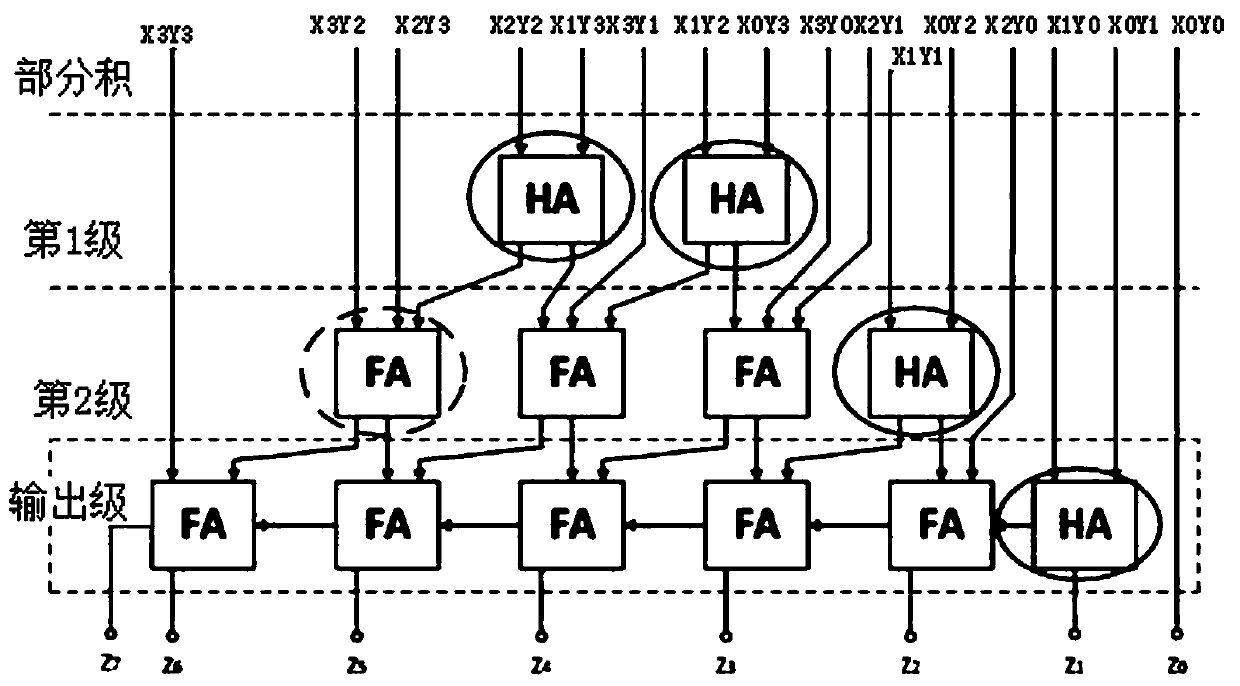

[0044] like Figure 4 As shown, it is a traditional wallace-tree digital multiplier. Taking 4 bits multiplied by 4 bits as an example, it is divided into the first level, the second level, and the output level. Each bit of the multiplier is obtained through an AND gate circuit; X0Y0 is the unit bit Z0; X0Y1 and X1Y0 are used as the input of the first CMOS half adder, the output sum is the tens bit Z1, and the output carry is used as the hundreds bit CMOS full adder of the output stage input; X0Y2 and X1Y1 are used as the input of the second CMOS half adder, and the output sum, X2Y0, and the output carry of the first CMOS half adder are collectively used as the input of the hundred-digit CMOS full adder, and the output sum is the hundred-digit Z2; X1Y2 and X0Y3 are used as the input of the third CMOS half adder; the output of the third CMOS half adder and, X3Y0, X2Y1 are jointly used as the input of the second-level thousand-bit CMOS full adder; the second-level thousand-bit CM...

Embodiment 2

[0046] On the basis of Embodiment 1, one or more of the first CMOS half adder, the second CMOS half adder, the third CMOS half adder, and the fourth CMOS half adder will be transformed into memristor arrays constitutes a half adder.

Embodiment 3

[0048] like figure 1 As shown, taking 4 bits multiplied by 4 bits as an example, it is divided into the first stage, the second stage, and the output stage. The partial product is used as the input, and the partial product is passed through each bit of the multiplier and the multiplicand through the AND gate circuit. Obtained; X0Y0 is the unit digit Z0; X0Y1 and X1Y0 are used as the input of the first half adder, the output sum is the tens digit Z1, and the output carry is used as the input of the hundred-digit CMOS full adder of the output stage; X0Y2 and X1Y1 are used as the second half adder The input of the device, the output sum, X2Y0, and the output carry of the first half adder are jointly used as the input of the hundred-digit CMOS full adder, and the output sum is the hundred-digit Z2; X1Y2 and X0Y3 are used as the input of the third half-adder; the third The output sum of the half adder, X3Y0, and X2Y1 are used as the input of the second-level thousand-bit CMOS full ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More