Forming method for semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve problems such as mutual interference, affecting device performance and stability, and achieve the effect of avoiding mutual interference, improving performance and stability, and being easy to receive.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

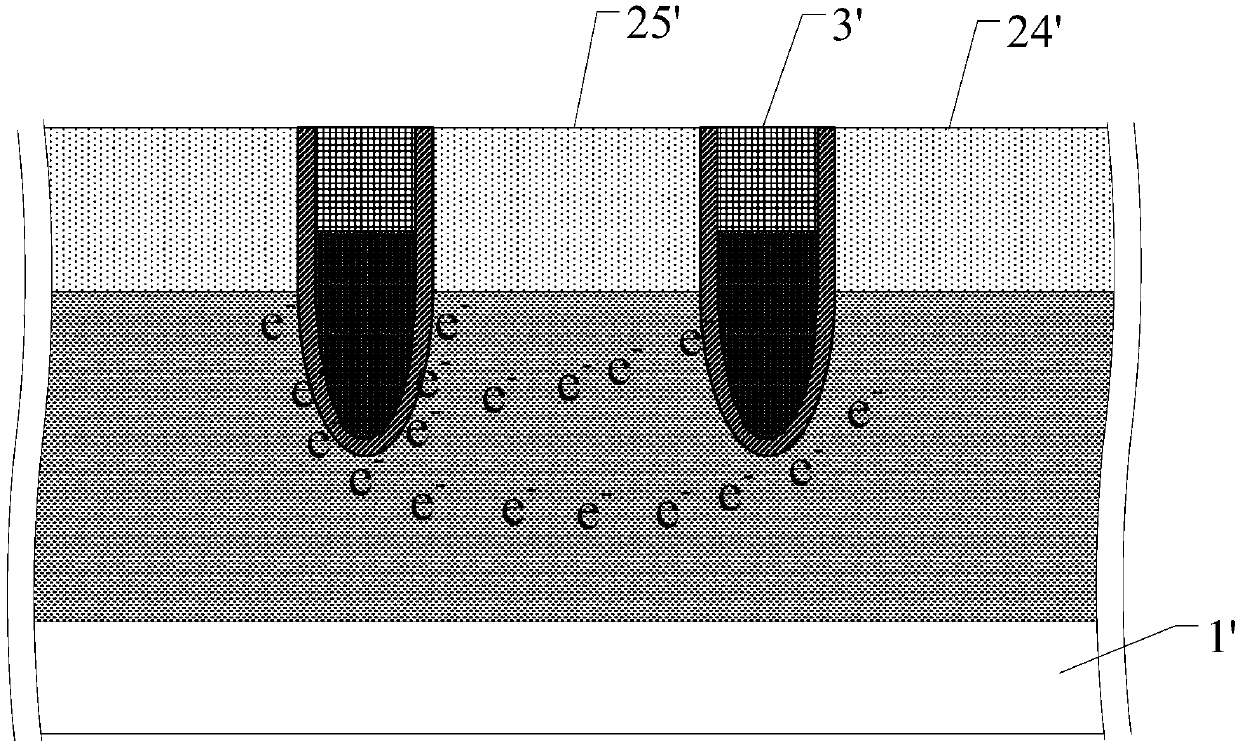

[0035] There is a semiconductor device such as figure 1 As shown, it includes a substrate 1' and two gate structures 3', a drain region 25' and a plurality of source regions 24' are formed in the substrate 1, and the source regions 24' conform to the active region The extension direction is arranged on both sides of the drain region 25', and each gate structure 3' is formed in the substrate between the drain region 25' and the source region 24' to form an access transistors, the adjacent access transistors in the same active region share the drain region 25', and the drain region 25' and the source region 24' extend downward from the surface of the substrate 1' to the same depth , forming a symmetrical structure. It can be understood that, when this semiconductor device is in use, the part of the substrate 1' along the bottom of the gate structure 3' constitutes a channel region, and when an access transistor is turned on, its source region 24' When the electrons migrate to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More