Constant slope digital-to-time converter and control method thereof

A digital time, constant slope technology, used in time-to-digital converters, electrical unknown time interval measurement, devices for measuring time intervals, etc., can solve the problems of limited linearity performance of digital-to-time converters and achieve high linearity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be further described below through specific embodiments in conjunction with the accompanying drawings. These embodiments are only used to illustrate the present invention, and are not intended to limit the protection scope of the present invention.

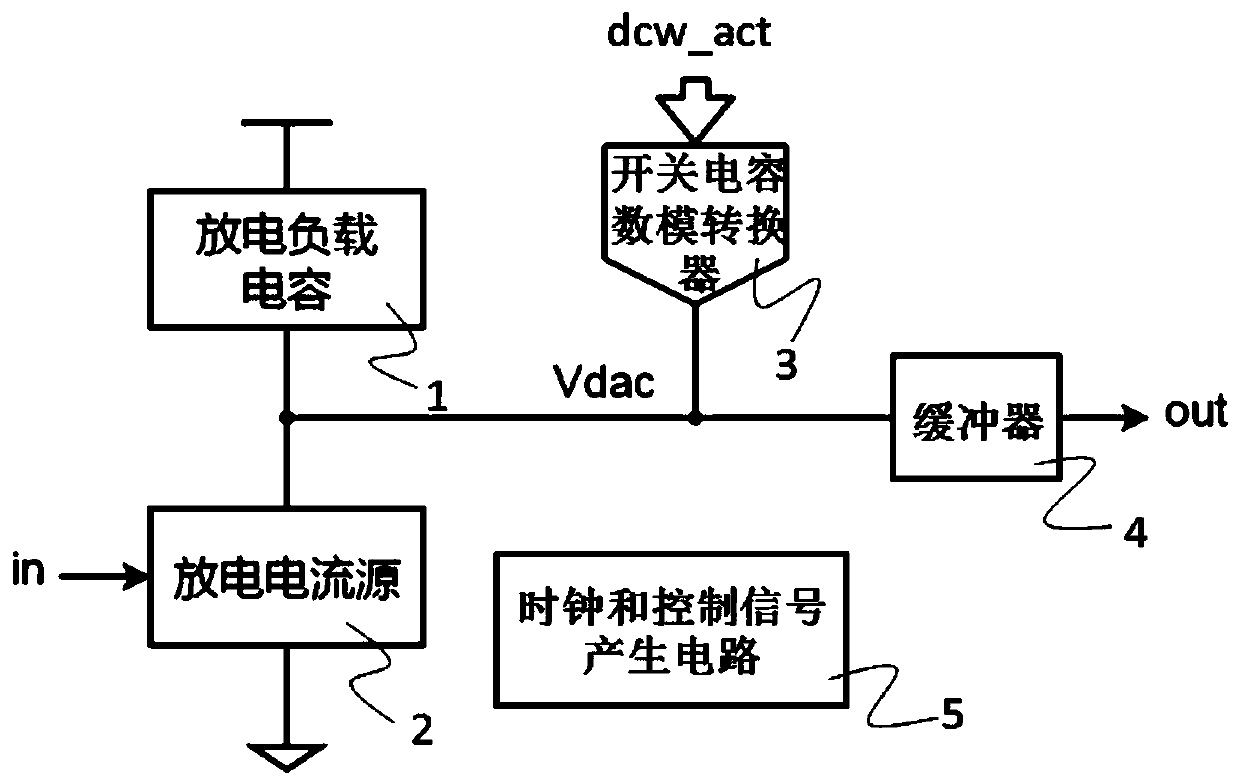

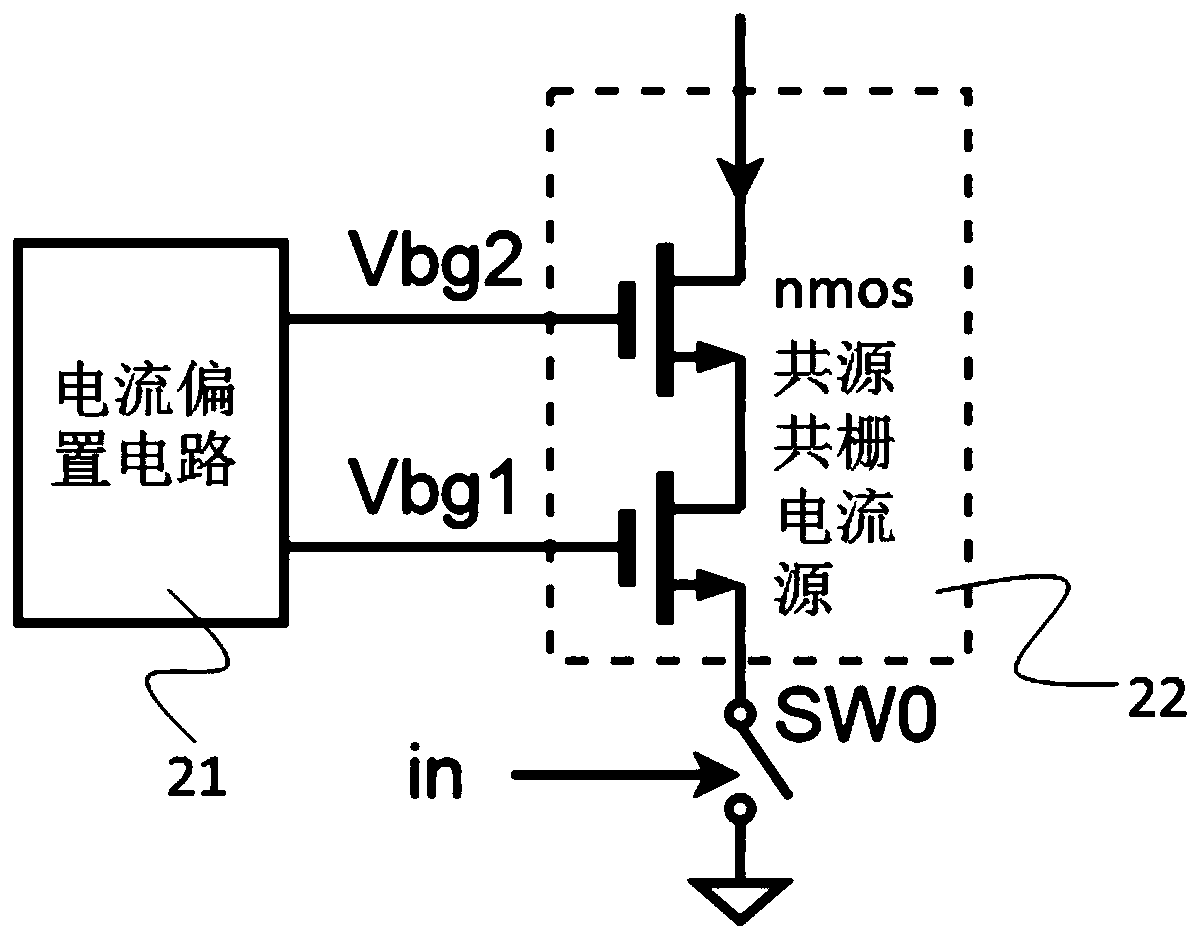

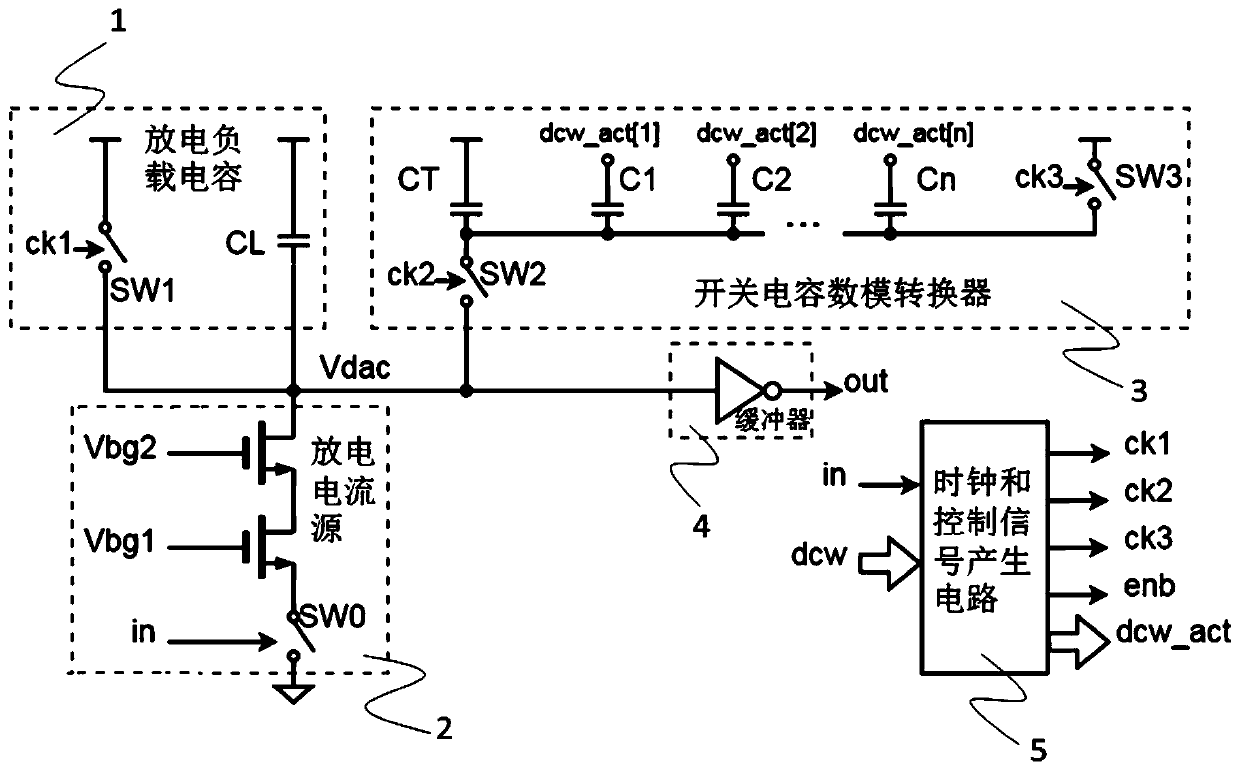

[0040] Such as figure 1 As shown, the present invention provides a constant slope digital-to-time converter, which includes: a discharge load capacitor 1 for storing charges to discharge to generate a voltage falling edge; a discharge current source 2 whose input terminal is connected to the discharge load capacitor The output terminal of 1 is connected to determine the slope of the falling edge of the output voltage through the discharge current of the discharge load capacitor 1; the output terminal of the switched capacitor digital-to-analog converter 3 is connected to the output terminal of the discharge load capacitor 1 for setting The discharge starting voltage of the discharge load capacitor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More