Impedance balance degree analysis method of on-chip power combiner

A technology of power combiner and impedance balance, which is applied in the direction of instruments, special data processing applications, electrical digital data processing, etc. It can solve problems such as time-consuming, inability to analyze balance mismatch, etc., and achieve the effect of less hardware and software resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

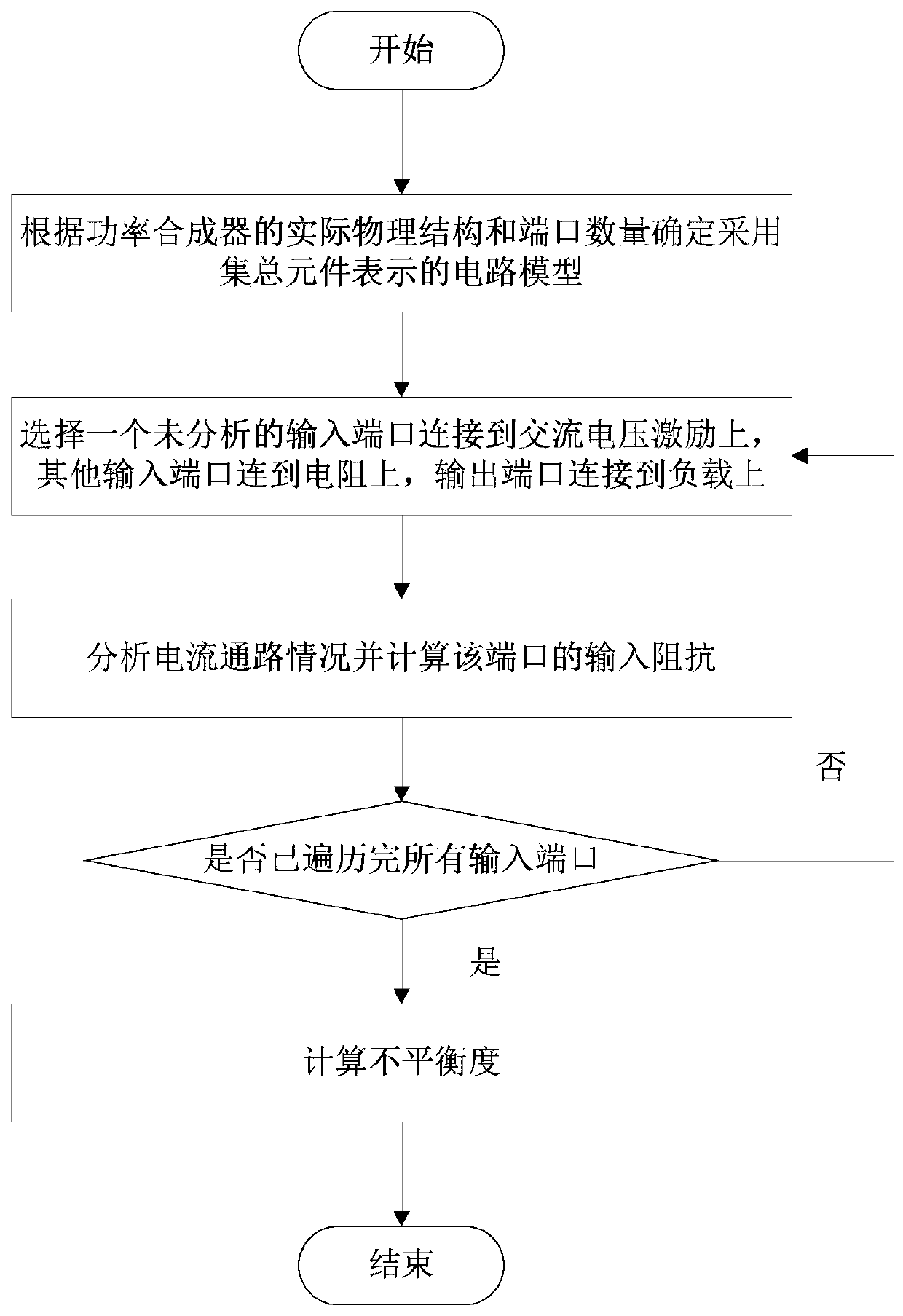

[0030] like figure 1 As shown, an impedance balance analysis method of an on-chip power combiner disclosed in an embodiment of the present invention, the steps include:

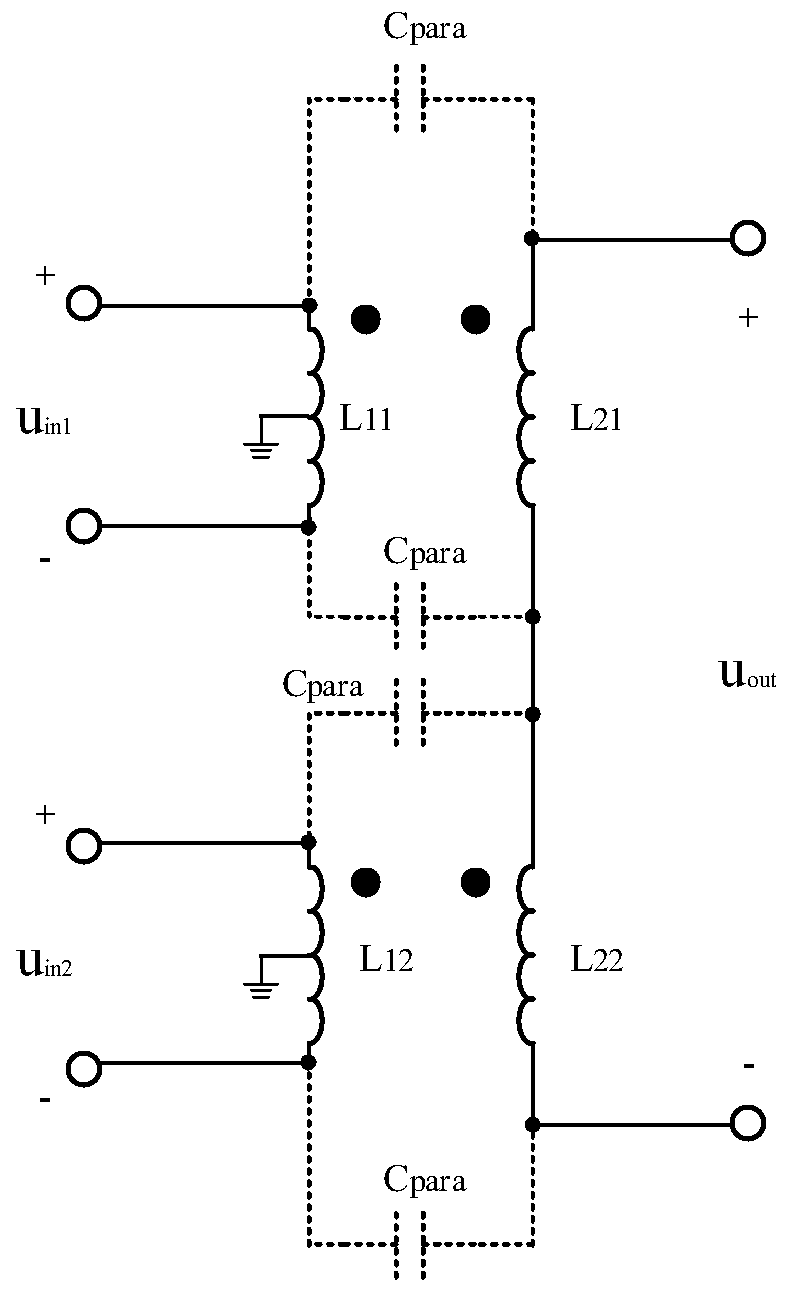

[0031] (1) According to the actual physical structure and number of ports of the power combiner, determine the circuit model represented by lumped elements, the model includes interlayer parasitic capacitance and transformer, and has N (N≥2) input ports and one output port , and the electromagnetic coupling between the coils is represented by a controlled current source connected across the output coil;

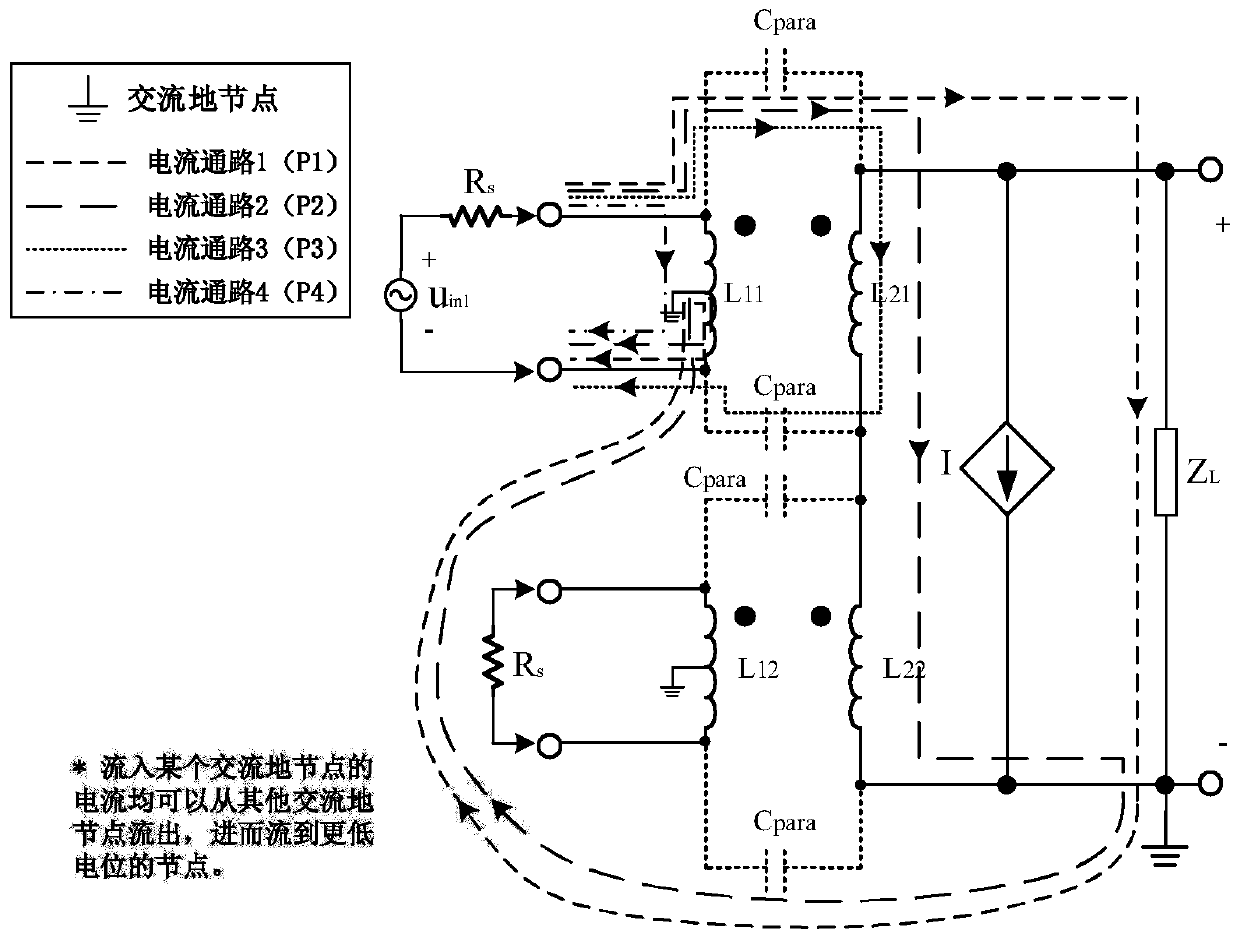

[0032] (2) Select one of the N input ports and connect it to an internal resistance R s The AC voltage excitation; connect the other N-1 input ports to N-1 resistances R s on the resistor; connect the output port to the load Z L superior;

[0033] (3) Analyze the path of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More