A debugging and verification platform and testing method for RISC-V processor system

A RISC-V, processor system technology, applied in fault hardware testing methods, electrical digital data processing, instruments, etc., can solve the problems of cumbersome SoC verification platform construction and high requirements for boards and cards, so as to improve project parallelism and flexible debugging The effect of high sex and highlighting substantive features

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

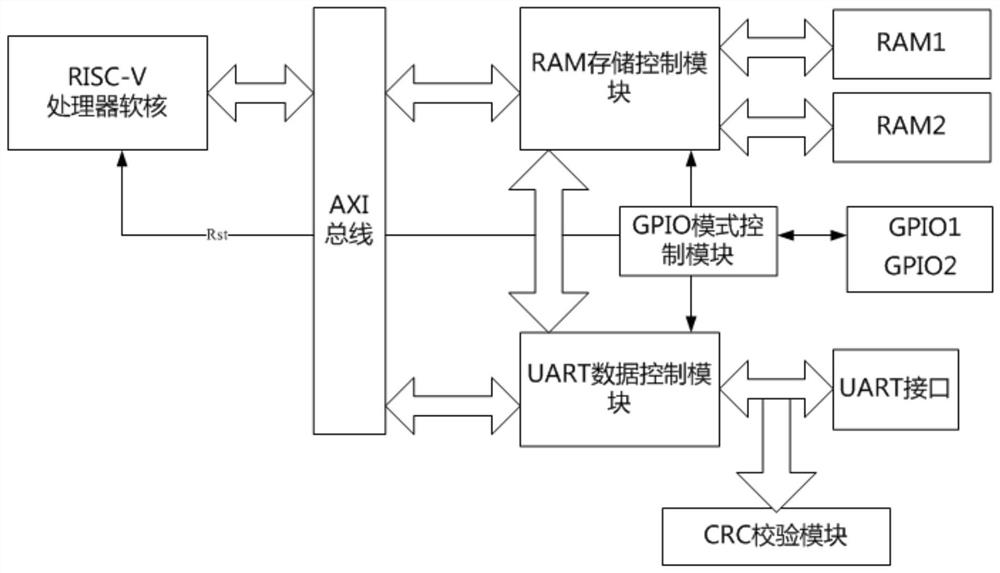

[0045] like figure 1 As shown, the technical solution of the present invention provides a debugging and verification platform for a RISC-V processor system. The FPGA-based RISC-V processor system starts the SoC verification platform, including a processor soft core, and the processor soft core passes through a bus. The module communicates with the RAM storage control module and the UART data control module respectively;

[0046] The platform also includes a mode control module, which is respectively connected with the RAM storage control module and the UART data control module;

[0047] The RAM storage control module is connected with a RAM memory; it is used for code instruction storage and program operation;

[0048] The mode control module is connected with a GPIO interface, which is used to generate a control signal to the processor soft core to transform the system mode according to the input signal of the GPIO interface;

[0049]The UART data control module is connecte...

Embodiment 2

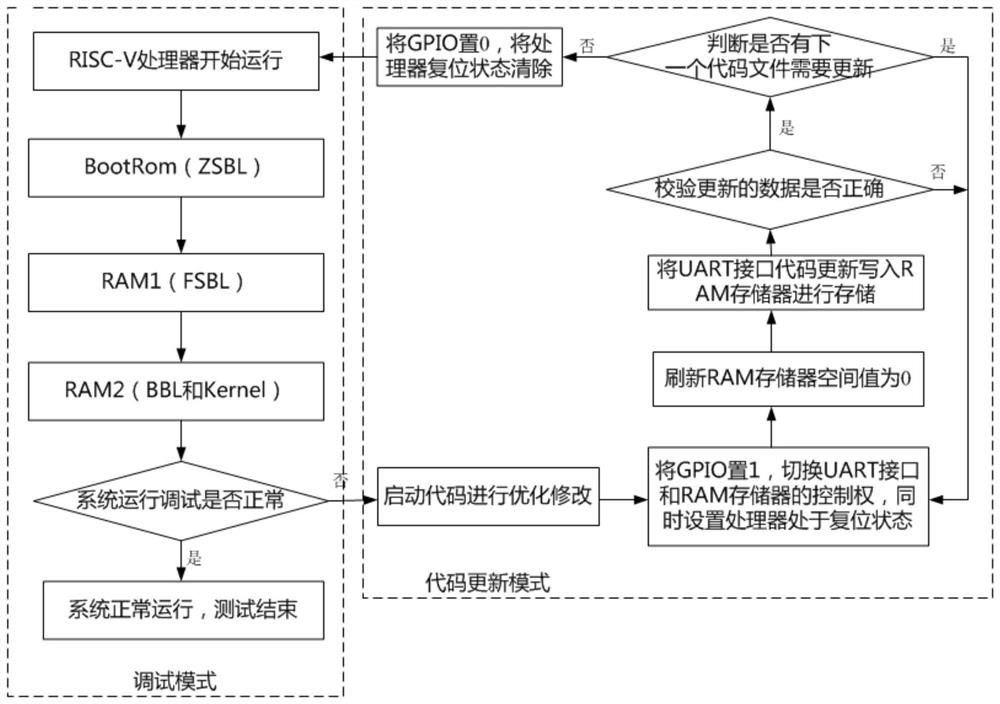

[0062] like figure 2 As shown, the technical solution of the present invention provides a test method for a debugging system of a RISC-V processor system. For the debugging platform of the first embodiment, the RISC-V system startup test method of the present invention can be divided into debugging according to GPIO control. and update two modes, including the following steps:

[0063] S1: RISC-V processor starts running;

[0064] S2: The startup code starts running;

[0065] For the RISC-V processor soft core, its operating frequency, BootRom address and RAM bus address need to be correctly configured. The system startup code includes ZSBL, FSBL, BBL and Kernel. In order to save storage resources, try to optimize invalid codes and optimize and simplify Kernel. At the same time, due to the use of the smallest SoC system, redundant hardware initialization code is omitted. The final system startup code file The storage and running space requirements are met (the function and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More