Fan-out type packaging method and fan-out type packaging structure of embedded chip

A packaging method and packaging structure technology, which are applied to semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of reducing the size of the packaging structure of the chip, many process steps, and complex processes, and achieve less interference. , less process steps, the effect of meeting development needs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

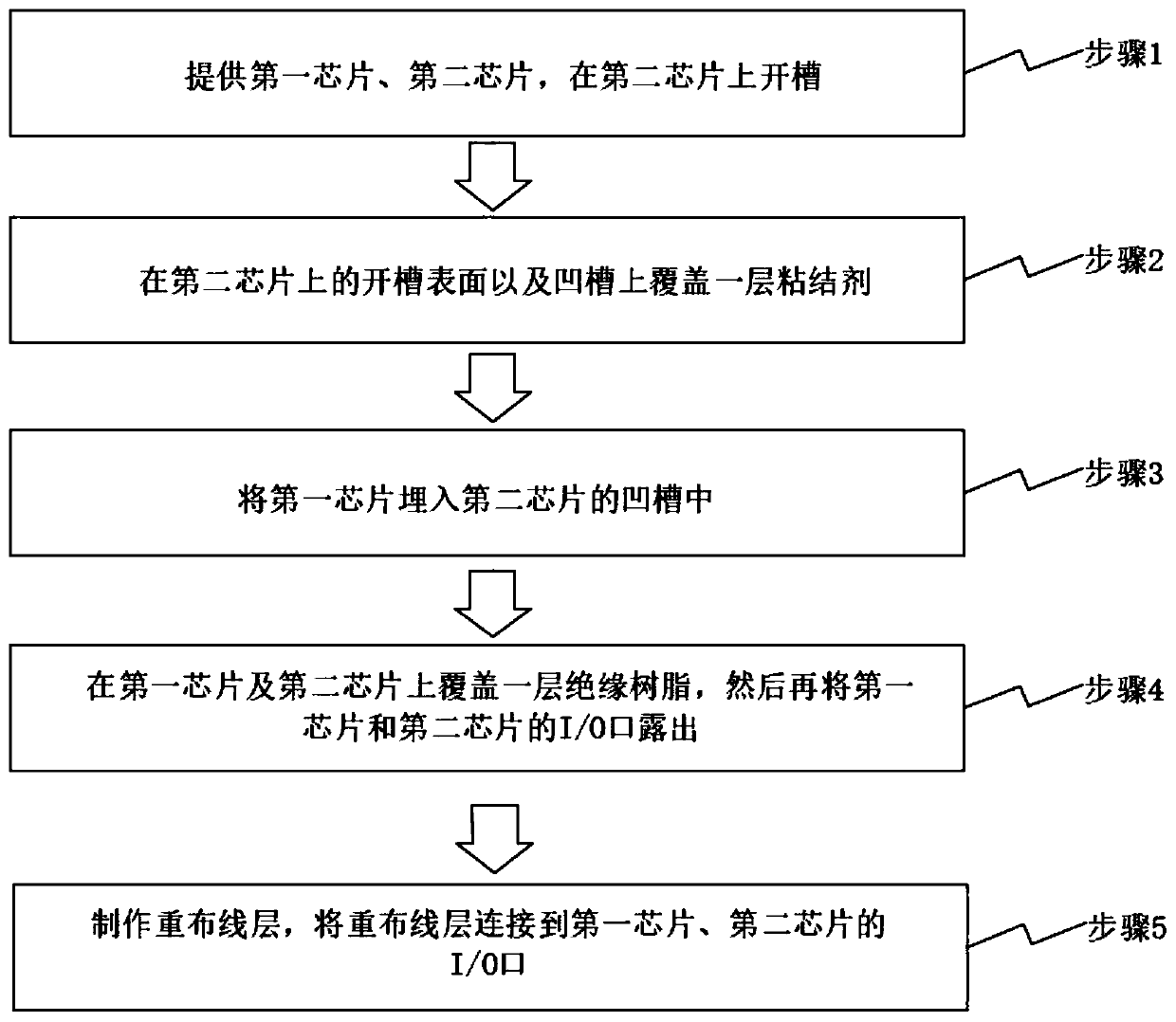

[0058] A fan-out packaging method for embedded chips of the present invention specifically includes the following steps:

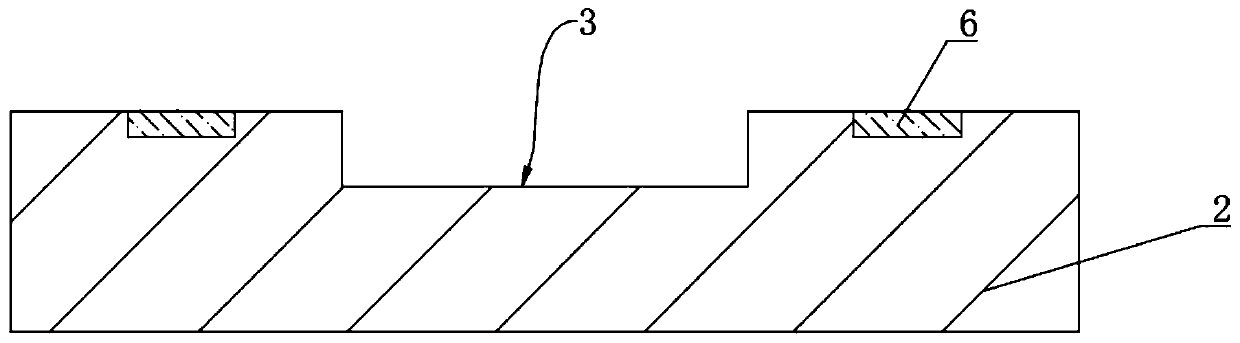

[0059] See figure 2 , step 1: provide the first chip 1 and the second chip 2, first form an opening on the second chip 2 through a photolithography process, and then etch a groove 3 at the position of the opening through an etching process, avoiding the second chip when slotting Functional area on chip 2;

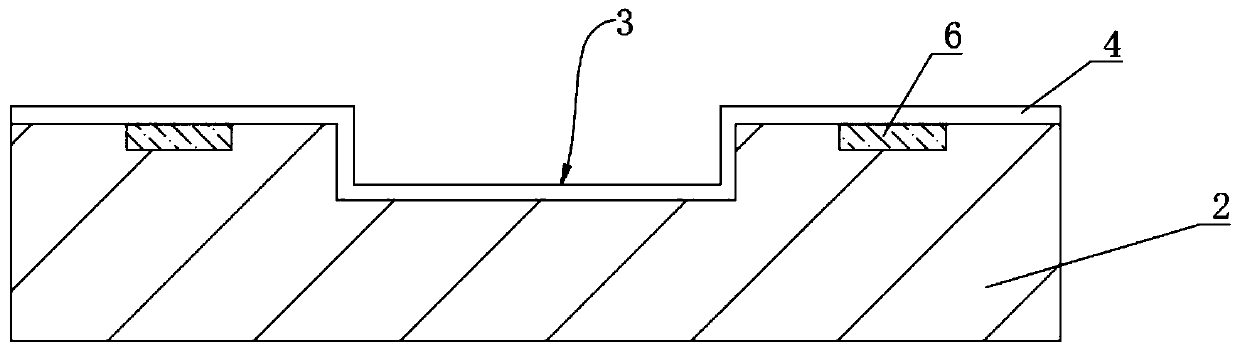

[0060] See image 3 , step 2: cover the grooved surface and the groove on the second chip 2 with a layer of adhesive to form the adhesive layer 4, specifically in this embodiment, the adhesive is covered on the second chip by a spraying process On the grooved surface of the groove, the adhesive 5 covers the side wall and the bottom surface of the groove 3 at the same time. Specifically, the adhesive can use DAF glue or PA glue;

[0061] See Figure 4 , step 3: burying the first chip 1 in the groove 3 of the second chip 2;

[0062] See Figure 5 ,...

specific Embodiment 2

[0071] A fan-out packaging method for embedded chips of the present invention comprises the following steps:

[0072] Step a: providing the first chip 1, the second chip 2, and the third chip 8;

[0073] Step b: firstly form openings on the second chip 2 and the third chip 8 through a photolithography process, and then etch a groove 3 at the position of the opening through an etching process, avoiding the second chip 2 and the third chip 8 when opening the grooves functional areas on

[0074] Step c: Cover the grooved surface on the second chip 2, the third chip 8 and the groove 3 with a layer of adhesive to form an adhesive layer 4, and the adhesive 5 covers the sidewall and bottom surface of the groove 3 at the same time ;

[0075] Step d: Embedding the first chip 1 in the groove 3 of the second chip 2, and embedding the second chip 2 in the groove 3 of the third chip 8;

[0076] Step e: Cover the first chip 1, the second chip 2, and the third chip 8 with a layer of insul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More