Semiconductor package and manufacturing method

A manufacturing method and packaging technology, which are applied to semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of obvious reflow process, affecting packaging reliability, and reducing process yield.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

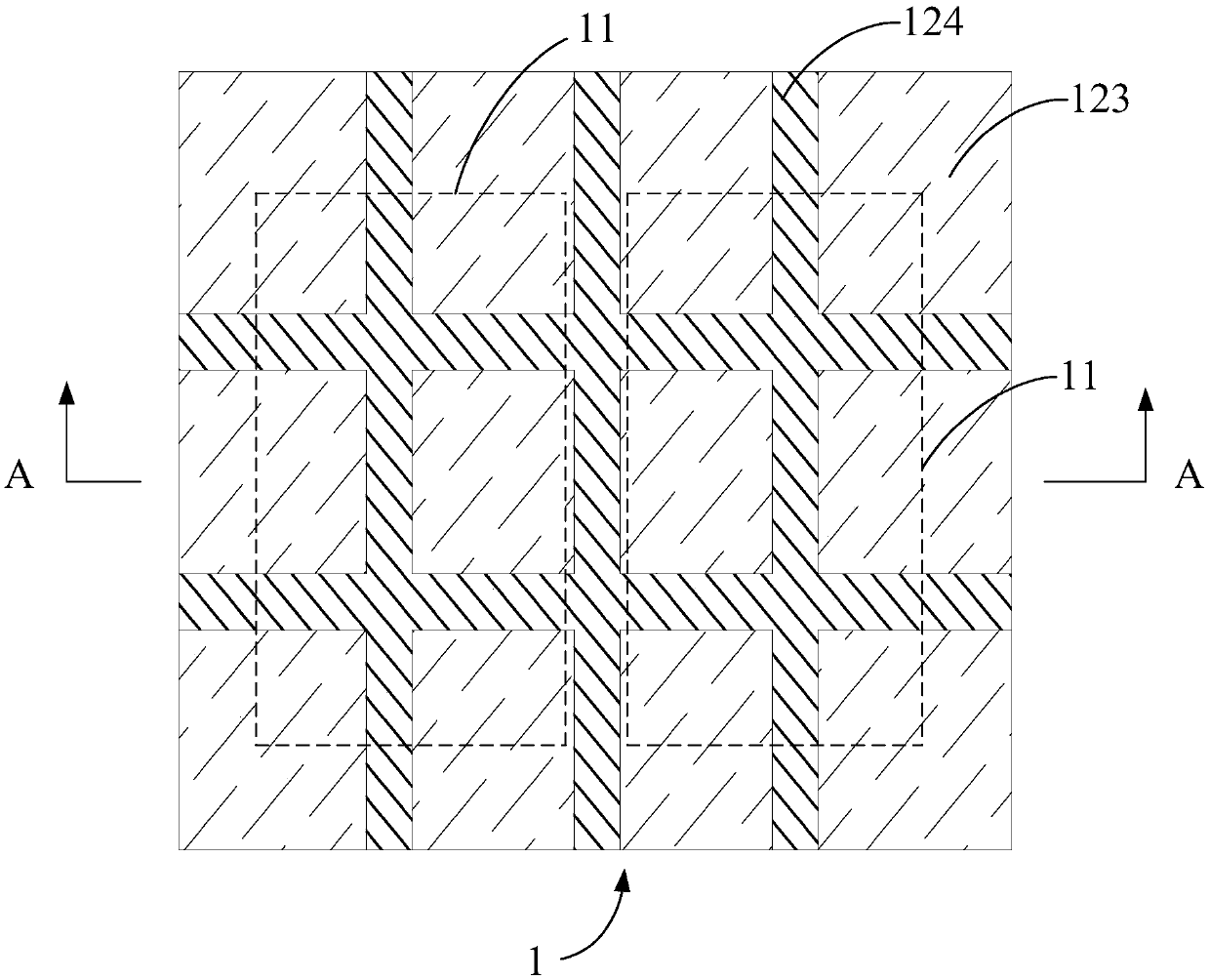

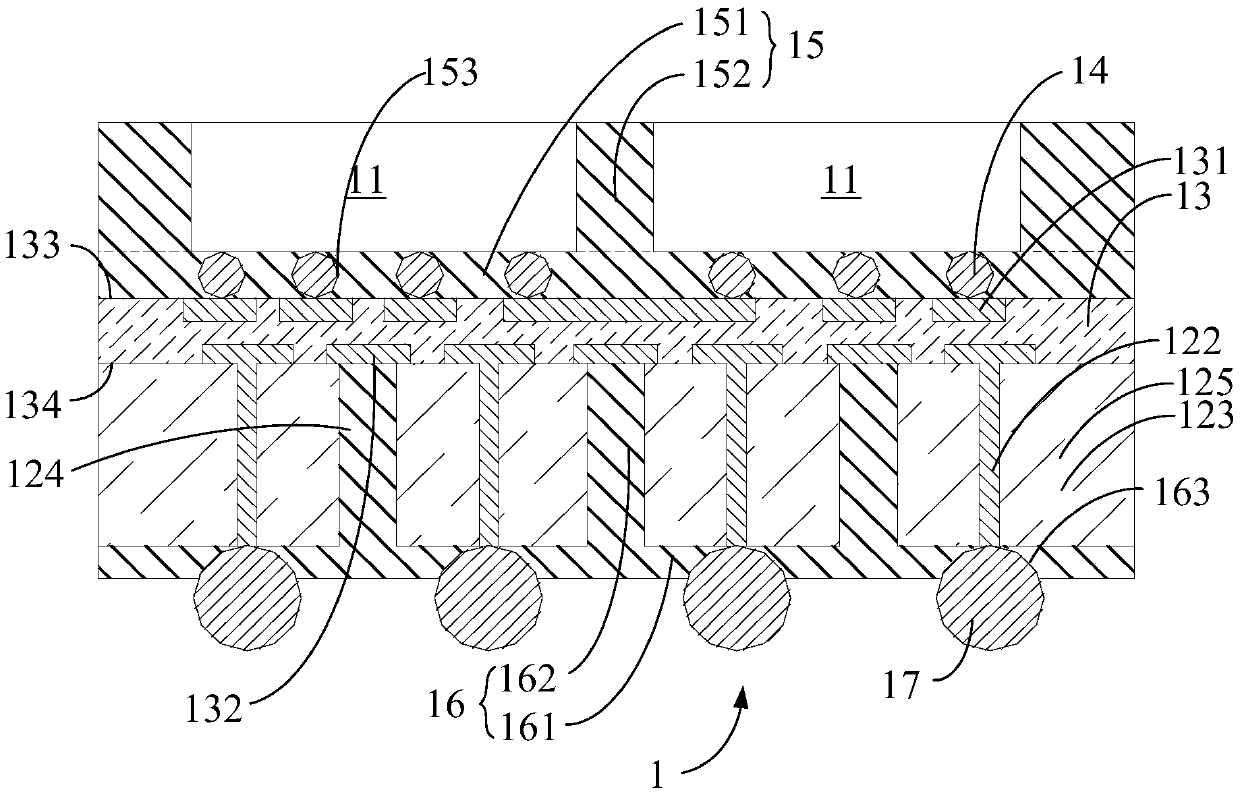

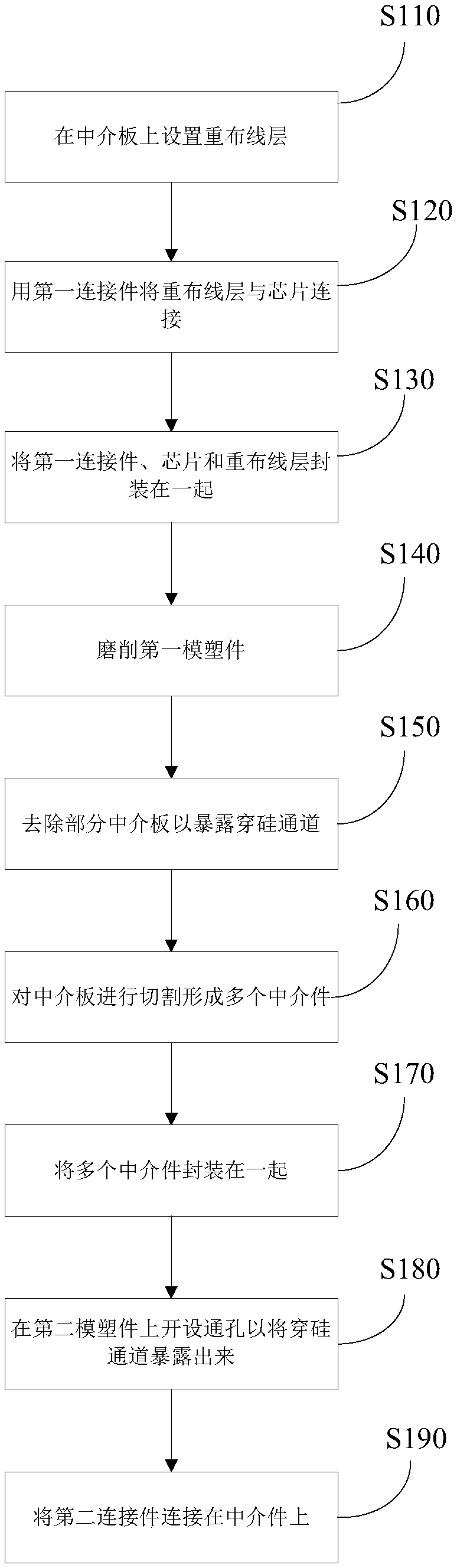

[0062] figure 1 , 2 The structure of a semiconductor package 1 in this embodiment is shown. The semiconductor package 1 includes a plurality of interposers 123 , a plurality of chips 11 , a plurality of first connectors 14 , a plurality of second connectors 17 and a redistribution layer 13 . A plurality of first connecting elements 14 and a plurality of intermediary elements 123 are respectively fixed on two sides of the redistribution layer 13 . Multiple chips 11 are fixed on the first connector 14 . The second connecting element 17 is disposed on a side of the interposer 123 away from the redistribution layer 13 . The two chips 11 can be electrically connected to each other through the redistribution layer 13 , and the chips 11 are electrically connected to the second connection member 17 through the first connection member 14 , the redistribution layer 13 , and the intermediary member 123 connected in sequence. The second connector 17 can be used as a pin of the semicon...

Embodiment 2

[0109] The semiconductor package 1a in the second embodiment differs from the semiconductor package 1 in the first embodiment only in the interposer and the groove. For the sake of brevity, only the structure and shape of the intermediary member 123a and the groove 124a in the second embodiment will be described below.

[0110] refer to Figure 12 , In this embodiment, the intermediary member 123a is a right triangle. The intermediaries 123a are provided in pairs. The hypotenuses of the two intermediary pieces 123a arranged in pairs are parallel to each other and close to each other, and the groove 124a separates the hypotenuses of the two intermediary pieces 123a. There are two pairs of intermediary members 123a, and the two pairs of intermediary members 123a are separated from each other by grooves 124a. Two chips 11a are provided, and each chip 11a can be projected onto a pair of interposers 123a arranged in pairs.

[0111] Since a groove 124a is formed between two adja...

Embodiment 3

[0113] The semiconductor package 1b in the third embodiment differs from the semiconductor package 1 in the first embodiment only in the interposer and the groove. For the sake of brevity, only the intermediary member 123b and the groove 124b in the third embodiment are described below.

[0114] refer to Figure 13 , in this embodiment, the intermediary member 123b is rectangular. The intermediary 123b is provided with four pieces. Two adjacent intermediary pieces 123b are separated from each other, and a groove 124b is formed between two adjacent intermediary pieces 123b. The grooves 124 are connected to form a "cross" structure. There are two chips 11b, one chip 11b can be projected onto two intermediary pieces 123b, and the other chip 11b can be projected onto the other two intermediary pieces 123b.

[0115] Since a groove 124b is formed between two adjacent interposers 123b, the groove 124b is an expansion joint of the intermediary substrate composed of a plurality of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More