Patents

Literature

54results about How to "Avoid splinters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

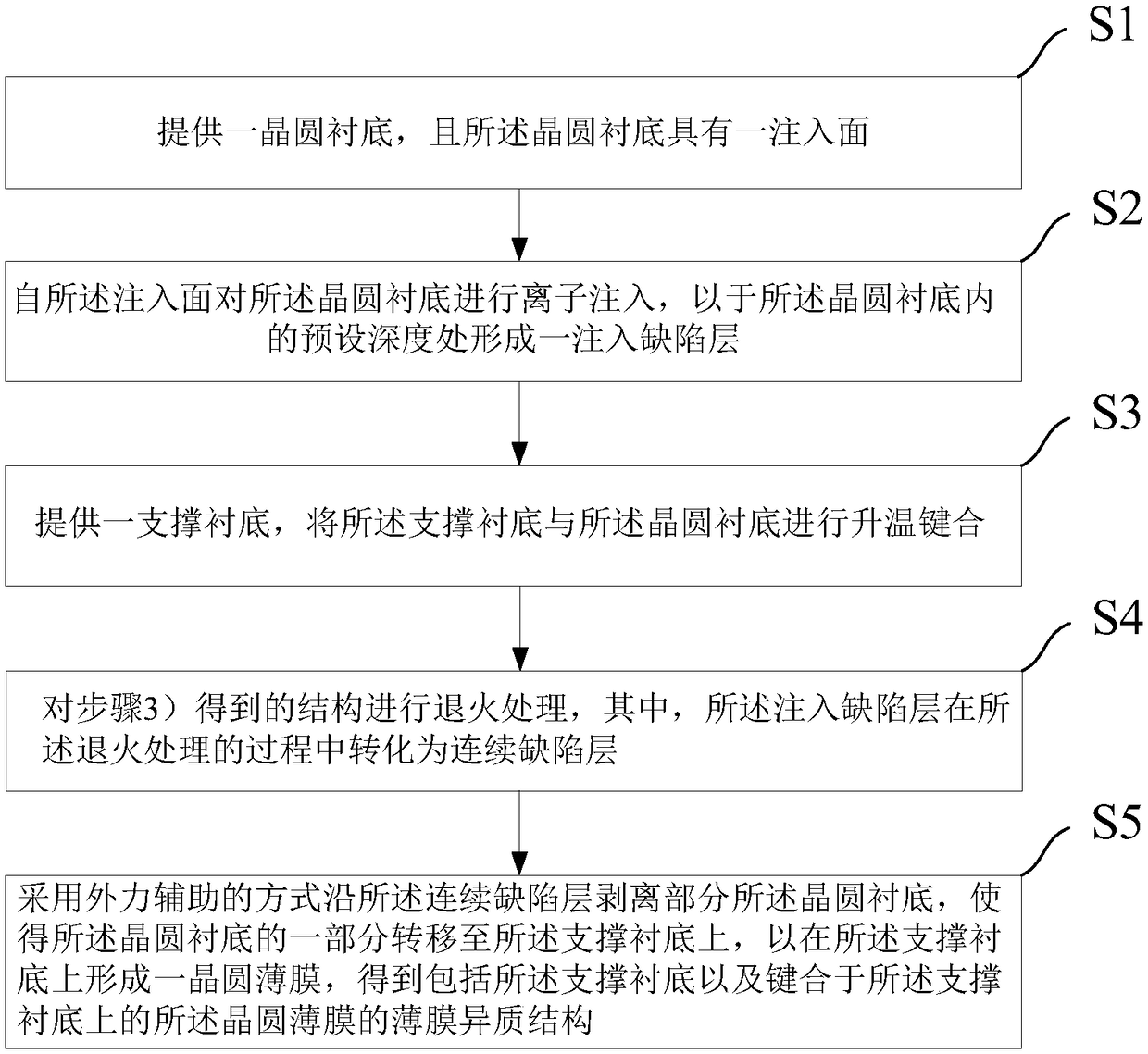

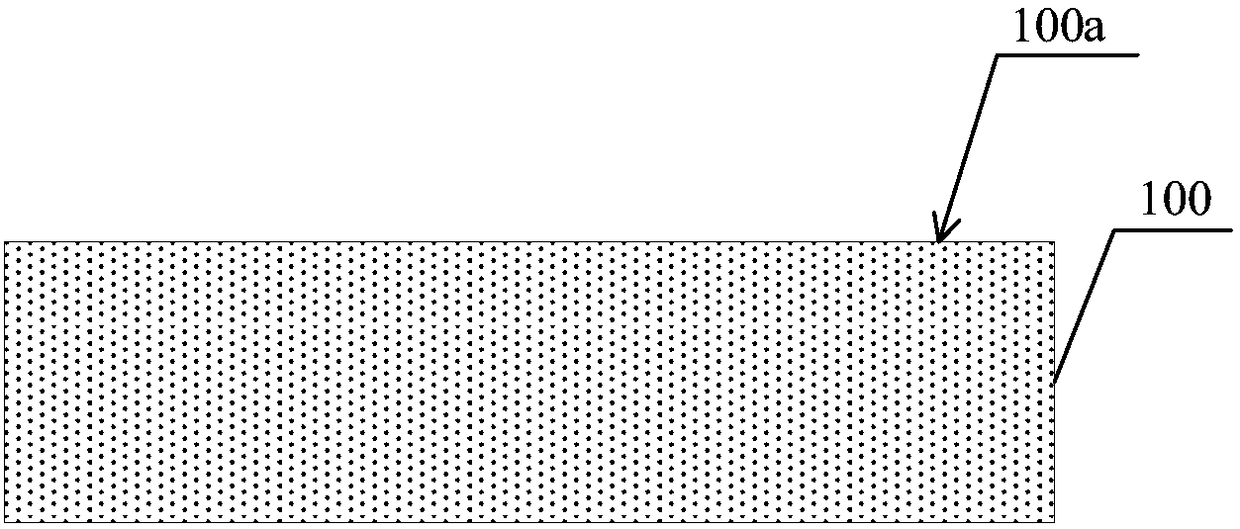

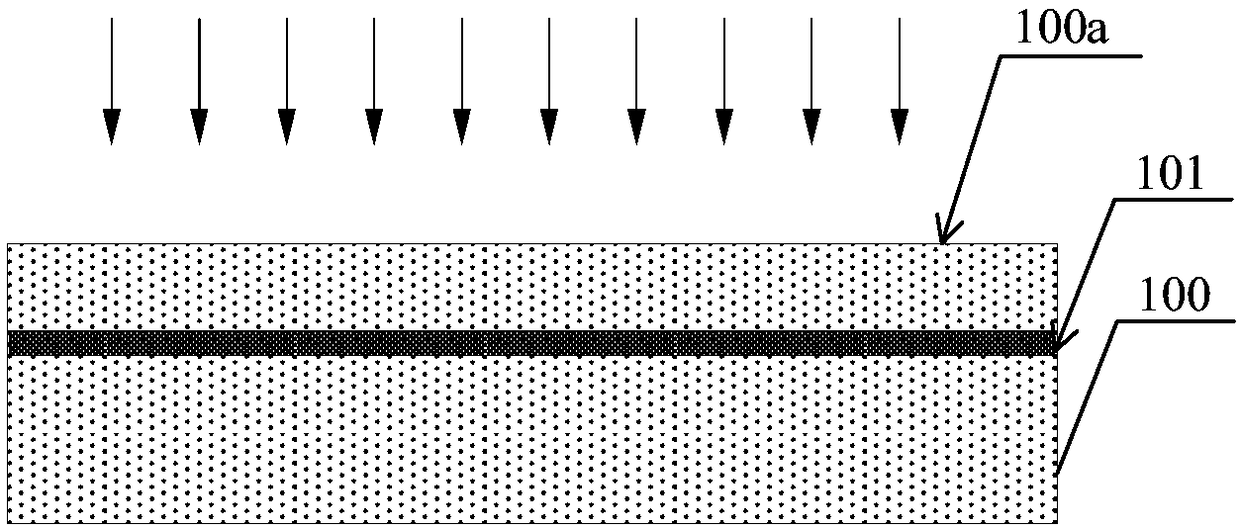

Method for preparing thin film heterostructure

InactiveCN108336219AReduce thermal strainAvoid chippingPiezoelectric/electrostrictive/magnetostrictive devicesOptoelectronicsIon implantation

The invention provides a method for preparing a thin film heterostructure. The method comprises the steps of providing a wafer substrate with an injection surface; conducting ion injection from the injection surface on the wafer substrate to form an injection defect layer at the predetermined depth of the wafer substrate; providing a support substrate, and performing temperature rising bonding onthe support substrate and the wafer substrate; annealing a obtained structure to form a continuous defect layer; stripping part of the wafer substrate through external force assisting, and forming wafer film on the wafer substrate to obtain a thin film heterostructure including the support substrate and the wafer film. The method can reduce the thermal strain of a bonding structure through the temperature rising bonding, so that the bonding structure remains stable and complete in the high-temperature process, and avoid the problem of film cracking caused by thermal mismatch in the stripping process, the bonding structure is separated from the continuous defect layer through the external force assisting method, so that no effect is caused on a bonding interface, and an external force assisting stripping method can reduce stripping temperature and stripping time, thereby reducing the cumulative effect of thermal stress in a piezoelectric crystal.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

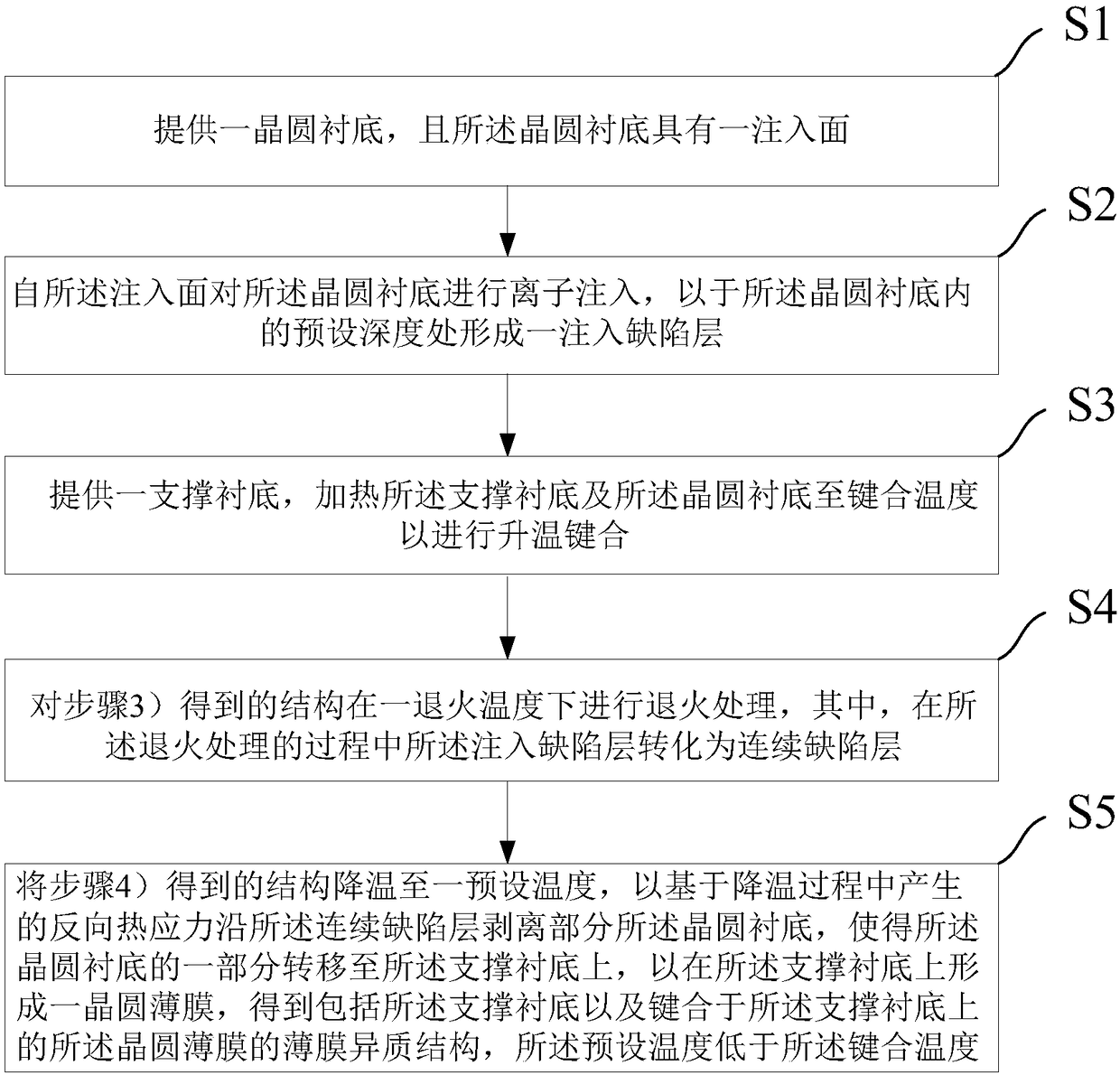

Thin film heterostructure preparation method

ActiveCN108493334ALow annealing temperatureShorten process timePiezoelectric/electrostrictive/magnetostrictive devicesOptoelectronicsHigh-temperature corrosion

The invention provides a thin film heterostructure preparation method. The method comprises steps: a wafer substrate with an injection surface is provided; ion implantation is carried out on the wafersubstrate from the injection surface, and an injection defect layer is formed at a preset depth in the wafer substrate; a support substrate is provided, and the support substrate and the wafer substrate are subjected to temperature rise bonding; the obtained structure is subjected to annealing treatment to form a continuous defect layer; the temperature of the obtained structure is reduced to a preset temperature, reverse thermal stress generated based on temperature reduction strips part of the wafer substrate along the continuous defect layer, and a thin film heterostructure comprising thesupport substrate and the wafer thin film is obtained, wherein the preset temperature is lower than the bonding temperature. In the temperature rise bonding mode, the thermal stress of the bonding structure can be reduced, the bonding structure can keep stable and complete in a high temperature process, the problem of wafer crack generated by thermal mismatch in the stripping process can be effectively solved, and through the reverse thermal stress assisting method, the bonding structure is separated at the continuous defect layer and a bonding interface is not influenced.

Owner:上海新硅聚合半导体有限公司

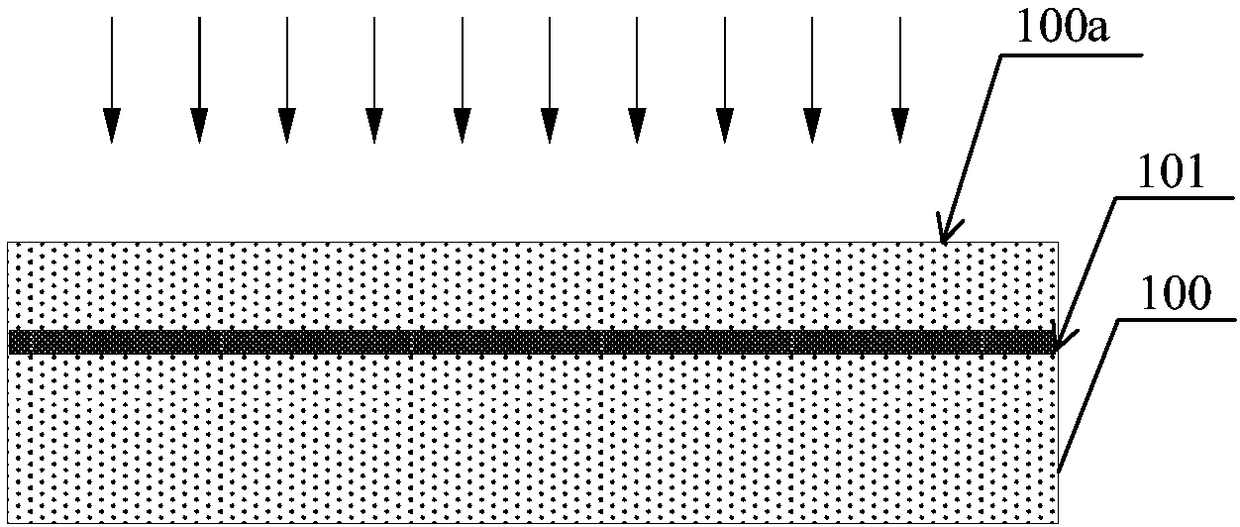

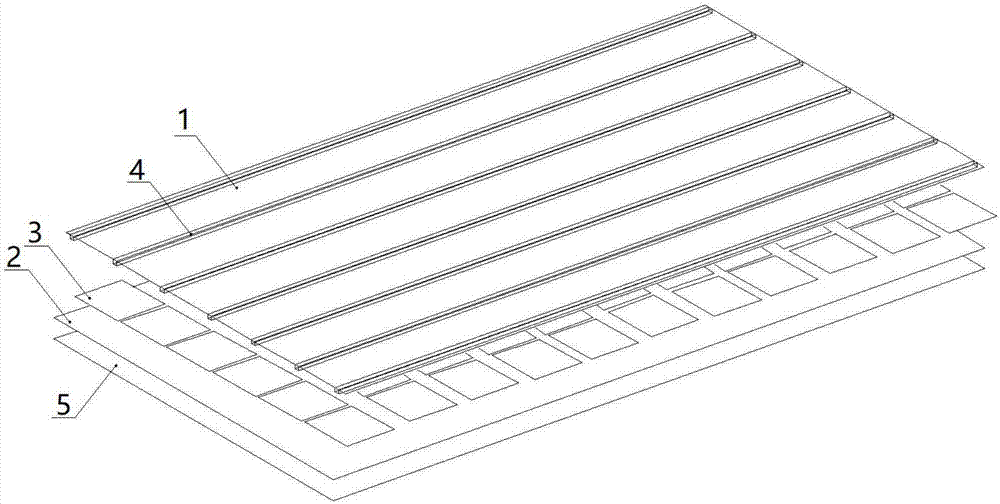

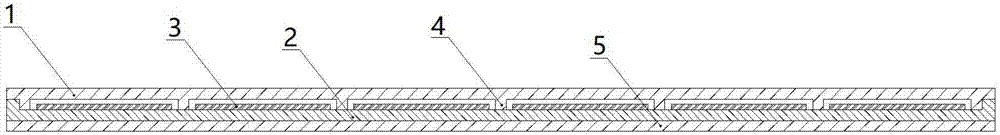

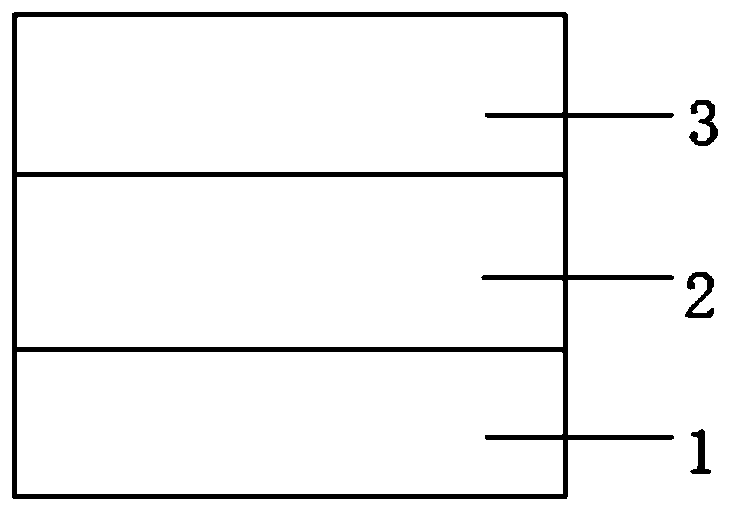

Ultra-light flexible crystalline silicon solar cell module and preparation method thereof

ActiveCN105322039AReduce weightLight in massPhotovoltaic energy generationSemiconductor devicesAdhesiveEngineering

The invention discloses an ultra-light flexible crystalline silicon solar cell module and a preparation method thereof. The ultra-light flexible crystalline silicon solar cell module comprises a front film, a solar cell, a support material, packaging adhesives and a rear film, wherein the front film, the packaging adhesive, the solar cell, the packaging adhesive, the support material and the rear film are sequentially arranged and are molded in a vacuum hot-pressing manner. The preparation method comprises the following steps: sequentially laminating the front film, the packaging adhesive, the solar cell, the packaging adhesive, the support material and the rear film from top to bottom; and carrying out a solidification under the vacuum conditions that the temperature is 100-150 DEG C and the pressure is 15Kpa to 30Kpa for 30-60 minutes, so as to obtain the ultra-light flexible crystalline silicon solar cell module. The ultra-light flexible crystalline silicon solar cell module disclosed by the invention has the advantages of high generating efficiency, flexibility, light weight and the like; the preparation method disclosed by the invention is integral molding; and the process is simple.

Owner:48TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

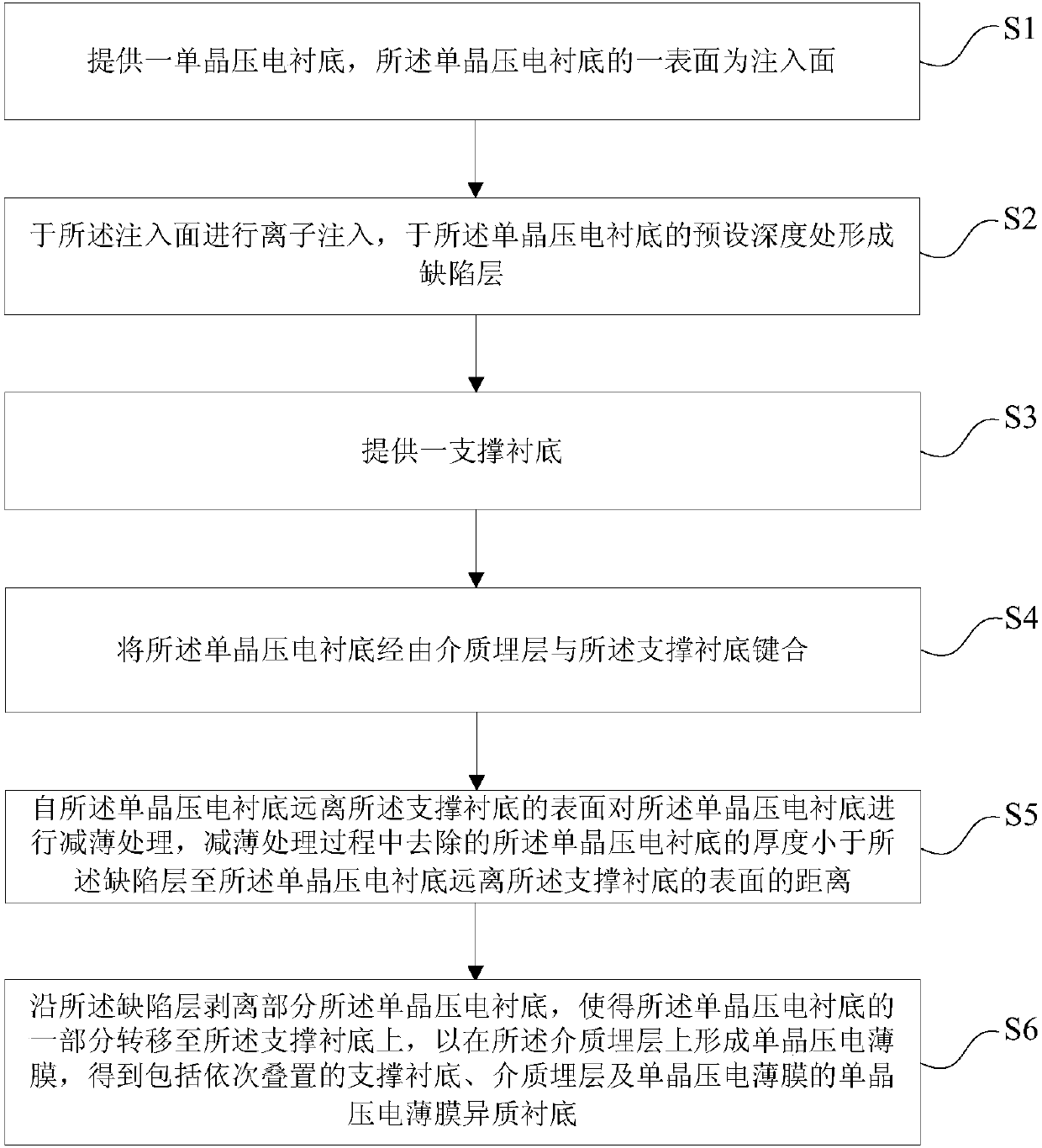

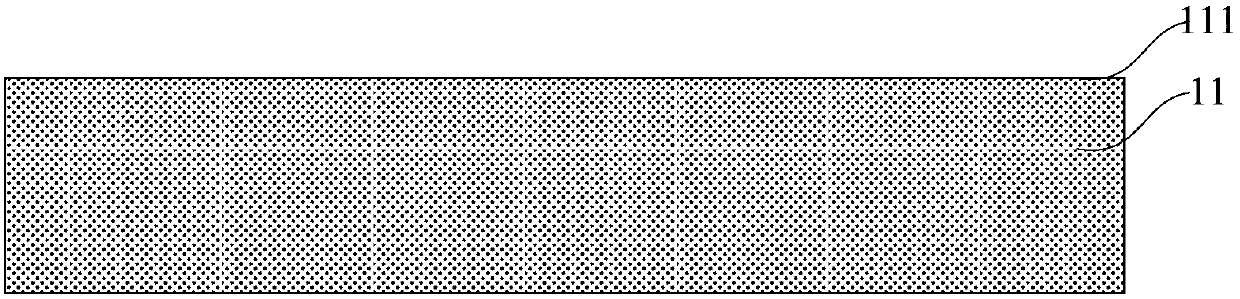

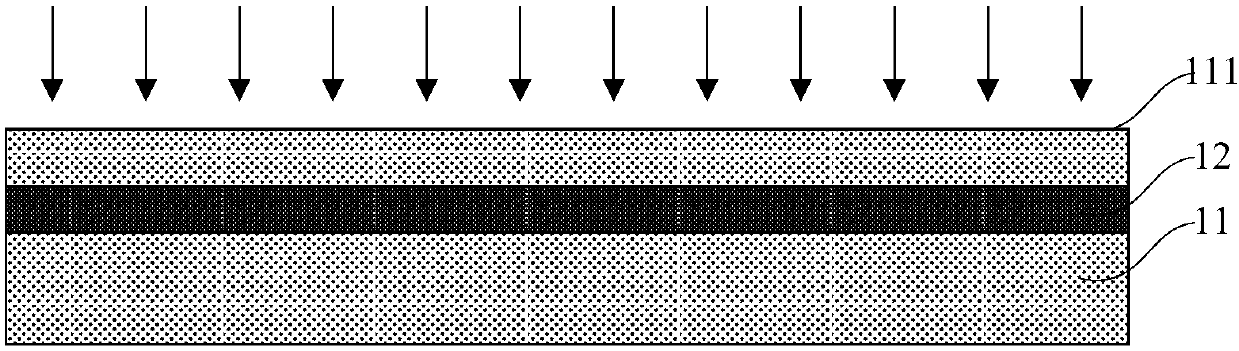

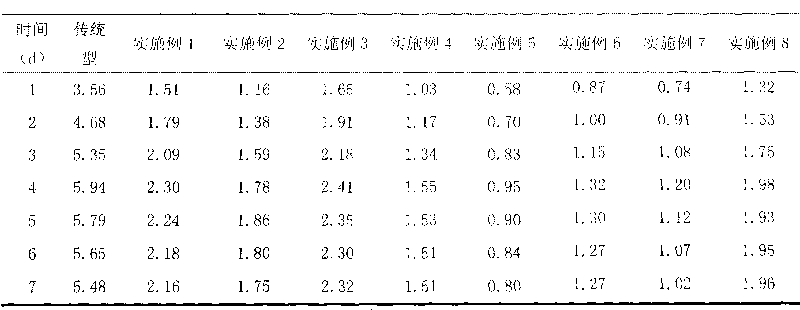

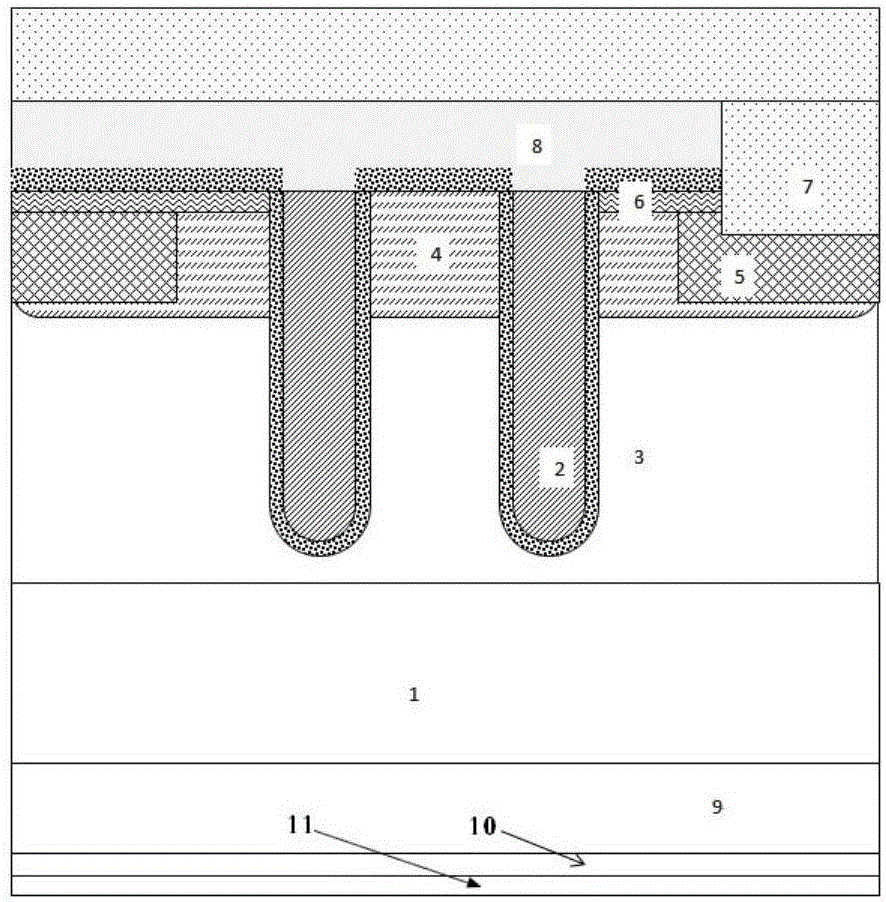

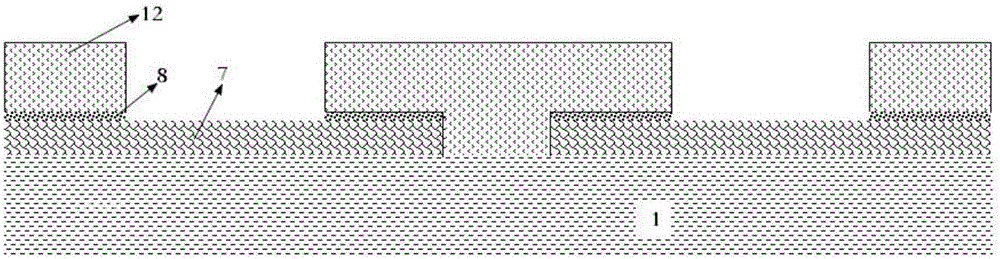

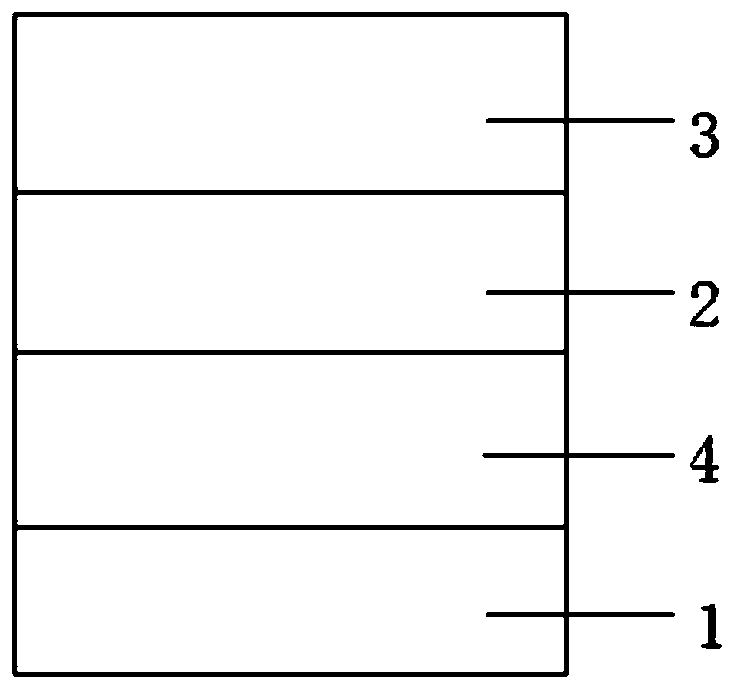

Preparation method of monocrystal piezoelectric film heterogeneous substrate

ActiveCN110137341ASolving Thermal Mismatch ProblemsAvoid splintersPiezoelectric/electrostrictive/magnetostrictive devicesDielectricSingle crystal

The invention provides a preparation method of a monocrystal piezoelectric film heterogeneous substrate. The method comprises the following steps of: 1) providing a monocrystal piezoelectric substrate, wherein one surface of the monocrystal piezoelectric substrate is an implantation surface; 2) performing ion implantation at the implantation surface, and forming a defect layer at the preset depthof the monocrystal piezoelectric substrate; 3) providing a support substrate; 4) bonding the monocrystal piezoelectric substrate with the support substrate through a dielectric buried layer; 5) performing thinning treatment of the monocrystal piezoelectric substrate from the surface, far away from the support substrate, of the monocrystal piezoelectric substrate; and 6) stripping part of the monocrystal piezoelectric substrate along the defect layer to obtain a monocrystal piezoelectric film heterogeneous substrate comprising the support substrate, the dielectric buried layer and the monocrystal piezoelectric film which are stacked in order. The monocrystal piezoelectric substrate is thinned prior to forming of the monocrystal piezoelectric film heterogeneous substrate through stripping along the defect layer, and then stripping is performed along the defect layer to reduce the thermal mismatching between the monocrystal piezoelectric substrate and the support substrate and avoid generation of the problem of cracking caused by thermal mismatch in the stripping process.

Owner:SHANGHAI NOVEL SI INTEGRATION TECH CO LTD

Film-coating premixing auxiliary material and preparation method thereof

ActiveCN101691429AGood dispersionGood flexibilityPharmaceutical delivery mechanismMethacrylic acid-ethyl acrylate copolymerPolyethylene glycol

The invention relates to a film-coating premixing auxiliary material which mainly comprises hydroxypropyl methylcellulose, polyvinylpyrrolidone-vinyl acetate copolymer (6:4), polyvinyl alcohol-polyethylene glycol copolymer, methacrylic acid-ethyl acrylate copolymer (1:1), polyethylene glycol, talcum powder and a colorant. The film-coating premixing auxiliary material has the advantages of favorable dampproof and anti-cracking properties, can disintegrate at a suitable time and uses water as dissolvent.

Owner:浙江瓯伦包衣技术有限公司

Fermented selenium-enriched fruit and vegetable plant pressed candies and processing method thereof

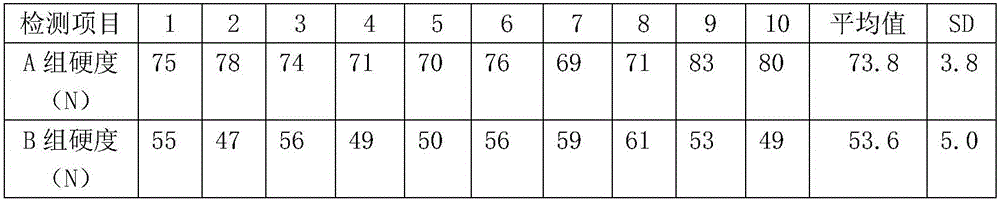

InactiveCN106035958ALittle elasticityImprove featuresYeast food ingredientsConfectioneryAlcohol sugarsHardness

The invention provides a fermented selenium-enriched fruit and vegetable plant pressed candy which comprises the following raw material components in percentage by mass: 40-80% of dried fermented selenium-enriched fruit and vegetable plant powder, 15-40% of plant or edible mushroom extract and 5-30% of saccharides or sugar alcohol. Furthermore, the invention provides a method for processing the fermented selenium-enriched fruit and vegetable plant pressed candy. According to the invention, the fermented selenium-enriched fruit and vegetable plants serve as raw materials, so that the pressing technology of the pressed candies can be improved, the elasticity of the raw materials is reduced, the candies are prevented from being cracked or loosened, the press hardness is improved, absorption of nutritive materials is promoted, and special odor or taste of partial raw materials introduced into the pressed candies can be improved.

Owner:恩施德源硒材料工程科技有限公司

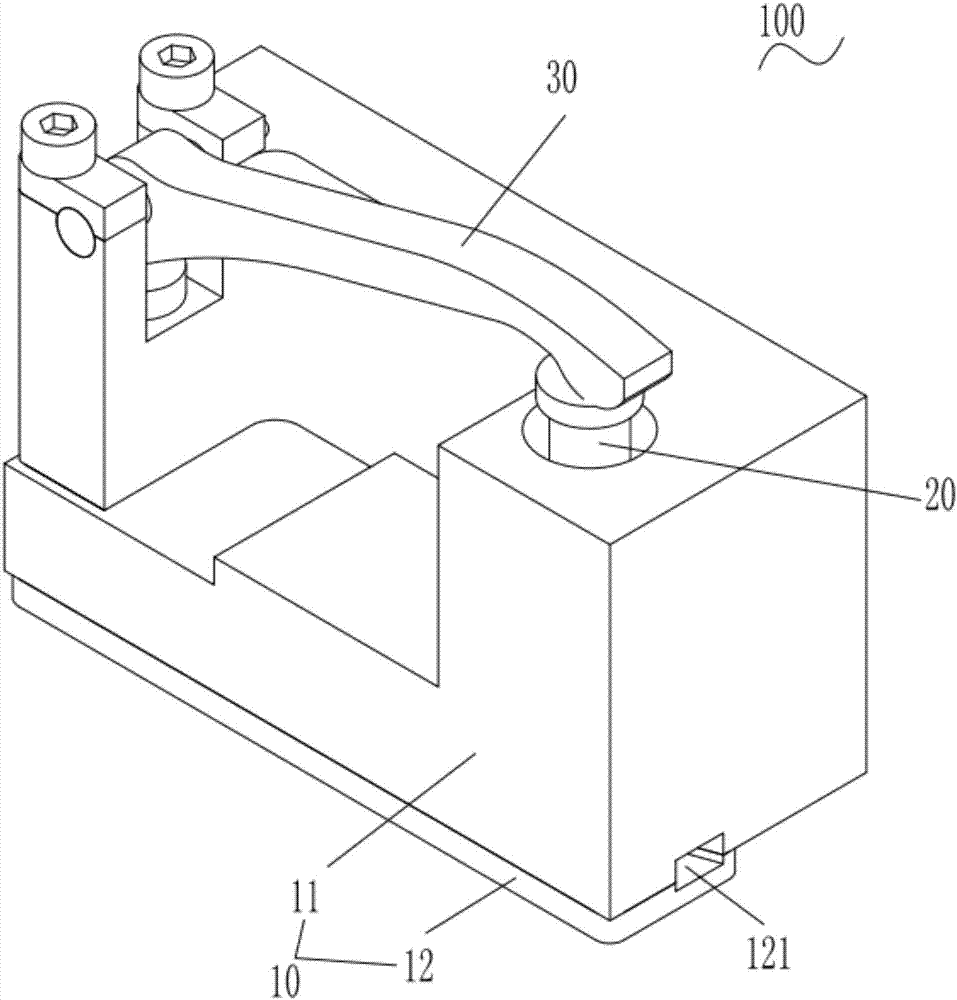

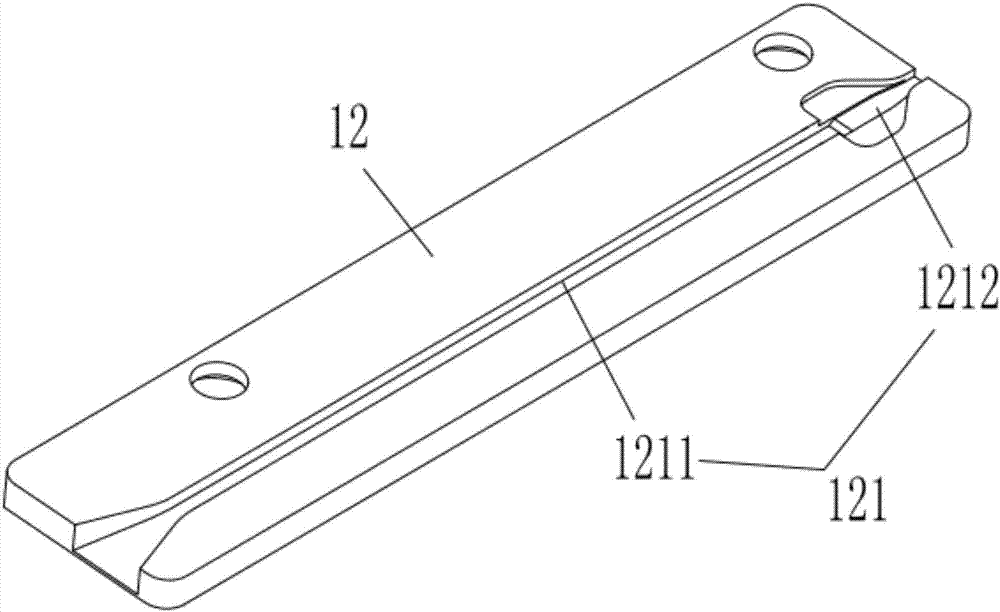

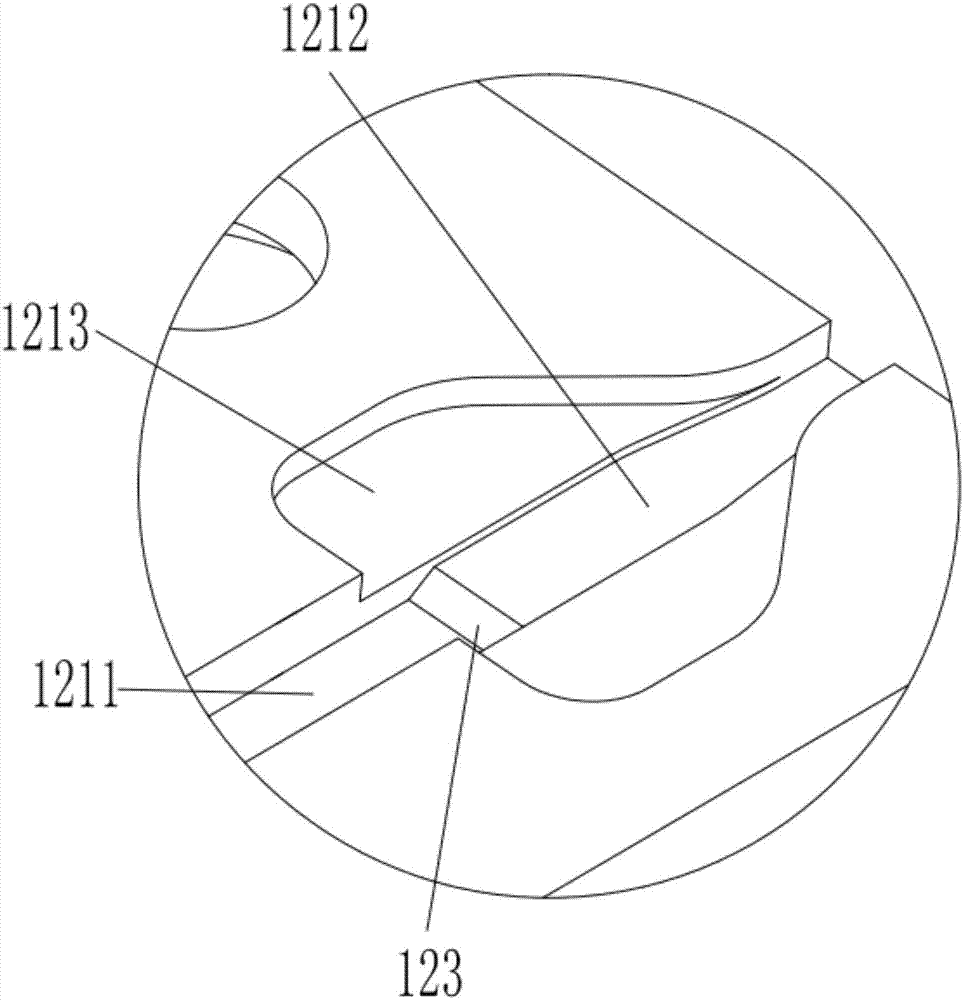

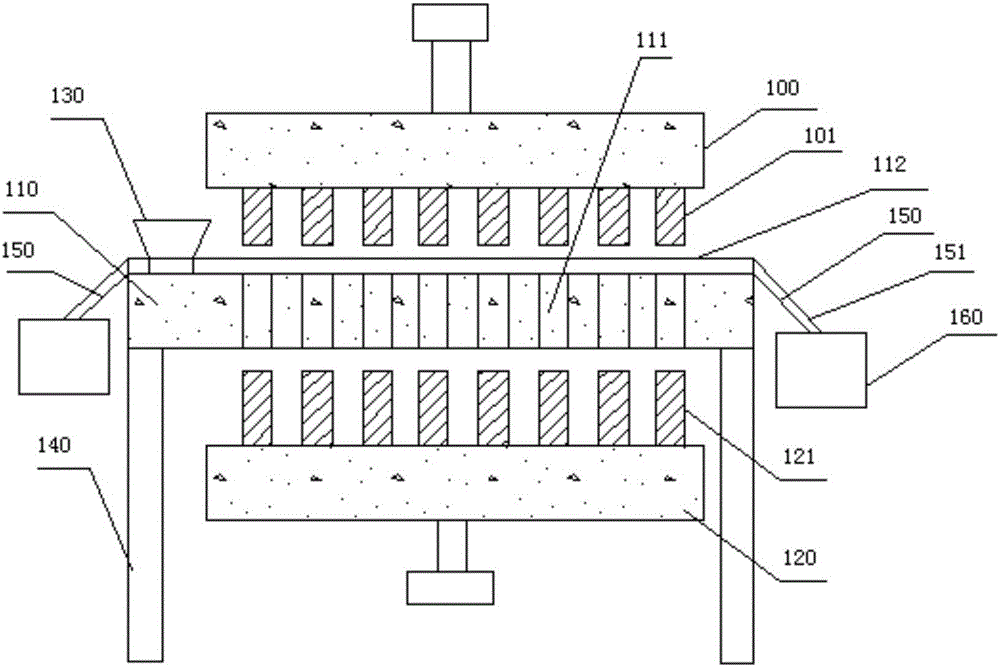

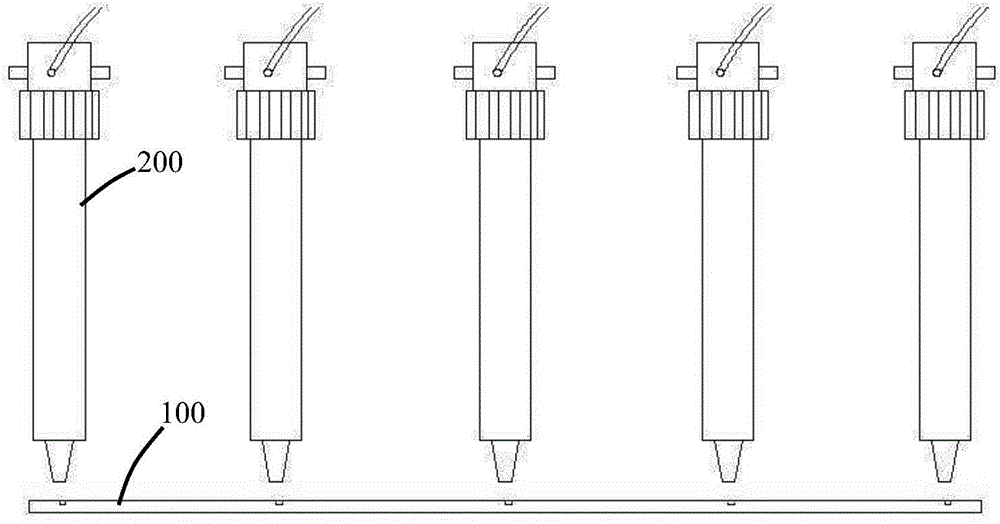

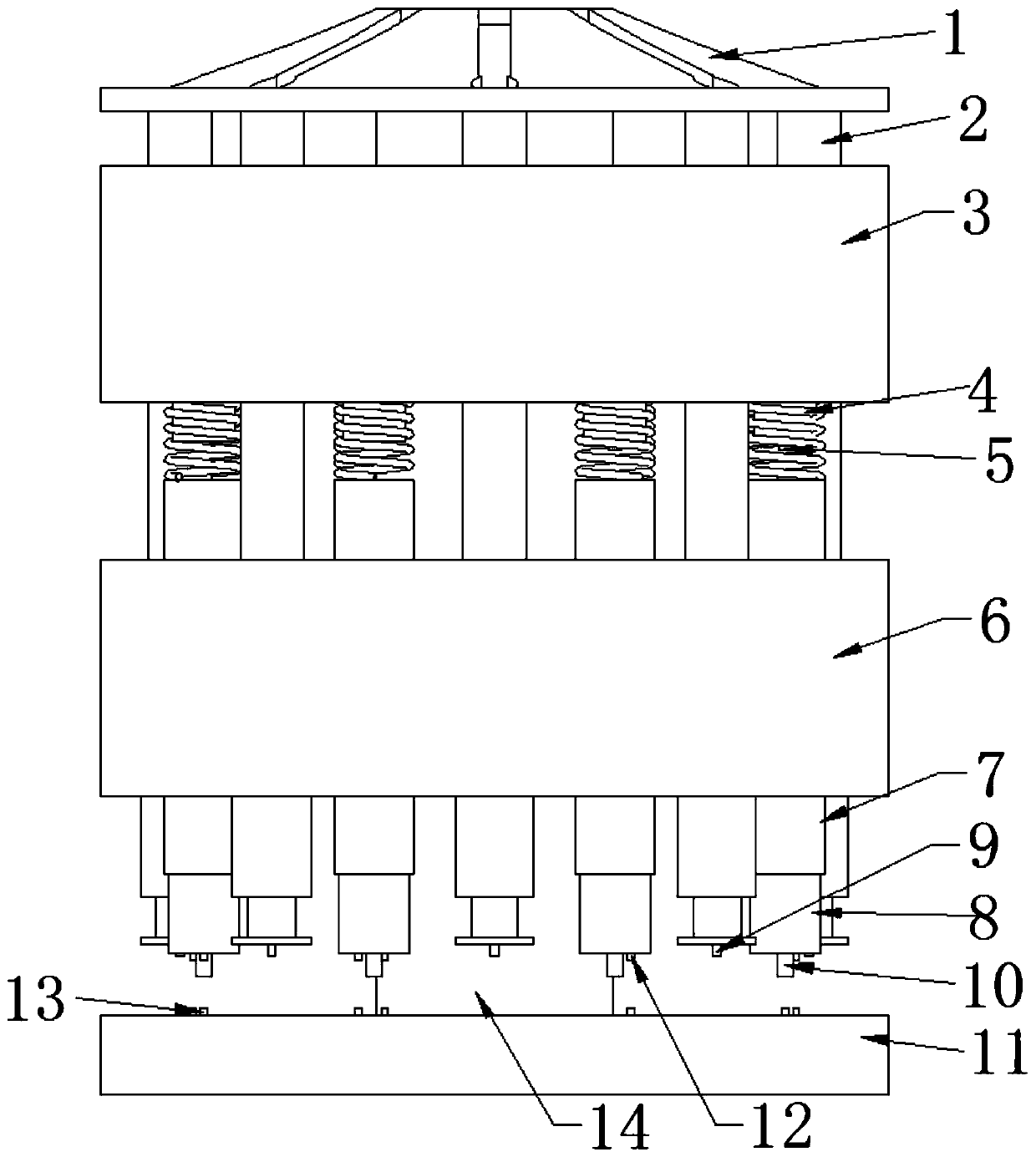

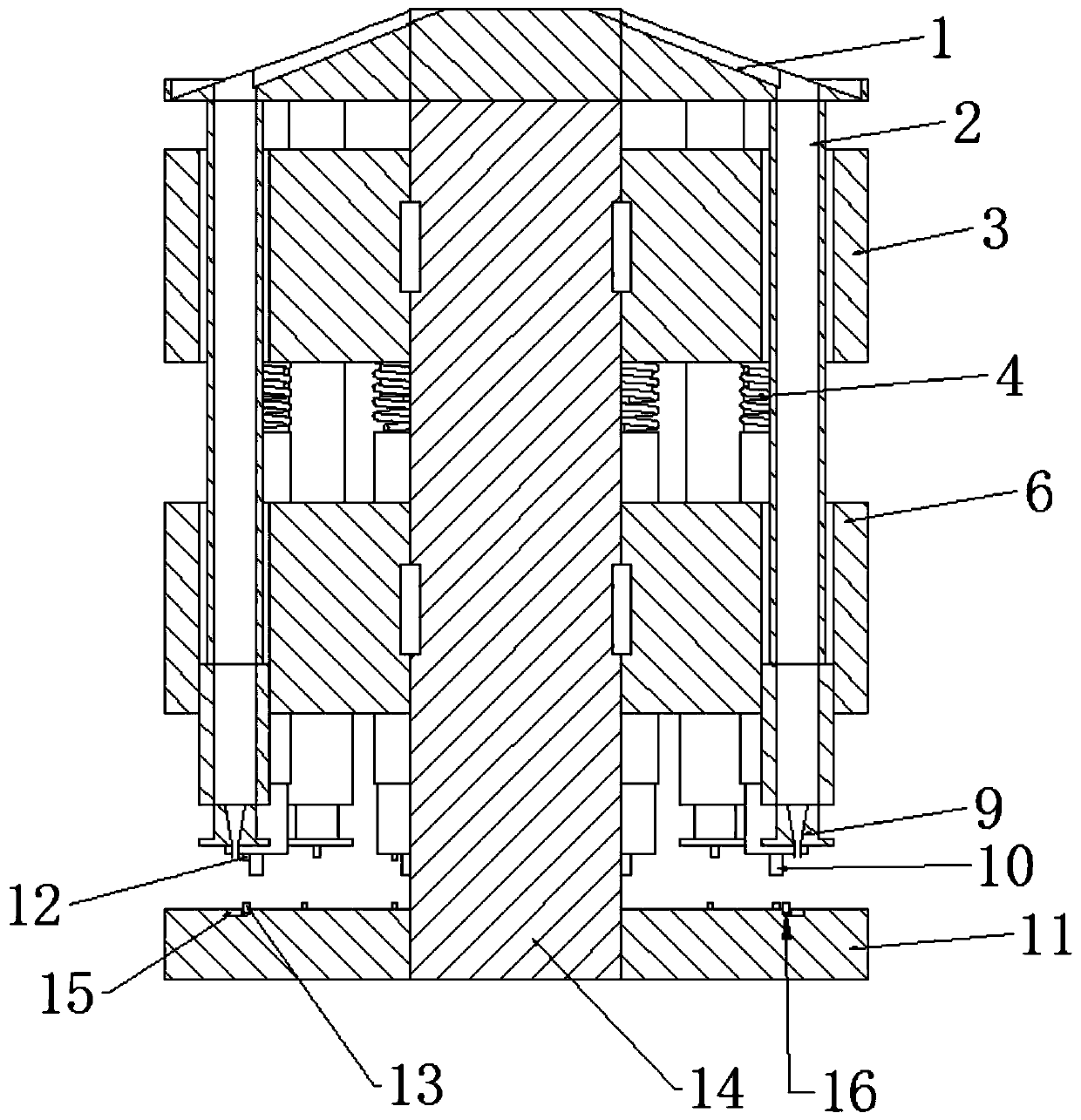

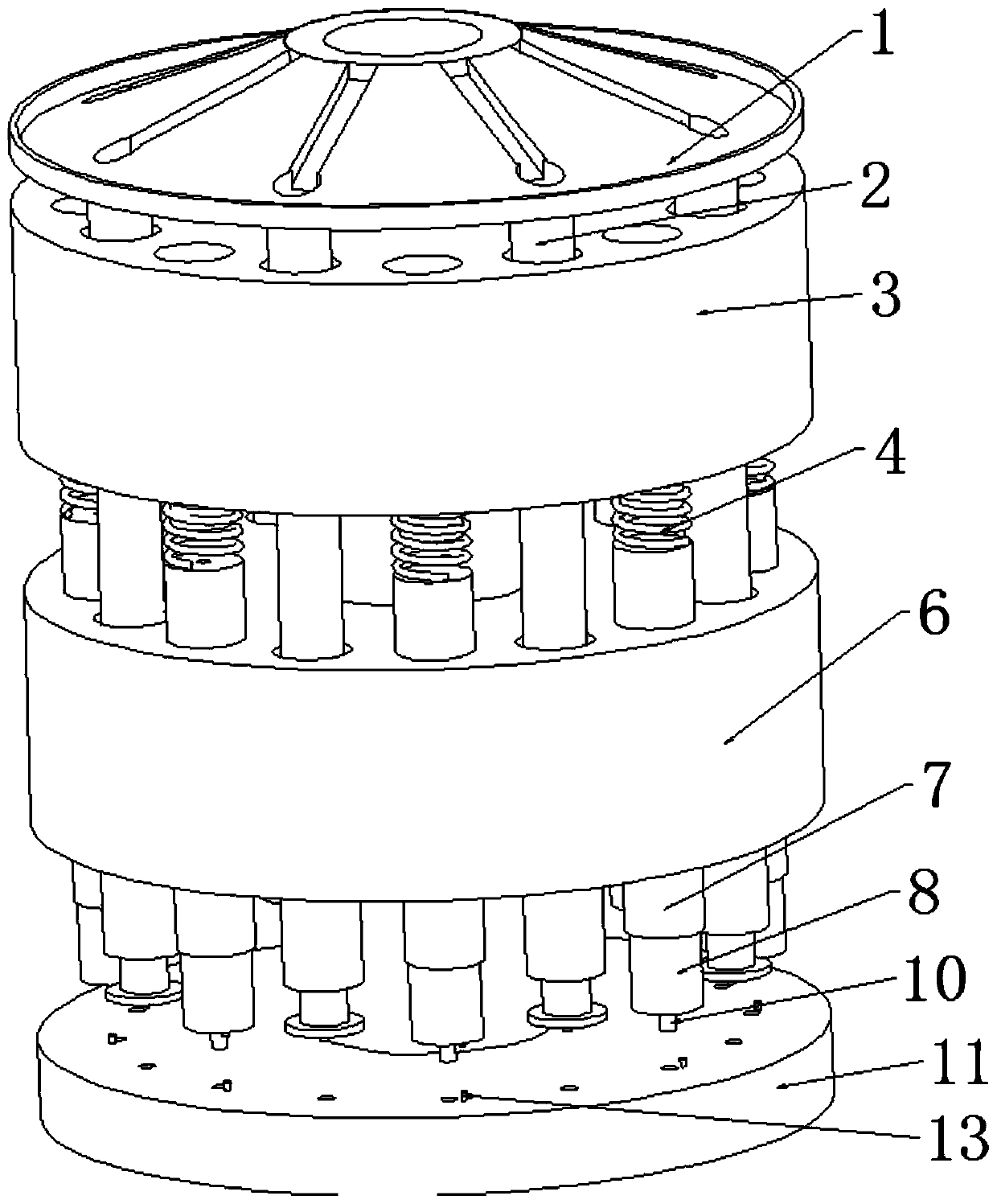

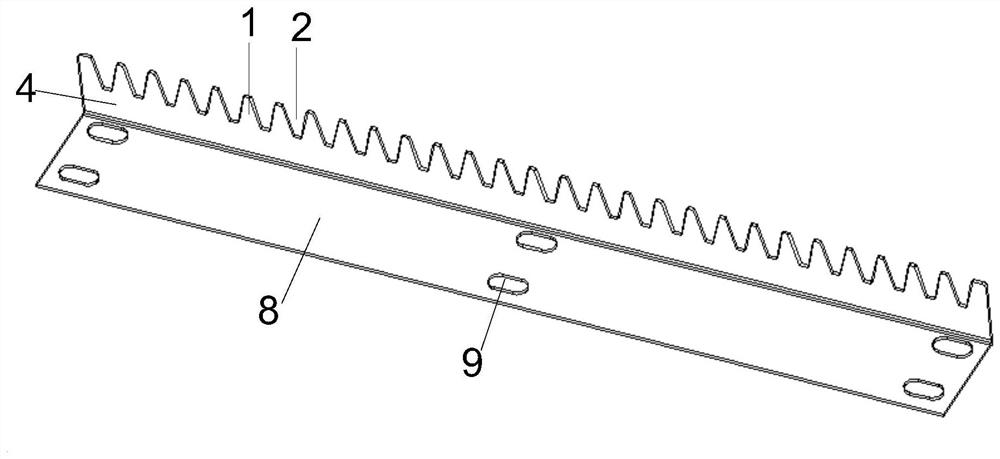

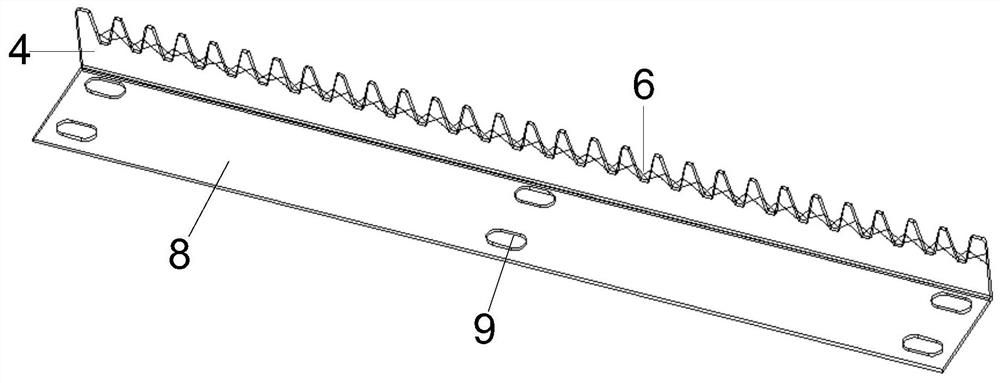

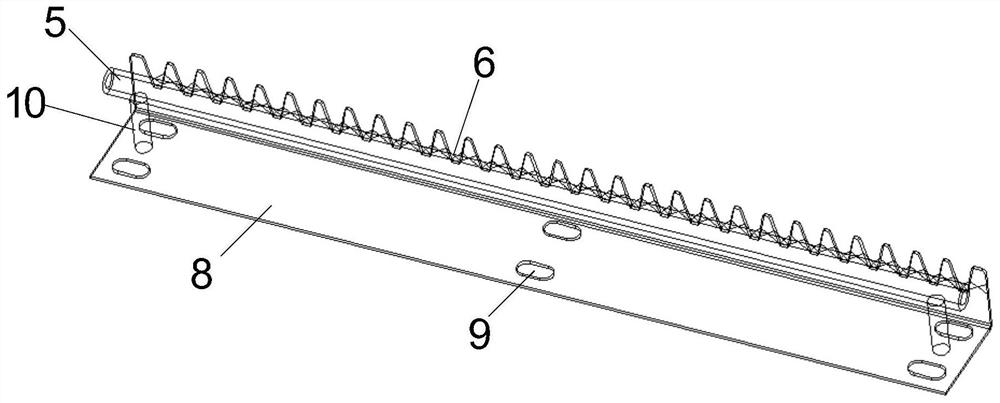

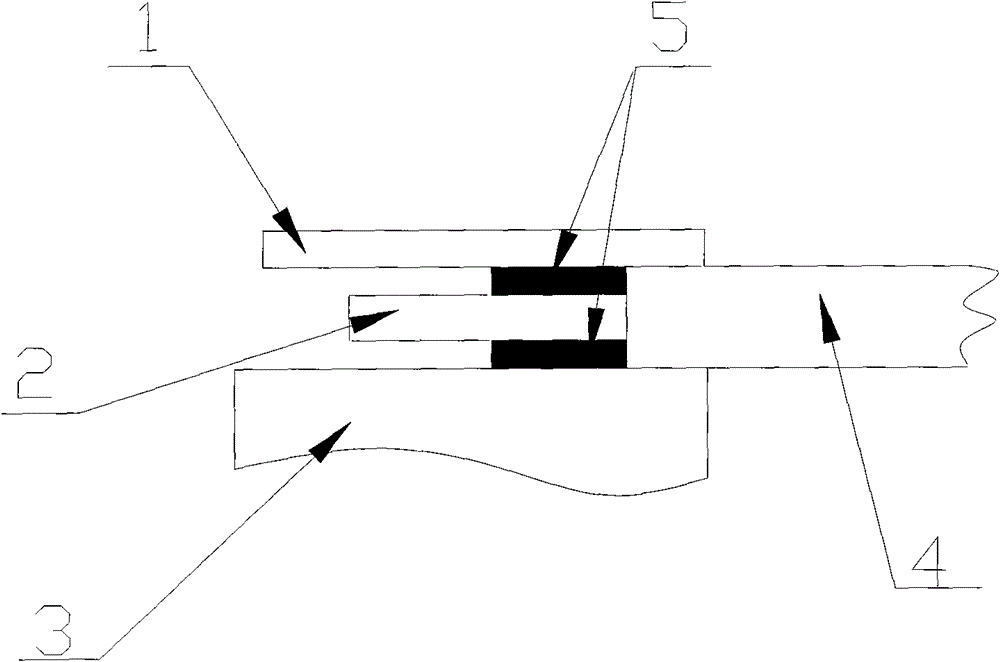

Segmental shaping device and method of round soldering strip and series welding machine

ActiveCN106876522AAvoid splintersFinal product manufactureSemiconductor devicesSolderingMechanical engineering

A segmental shaping device of a round soldering strip comprises a base, a first driving mechanism and a shaping mechanism, wherein a soldering strip passage is arranged at the bottom of the base and is used for the soldering strip to pass through, one end of the shaping mechanism is overlapped with the first driving mechanism, the other end of the shaping mechanism is arranged above the soldering strip passage at the bottom of the based so that the shaping mechanism is driven to vertically move relative to the base by the first driving mechanism and the shaping of the round soldering strip arranged under the shaping mechanism is further implemented by an acting force between the bottom of the shaping mechanism and the bottom of the base. The driving mechanism drives the shaping mechanism to vertically move, and the shaping of the soldering strip in the soldering strip passage at the bottom of the base is further implemented; and the round soldering strip shaped by employing the method is used for connection between dense-grating battery pieces and connection between half battery pieces, so that the battery pieces and the soldering strip of a battery piece connection segment are flat, and the battery pieces and the battery piece connection segment can be effectively prevented from broken during the lamination process.

Owner:宁夏小牛自动化设备股份有限公司 +2

Preparation method for TEM sample

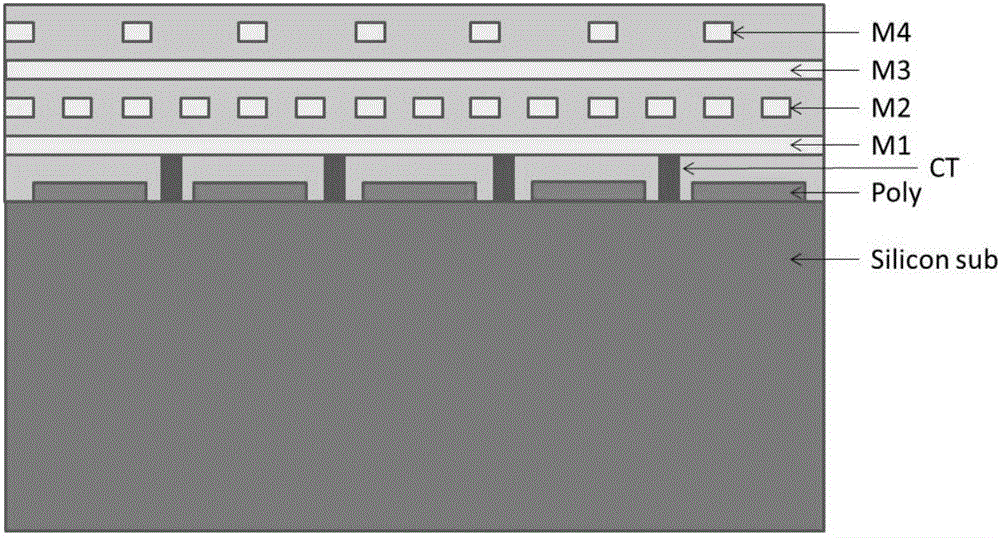

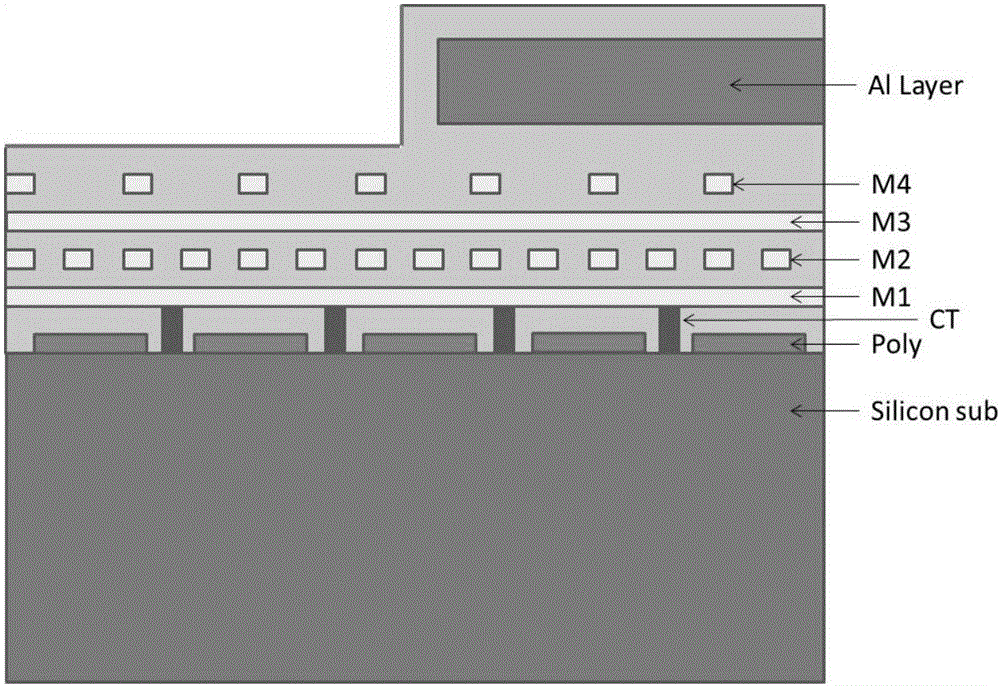

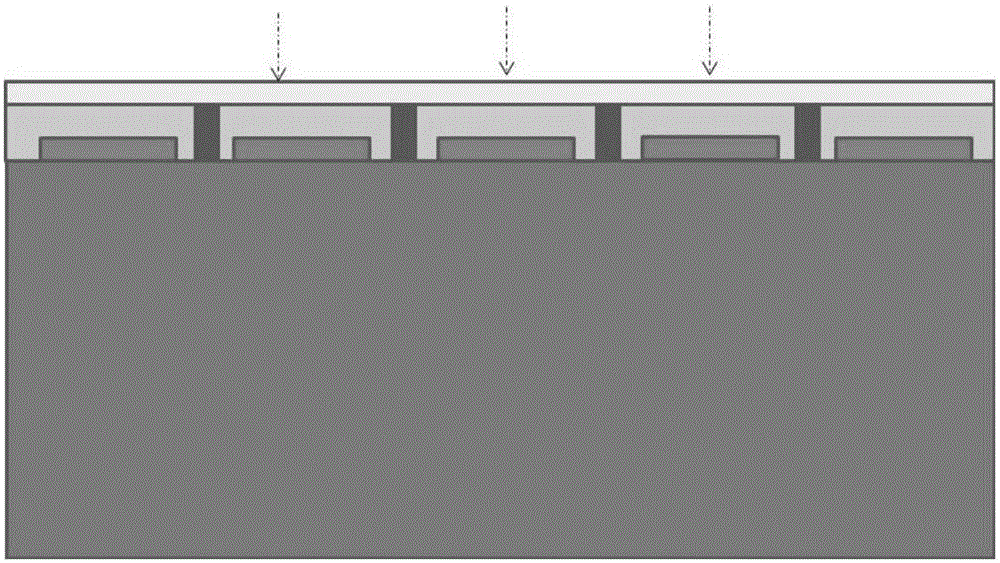

ActiveCN105699698AAvoid processing powerAvoid reactionScanning probe techniquesIon beamCombinatorial chemistry

Disclosed in the invention is a preparation method for a TEM sample. An inclined cutting opening is formed in a chip sample surface by using an ion beam and level removing and TEM sample preparation are carried out on a target area position directly, so that time for TEM sample preparation is substantially shortened; and the position and depth for level removing are controlled precisely, so that the success rate of sample preparation and the quality of the sample are improved. And the chip sample is protected from being damaged.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Ultra-light flexible crystalline silicon solar cell module and preparation method thereof

ActiveCN105322039BReduce weightLight in massPhotovoltaic energy generationSemiconductor devicesPlastic packagingEngineering

The invention discloses an ultra-light flexible crystalline silicon solar cell component and a preparation method thereof. The ultra-light flexible crystalline silicon solar cell component includes a front film, a solar cell, a supporting material, an encapsulation glue and a back film, and the front film, the encapsulation glue, The solar cell, encapsulant, supporting material and rear mold are arranged in sequence and formed by vacuum thermocompression. The preparation method is: stack the front film, encapsulant, solar cell, encapsulant, support material and rear mold in sequence from top to bottom, under vacuum conditions with a temperature of 100°C to 150°C and a pressure of 15Kpa to 30Kpa , cured for 30 min to 60 min to obtain an ultra-light flexible crystalline silicon solar cell module. The ultra-light flexible crystalline silicon solar cell module of the invention has the advantages of high power generation efficiency, flexibility, light weight, etc., and the preparation method of the invention is integrally formed, and the process is simple.

Owner:48TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

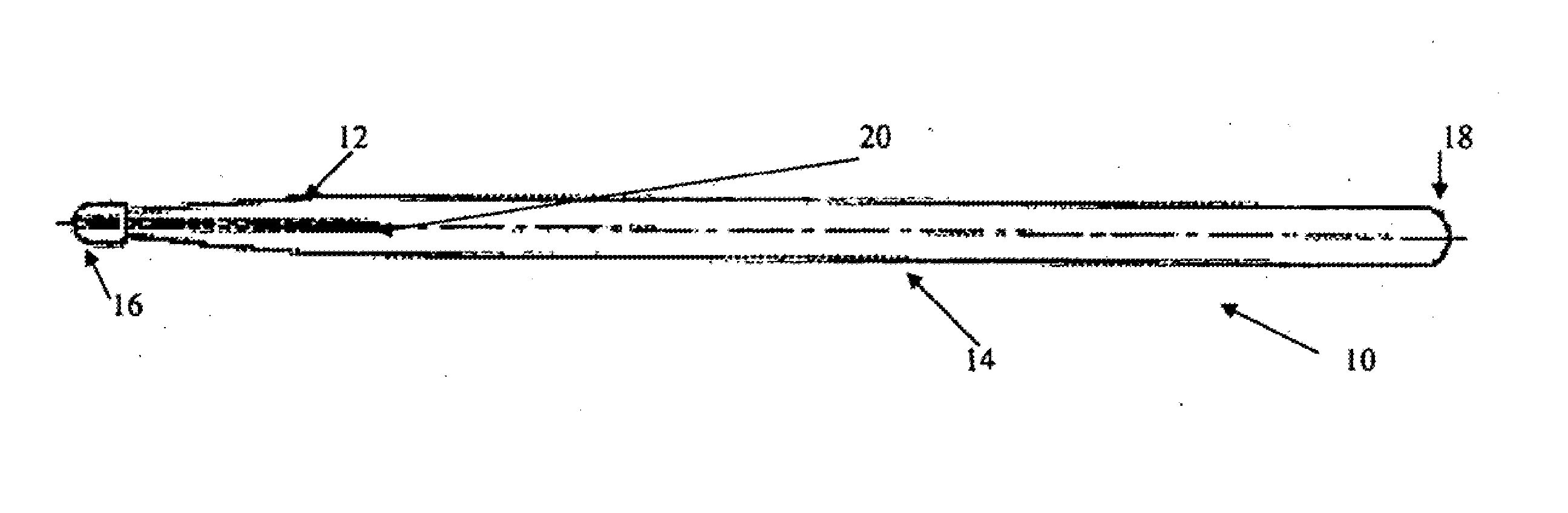

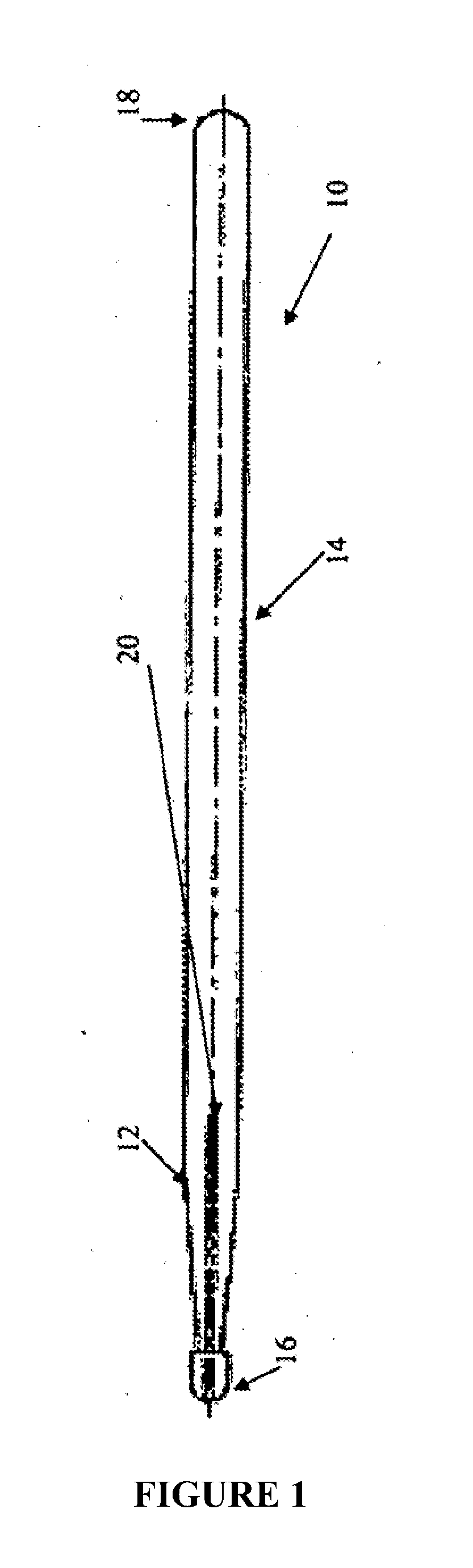

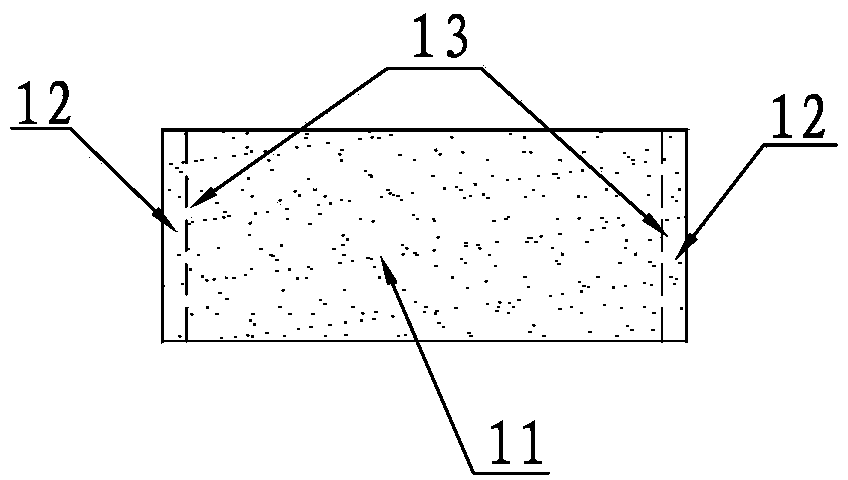

Reinforced drum stick

InactiveUS20110162512A1High strengthIncreased durabilityPercussion musical instrumentsEngineeringMechanical engineering

A reinforced drum stick (10) having a butt portion (14) and a striking portion (12), and a reinforcement means (20) extending from the striking portion (12) into at least a portion of the butt portion (14), the reinforcement means (20) adapted to prevent splintering, chipping, cracking, breaking or bowing of the drum stick (10), whilst retaining the feel and rebound characteristics of the dram stick (10), and enhancing the tonal consistency from drum stick (10) to drum stick (10).

Owner:WHITE WILLIAM JOHN

Camellia nitidissima lozenge and preparation method thereof

InactiveCN105725212APrevent oxidationPrevent escapeMetabolism disorderPharmaceutical non-active ingredientsOysterMagnesium stearate

The invention discloses a camellia nitidissima lozenge and a preparation method thereof. The camellia nitidissima lozenge comprises the following components in parts by weight: 40-50 parts of camellia nitidissima, 5-10 parts of spirulina, 15-20 parts of trepan, 20-30 parts of oyster, 3-5 parts of xylitol, 2-3 parts of an arhat fruit extract, 7-9 parts of microcrystalline cellulose and 5-7 parts of magnesium stearate. In the preparation process, a carbon dioxide supercritical extraction method is adopted to extract effective components such as general flavones and tea polyphenol in camellia nitidissima at relatively low temperature, oxidation and diffusion of thermosensitive substances can be effectively prevented, no solvent residue can be generated, and the quality of the camellia nitidissima lozenge can be improved.

Owner:马占平 +2

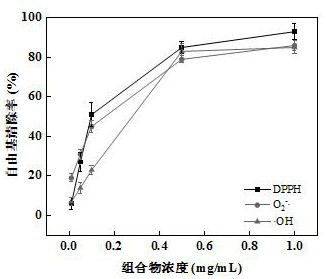

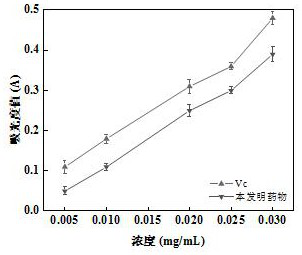

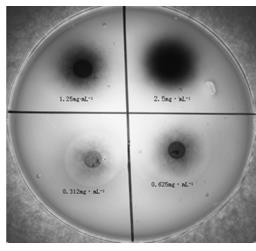

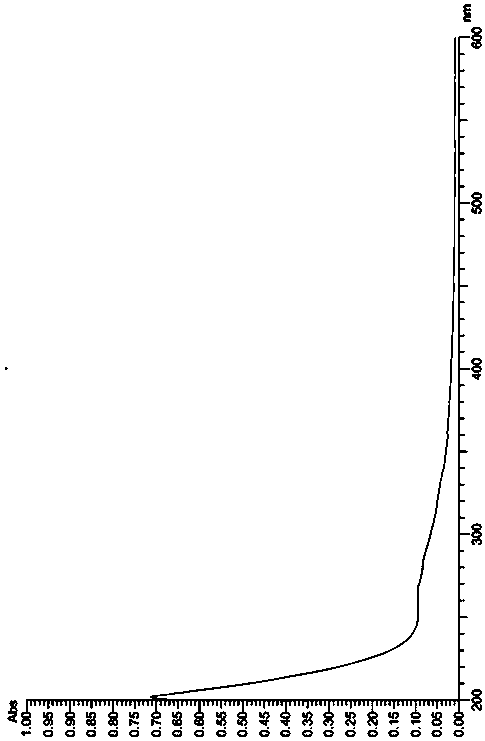

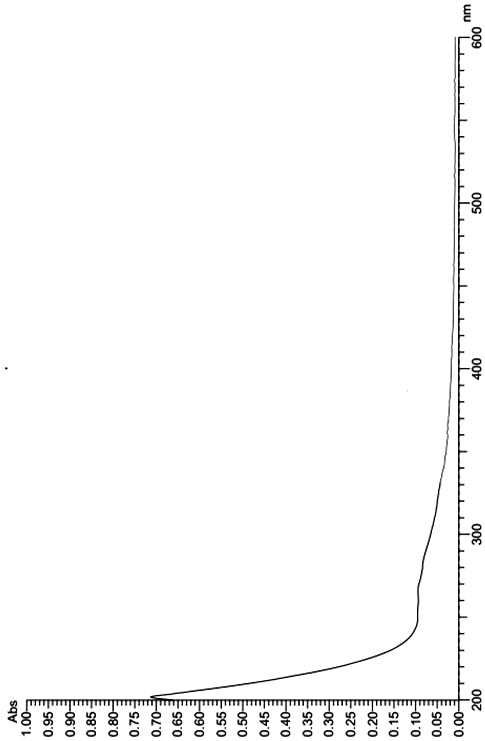

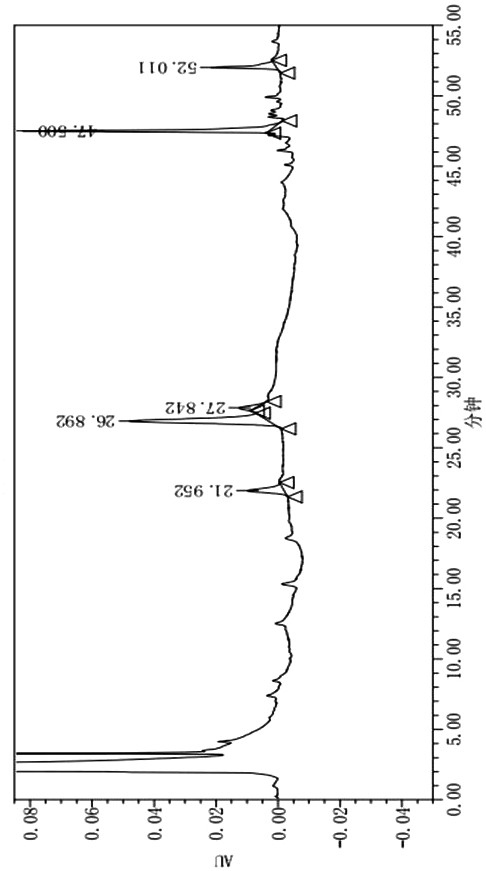

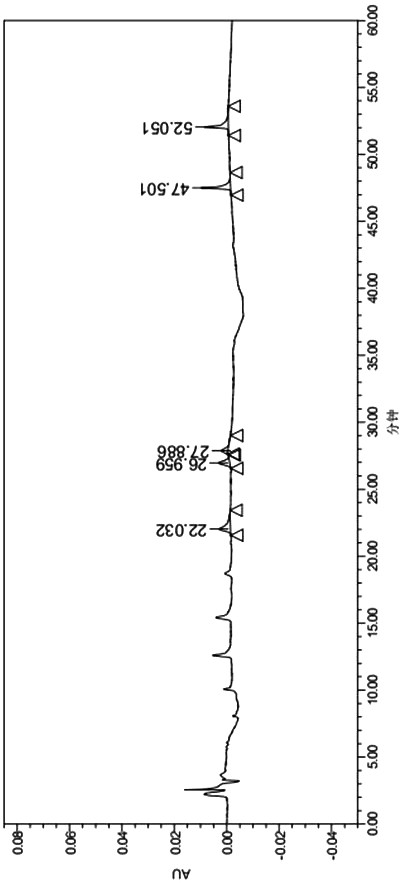

Anthocyanin-contained composition and application thereof

InactiveCN113143908AStrong reductionEnhanced Antioxidant MechanismOrganic active ingredientsPowder deliveryEscherichia coliSuperoxide

The invention relates to the field of medicinal use of anthocyanin and discloses an anthocyanin-contained composition and application thereof. If anthocyanin is extracted from grape skin, the composition is applied to antioxidation drugs, plays a role in clearing away DPPH free radicals, superoxide anion free radicals (O2<->.) and hydroxyl free radicals (.OH) and has a relatively high reducing property; if the anthocyanin is extracted from mulberries, the composition is applied to bacteriostatic drugs and plays a role in inhibiting staphylococcus aureus, Escherichia coli and bacillus subtilis; and the composition can also be applied to blood sugar reducing, blood fat reducing and atherosclerosis inhibiting and plays a role in inhibiting intestinal alpha-glucosidase, the blood sugar reducing activity of acarbose is enhanced obviously, the synthesis of fats is inhibited, the decomposition of the fats is stimulated, and the composition has blood sugar reducing and blood fat reducing actions and can be used for inhibiting expression of adhesion molecules and inhibiting formation of atherosclerosis.

Owner:HUAIYIN INSTITUTE OF TECHNOLOGY

Temperature measuring device and temperature measuring method

ActiveCN104155019AAccurately obtain temperature valuesTemperature controlThermometer detailsThermometers using electric/magnetic elementsMeasuring instrumentThermocouple

The invention discloses a temperature measuring device and a temperature measuring method. The temperature measuring device comprises an insulated body, a thermocouple, and a temperature measuring instrument, wherein the insulated body is provided with a mounting groove; the thermocouple is arranged in the mounting groove; a wiring groove is formed in the insulated body; the wiring groove is communicated with the mounting groove; a wire is arranged in the wiring groove; one end of the wire is electrically connected with the thermocouple and the other end extends out from the wiring groove; and the temperature measuring instrument is electrically connected with the other end of the wire for receiving electrical signals converted by the thermocouple. The temperature measuring device of the invention can accurately acquire the temperature value on the surface of a cell in the case of hot air welding through simulating the processing environment when the cell is welded, and thus, during the actual welding process of the cell, the temperature on the surface of the cell can be effectively controlled, and cracking can be prevented.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

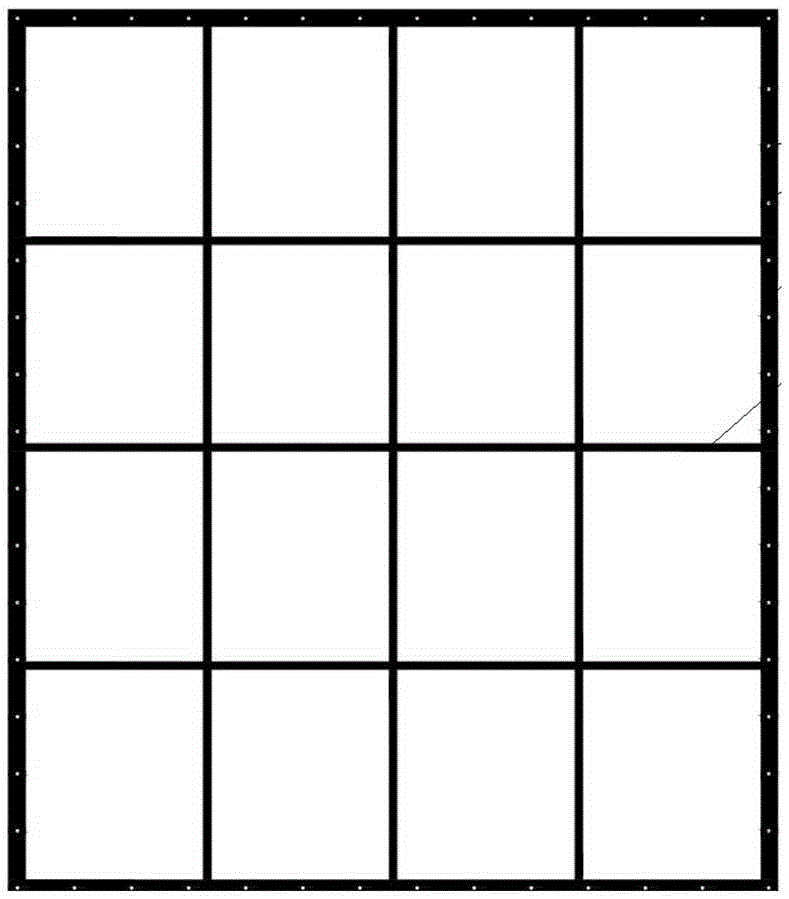

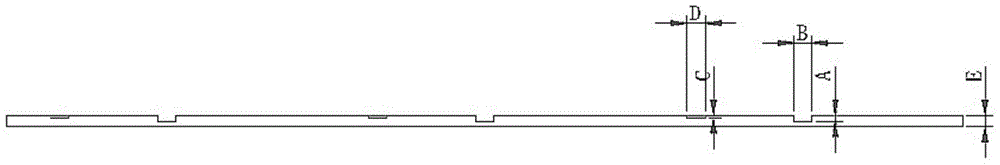

Sub-ingot silicon rod with technology protection ends and production method

InactiveCN103526289AAvoid splintersPrevent missing cornersPolycrystalline material growthFine working devicesIngotEngineering

The invention discloses a sub-ingot silicon rod with technology protection ends and a production method. The sub-ingot silicon rod with technology protection ends is composed of a silicon slice cutting section and technology protection sections arranged at two ends of the silicon slice cutting section. Because the technology protection sections are arranged at two ends of the sub-ingot silicon rod to be sliced in advance, during the cutting process, the technology protection ends arranged at two ends of the sub-ingot silicon rod can protect the outermost silicon slices, and no conditions of slice falling, corner missing, edge breaking and the like happen. Breakage of cutting steel wires caused by slopes of two ends of the sub-ingot silicon rod can be avoided during the cutting process of silicon slices, conditions of slice cracking, corner missing, edge breaking and the like of outermost silicon slices can be prevented effectively, and the slice output rate of silicon rods and the qualified rate of silicon slices are ensured.

Owner:JIANGSU ZHAOJING PHOTOELECTRIC TECH DEV

Method for preventing wire cutting steel wires from being broken and improving silicon wafer yield

The invention discloses a method for preventing wire cutting steel wires from being broken and improving the silicon wafer yield. The method includes the steps of sub-ingot-blank cutting, sub-ingot-silicon-rod cutting, sub-ingot-silicon-rod bonding and cutting steel wire distribution cutting, wherein each sub-ingot-silicon-rod is composed of a silicon wafer cutting section and process protection sections, and the process protection sections are arranged at the two ends of the silicon wafer cutting sections. When the cutting steel wires are distributed, it is guaranteed that the two steel wires, located on the outer sides, in each set of cutting steel wires are located inside the corresponding silicon wafer cutting section. Due to the fact that the process protection sections are reserved at the two ends of the sub-ingot-silicon-rods to be cut, in the silicon wafer cutting process, the process protection sections located at the two ends of the sub-ingot-silicon-rods have the protection effect on silicon wafers at the outmost ends, the defects of breakage, unfilled corners, edge breakage and the like of the silicon wafers can be prevented, the silicon wafer yield and the silicon wafer pass percent are improved, and the defect that the steel wires are broken due to uneven stress can also be effectively prevented.

Owner:JIANGSU ZHAOJING PHOTOELECTRIC TECH DEV

Method for improving stress on IGBT (insulated gate bipolar translator) back surface

InactiveCN106024626AIncrease stressAvoid splintersSemiconductor/solid-state device manufacturingSemiconductor devicesStress distributionEngineering

The invention discloses a method for improving stress on an IGBT (insulated gate bipolar translator) back surface. With regard to polyimide which covers a passivation layer on the front surface of a silicon wafer, the exposure of a scribing groove on the polyimide is changed from a bright state into a dark state in the photoetching definition for the scribing groove; after exposure is performed, the polyimide in the scribing groove is kept, so that the stress on the silicon wafer can be scattered, and the stress distribution on the silicon wafer can be improved; or, with regard to the polyimide which covers the passivation layer on the front surface of the silicon wafer, the exposure of the scribing groove on the polyimide is still kept at the bright state in the photoetching definition for the scribing groove so as to increase a dark virtual pattern; and after exposure is performed, the dark virtual pattern is transferred to the polyimide, so that uniform distribution can be formed on the polyimide layer.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

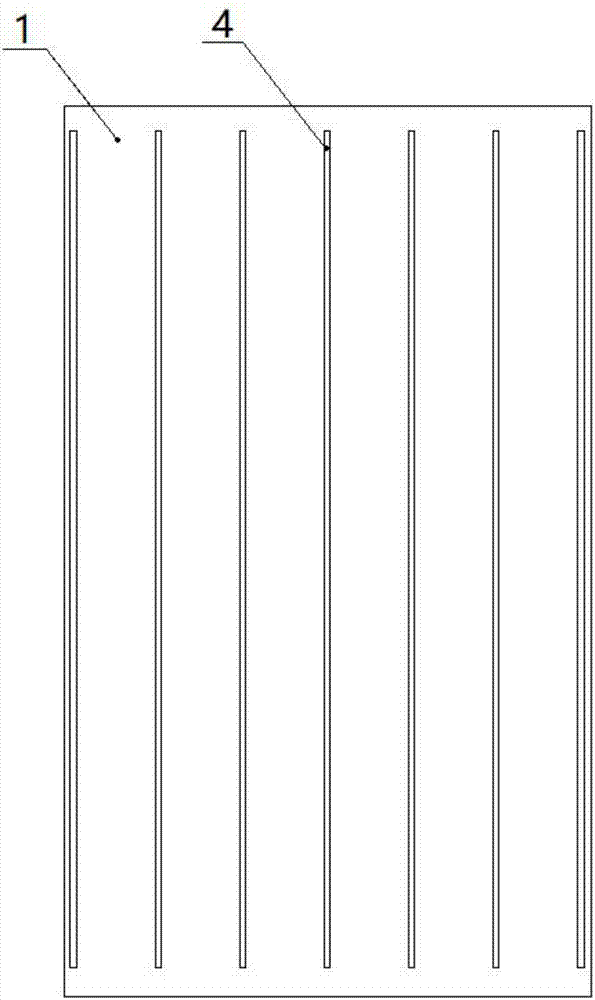

Tablet preparation device for avoiding tablet splitting

Owner:上海国创医药股份有限公司

Semiconductor structure, preparation method thereof, self-supporting gallium nitride layer and preparation method thereof

PendingCN111223763ASelf-strippingQuality assuranceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureGallium nitride

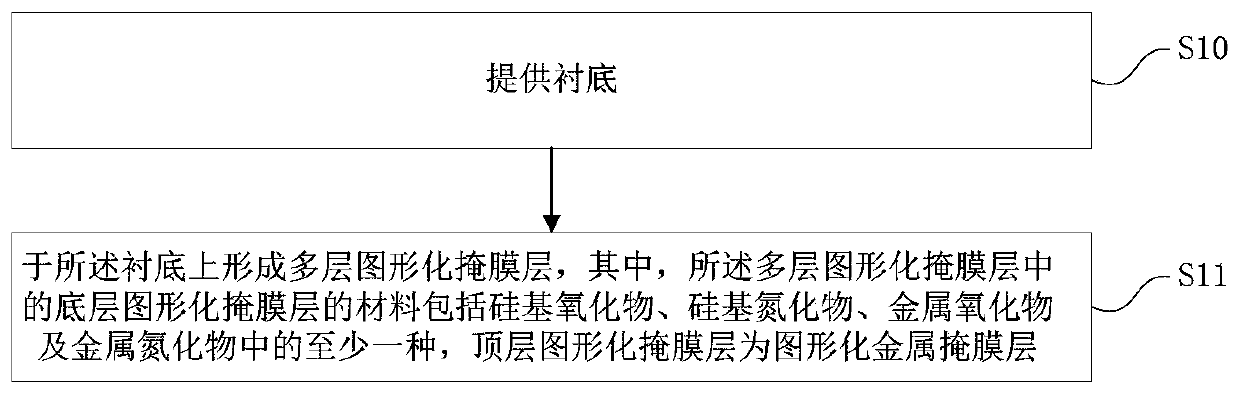

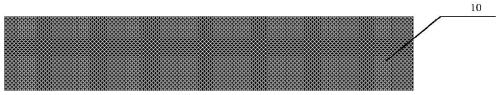

The invention relates to a semiconductor structure, a preparation method thereof, a self-supporting gallium nitride layer and a preparation method thereof. The preparation method of the semiconductorstructure comprises the steps of providing a substrate; forming a nitride buffer layer on the substrate; and forming a multi-layer graphical mask layer on the nitride buffer layer, wherein materials of a bottom graphical mask layer in the multi-layer graphical mask layer comprise at least one of silicon-based oxide, silicon-based nitride, metal oxide and metal nitride, and the top graphical mask layer is a graphical metal mask layer. According to the invention, self-stripping of the gallium nitride layer formed on the multi-layer graphical mask layer is facilitated; the quality of the galliumnitride layer formed on the multi-layer graphical mask layer is ensured; and the problem of influence on the quality of the gallium nitride layer due to cracking caused by only partial stripping in the stripping process in stripping of the metal mask layer is solved.

Owner:镓特半导体科技(上海)有限公司

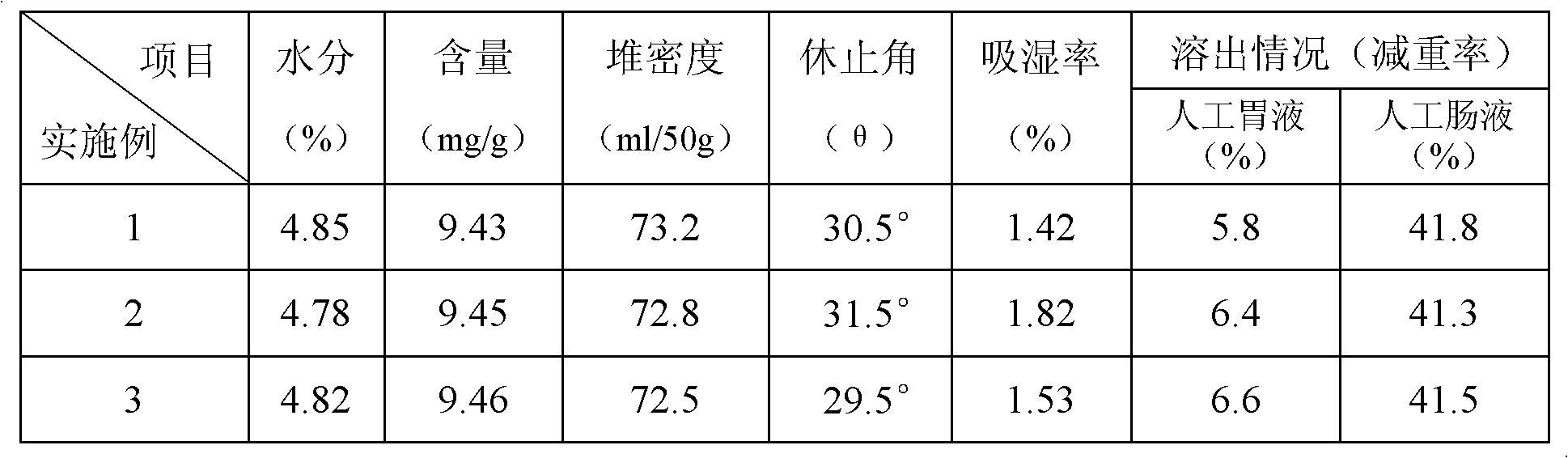

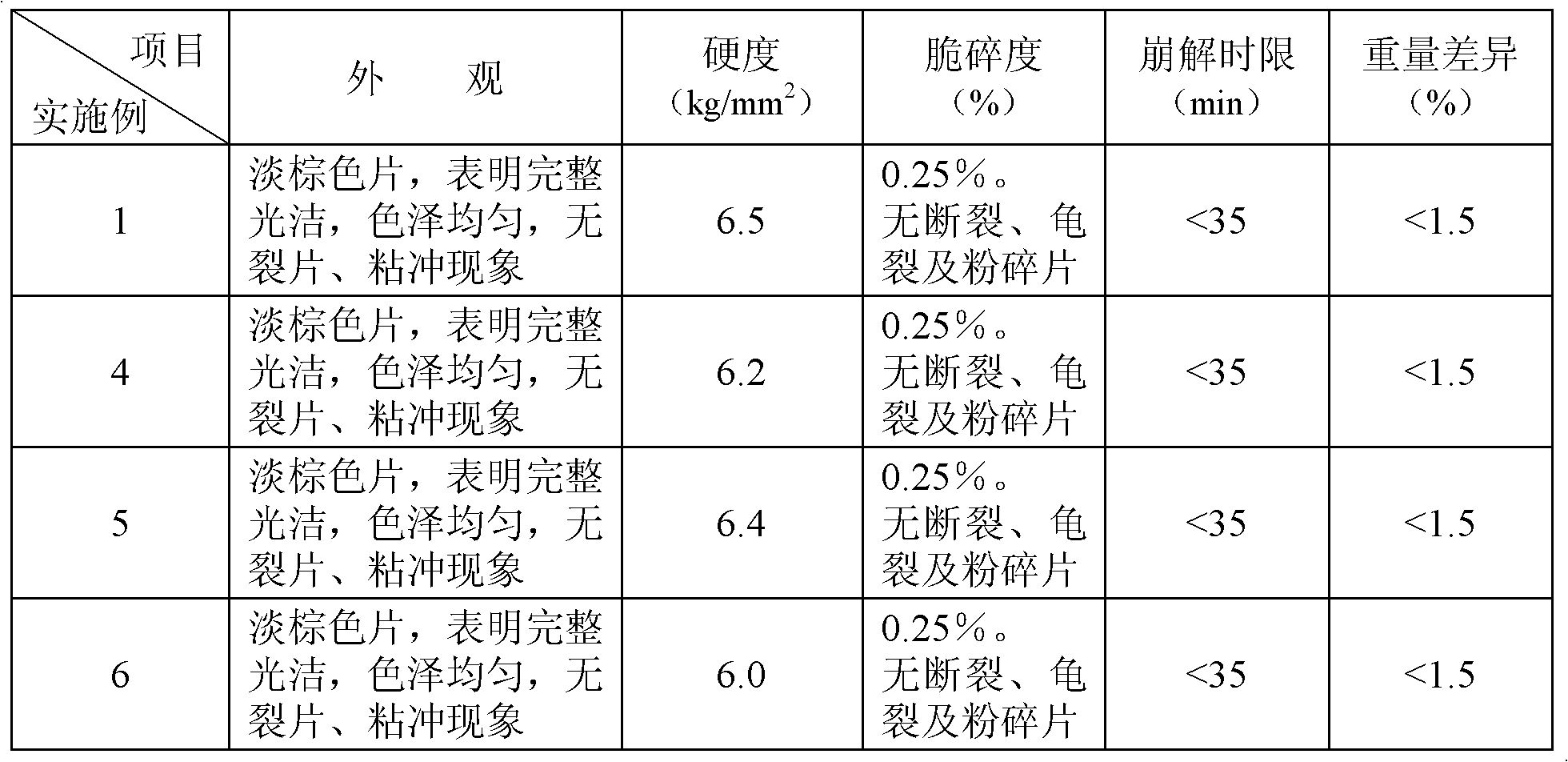

Method for preparing Gentongping tablets

ActiveCN102008592AImprove liquidityGood compressibilityAntipyreticAnalgesicsHigh probabilityMedicine

The invention discloses a method for preparing Gentongping tablets. The method comprises the following steps of: preparing Gentongping extract; preparing Gentongping extract particles by fluidized bed one-step granulation technology; coating the Gentongping extract particles by powder coating technology to prepare coated Gentongping extract particles; preparing Gentongping tablet cores by direct compression technology; and finally coating with thin films to prepare the Gentongping tablets. The preparation method solves the problems of dry extract, difficulty of crushing, high labor intensity, serious dust pollution, difficulty of process control during wet granulation, high probability of moisture absorption and deterioration of particles, poor fluidity, high probability of cracking and breaking, large tablet weight difference, poor hardness and the like existing in the preparation process of the conventional Gentongping tablets, overcomes the defect of stimulation to the stomach by the conventional Gentongping tablets, improves the medication safety, has the advantages of reliable process, stable quality, low labor intensity and the like, is easy to operate and is suitable for requirements of industrial production.

Owner:上海复旦复华药业有限公司 +1

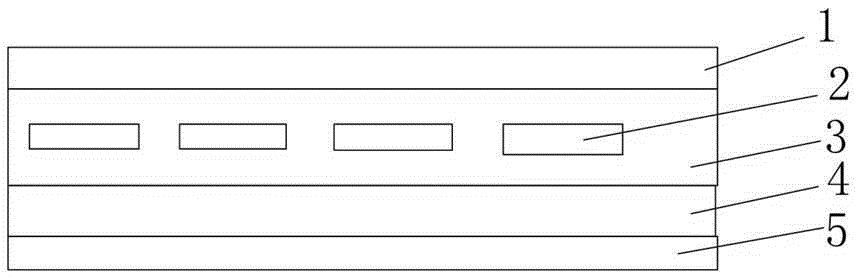

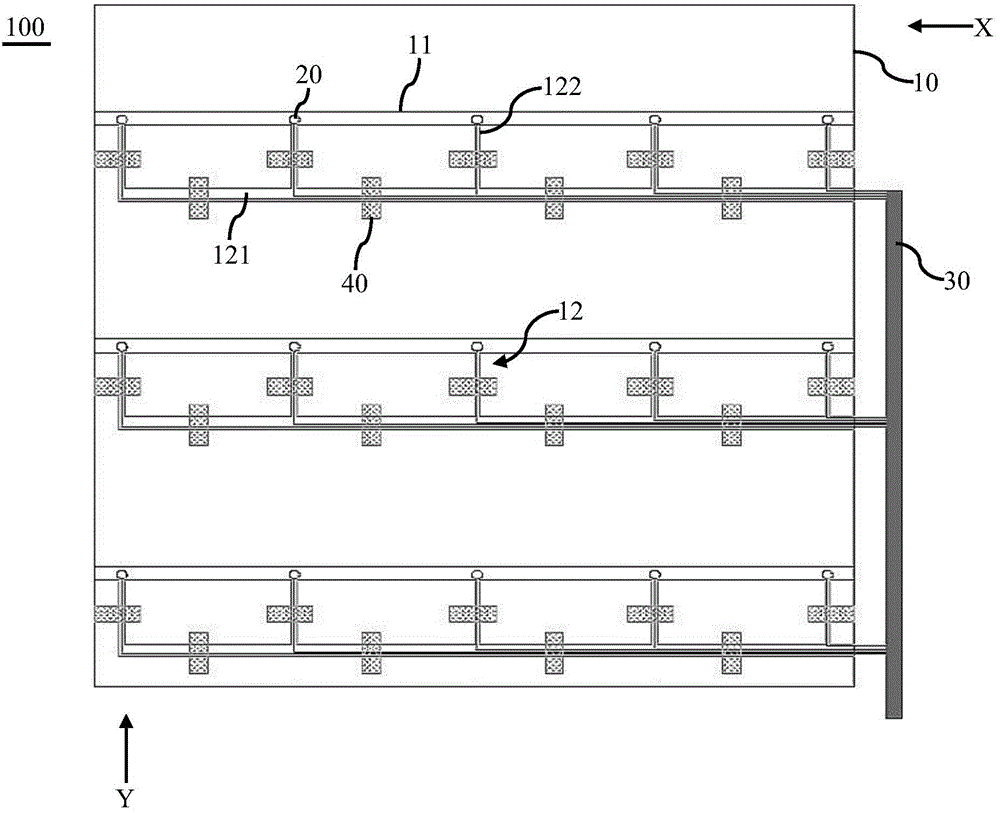

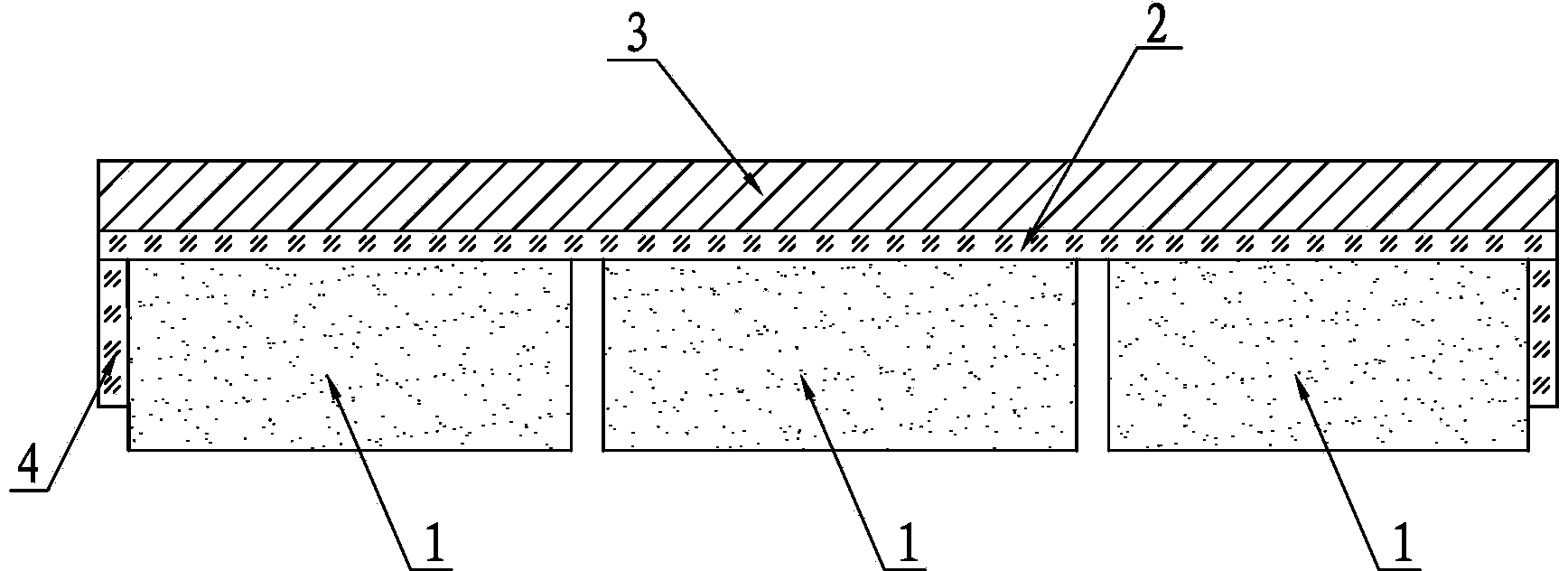

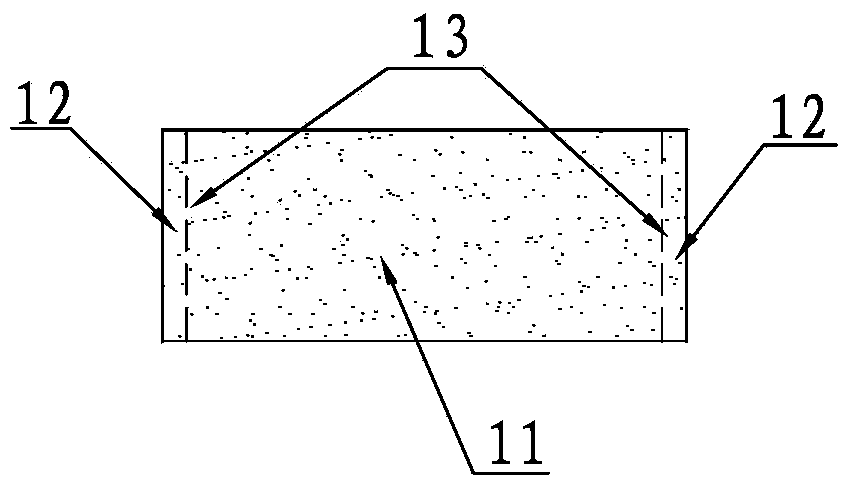

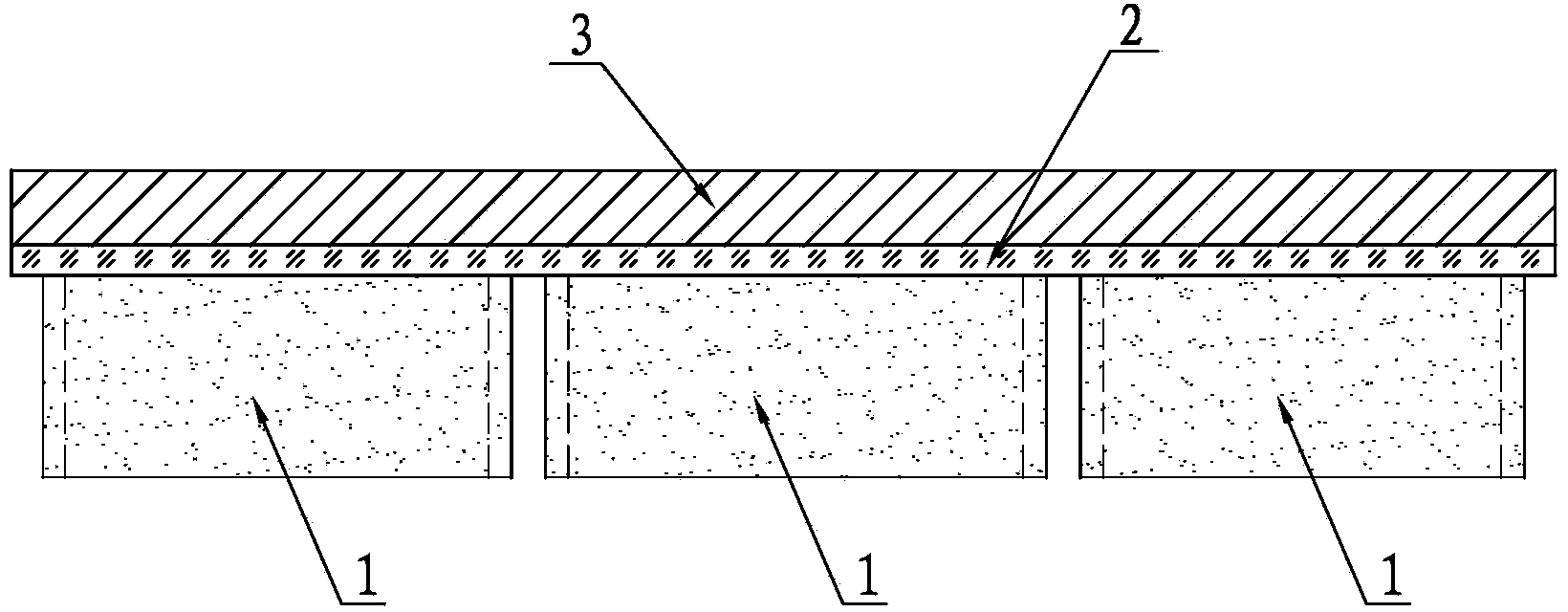

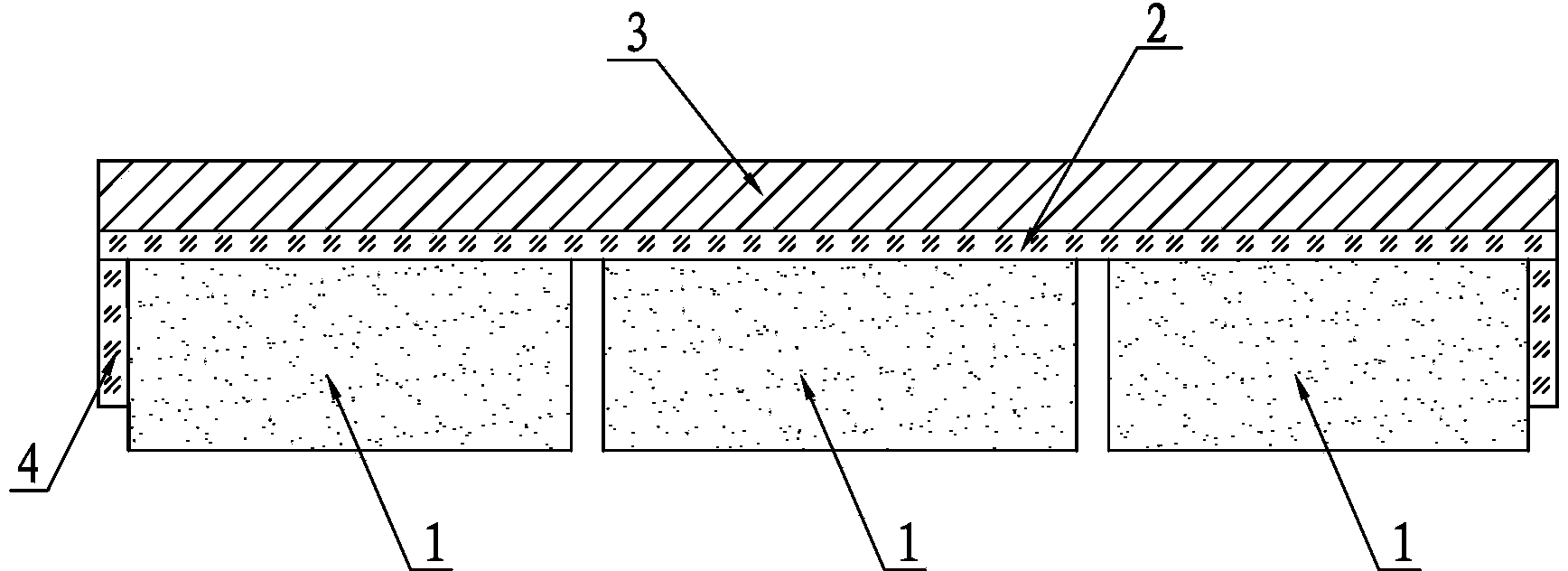

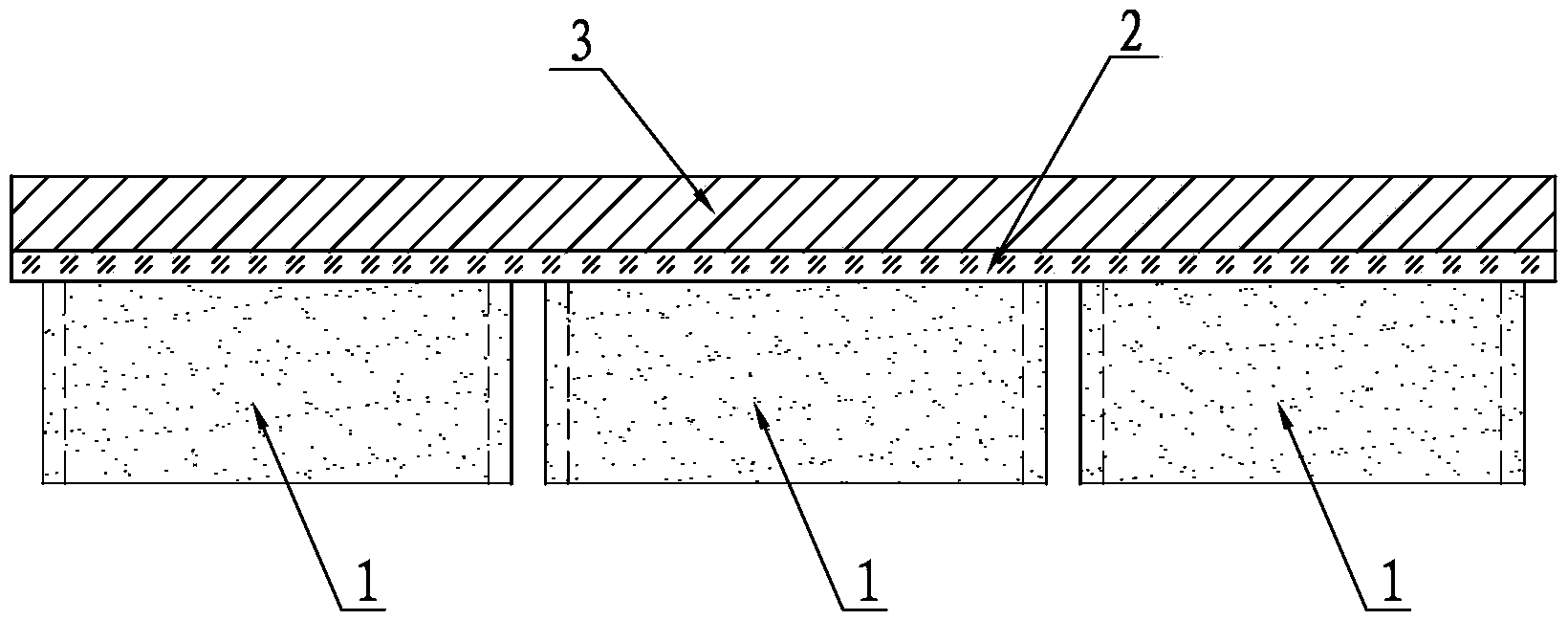

Photovoltaic module and preparation method

PendingCN107887462AAvoid splintersAvoid debrisFinal product manufacturePhotovoltaic energy generationIndirect contactTransmittance

The invention relates to a photovoltaic module comprising a light-transmitting layer, a battery assembly and an encapsulating layer that are successively stacked. The battery assembly comprises at least one battery piece laid between the light-transmitting layer and the encapsulating layer and having a side facing the light-transmitting layer, wherein the side and the light-transmitting layer arearranged at a predetermined interval. The predetermined interval causes the side, facing the light-transmitting layer, of the battery piece not to be in direct or indirect contact with the light-transmitting layer such that a problem is avoided that the battery piece is pressed to fracture or smash during a stacking process. In addition, removal of an encapsulating material between the battery piece and the light-transmitting layer is beneficial to reducing the production cost and the light-absorbing rate of the encapsulating material, and avoids a transmittance decrease and am efficiency decrease of the photovoltaic module due to the deterioration of the encapsulating material. The photovoltaic module is easy to produce, high in preparation efficiency and finished product rate, and low inproduction cost.

Owner:GREE ELECTRIC APPLIANCES INC

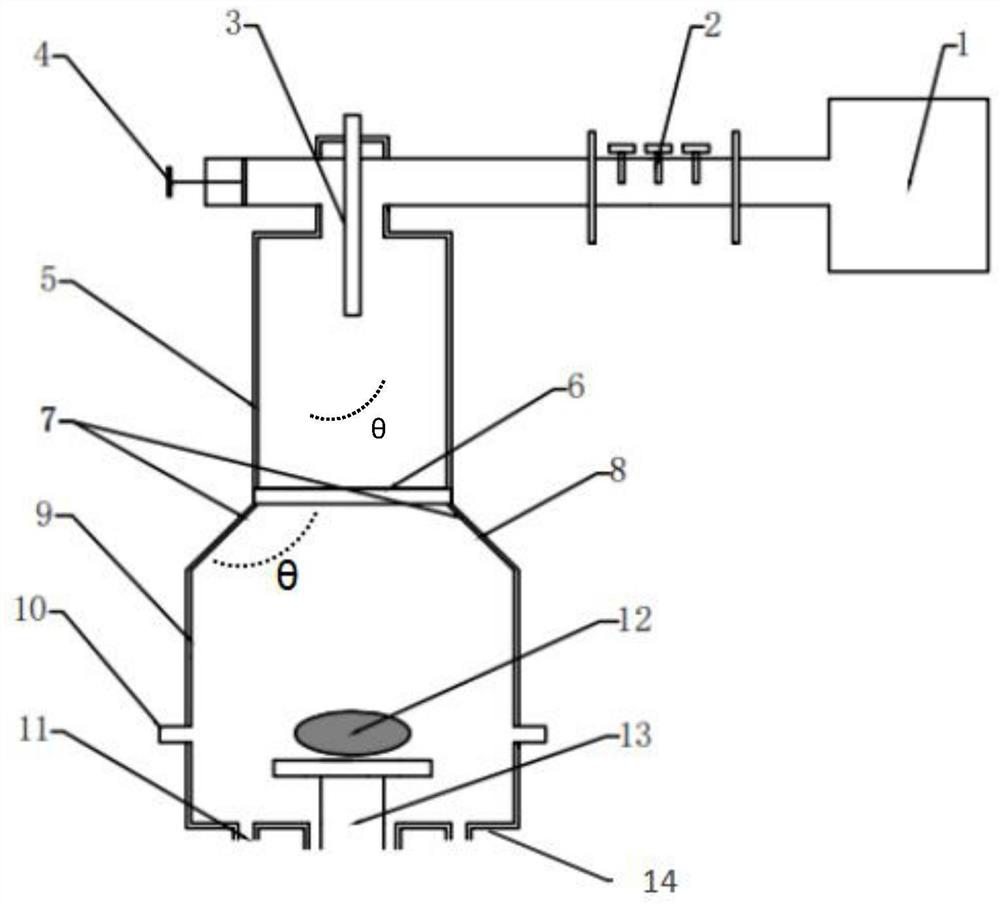

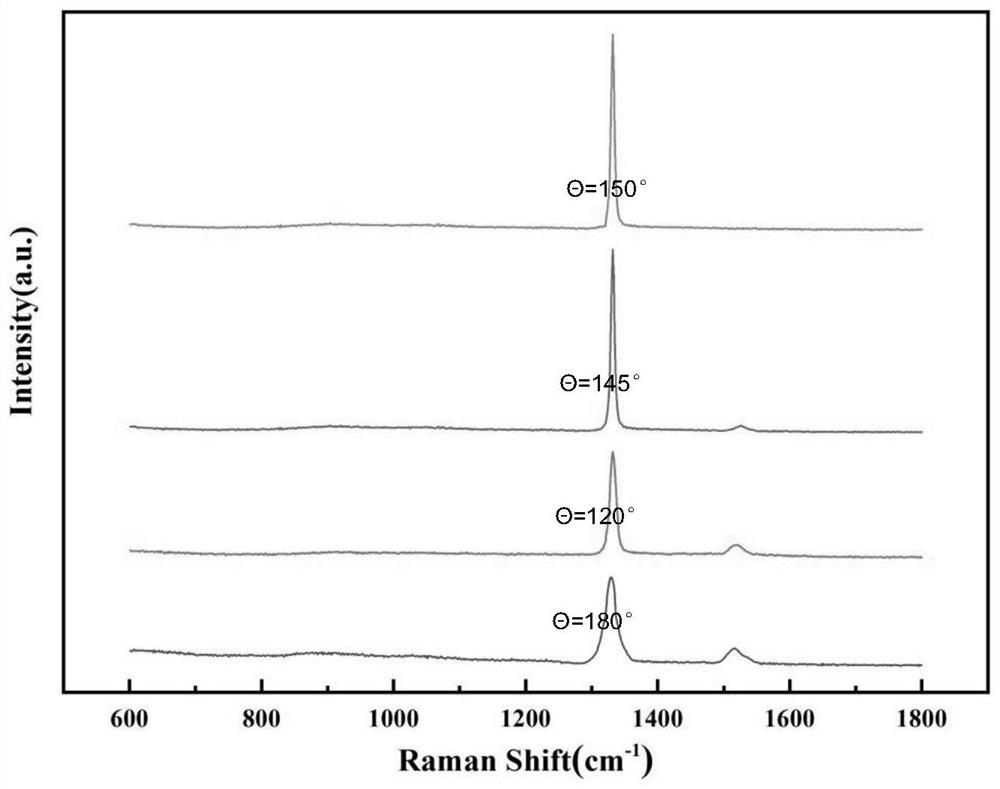

Method for synthesizing diamond based on microwave plasma reactor

ActiveCN113388885AGuaranteed stabilityAvoid moving upPolycrystalline material growthFrom chemically reactive gasesPhysical chemistryDiamond deposition

The invention relates to the technical field of chemical vapor deposition, in particular to a method for synthesizing diamond based on a microwave plasma reactor. The method comprises the following steps: 1, screening seed crystals; 2, carrying out seed crystal pretreatment; 3, processing a cavity of a reaction cavity; 4, preventing seed crystals; 5, adjusting the reaction air pressure, adjusting the microwave input power, and exciting plasma; 6, adjusting the height of a first lifter and the height of a second lifter; 7, adjusting power and reaction air pressure; 8, carrying out diamond deposition; and 9, carrying out shutdown processing. According to the invention, through integral method control, the stability of the plasma ball is ensured, and the phenomenon that the plasma ball moves upwards is avoided; and reaction gas can be fully dissociated when the ratio of the reaction gas pressure to the power value ranges from 2 / 1 to 3 / 1, and the quality and the speed of grown diamonds are obviously improved.

Owner:秦皇岛本征晶体科技有限公司

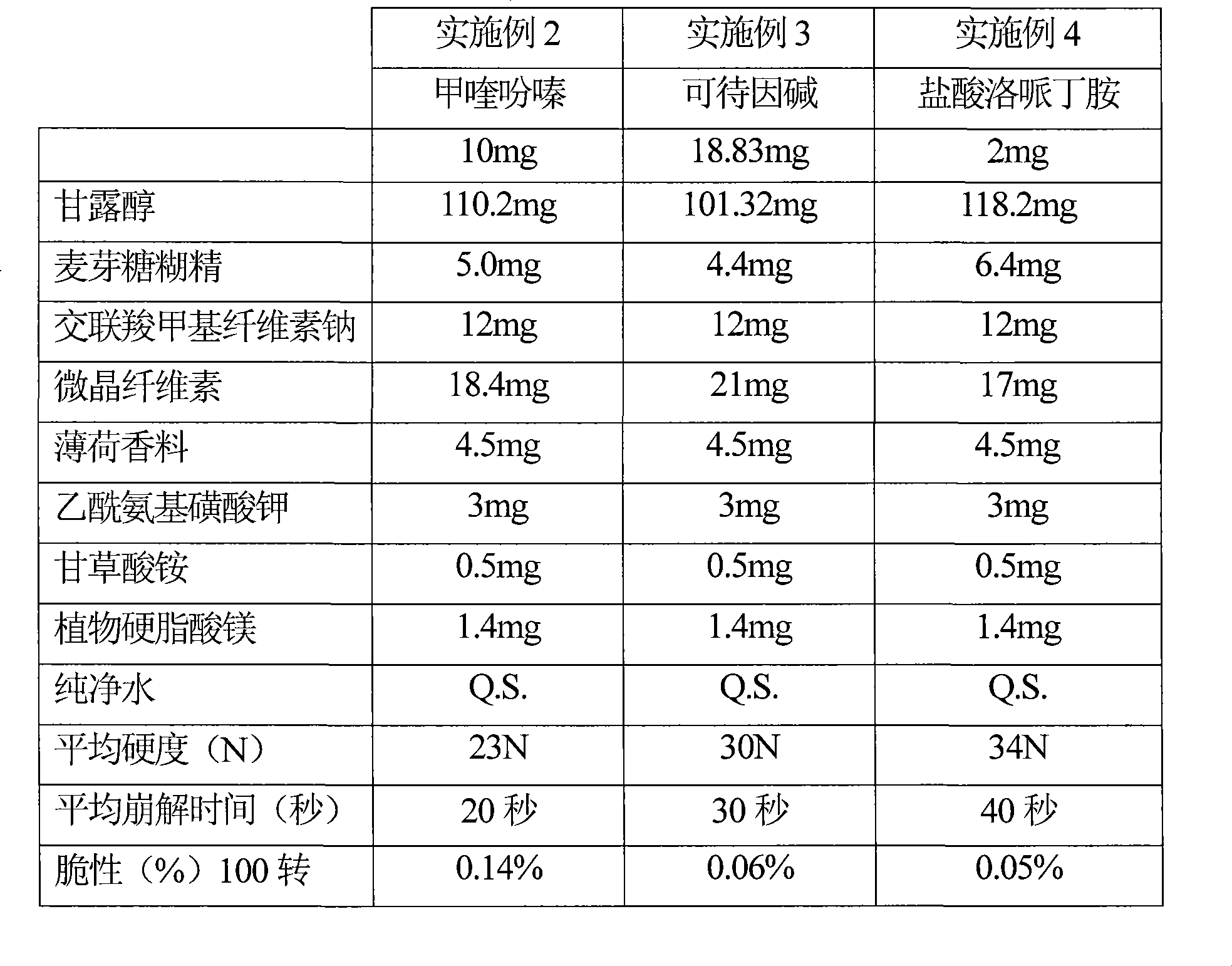

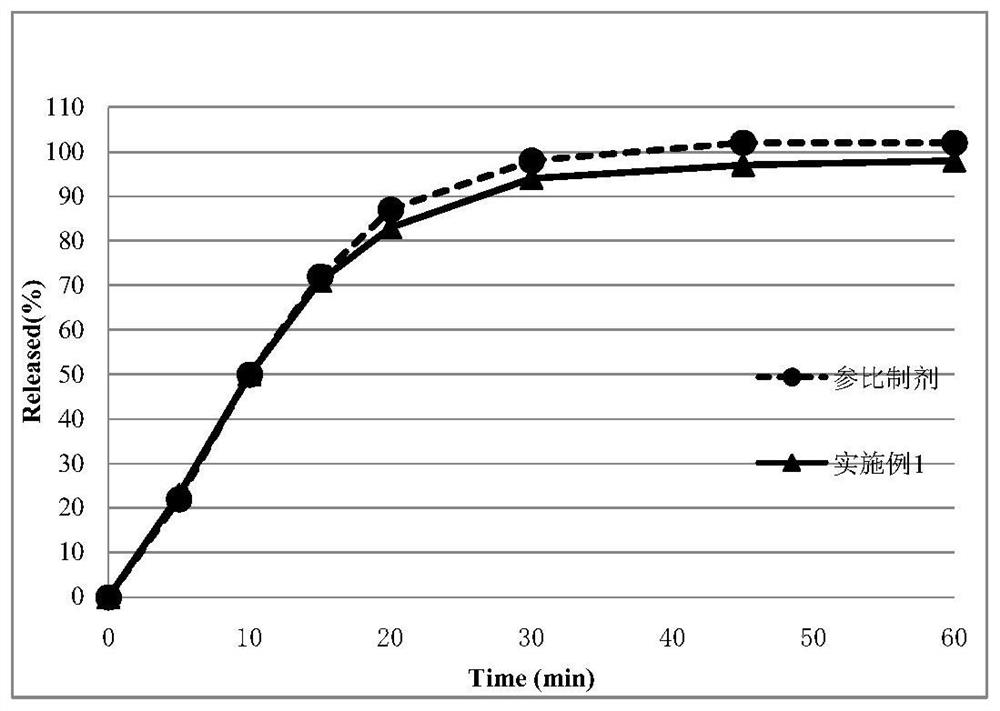

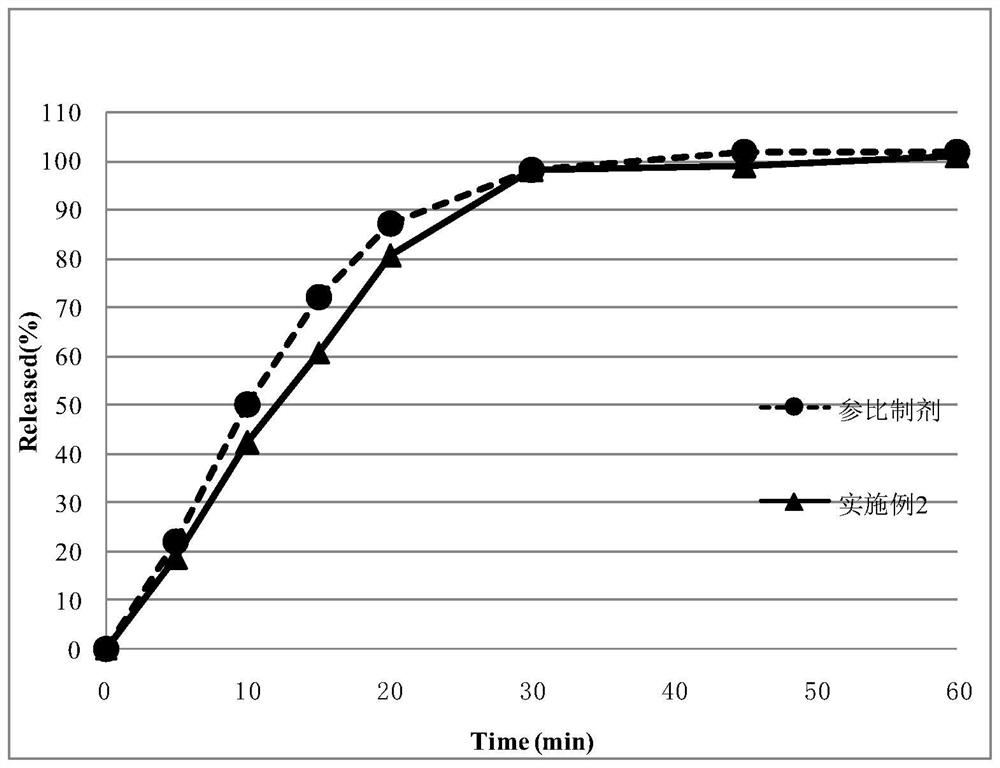

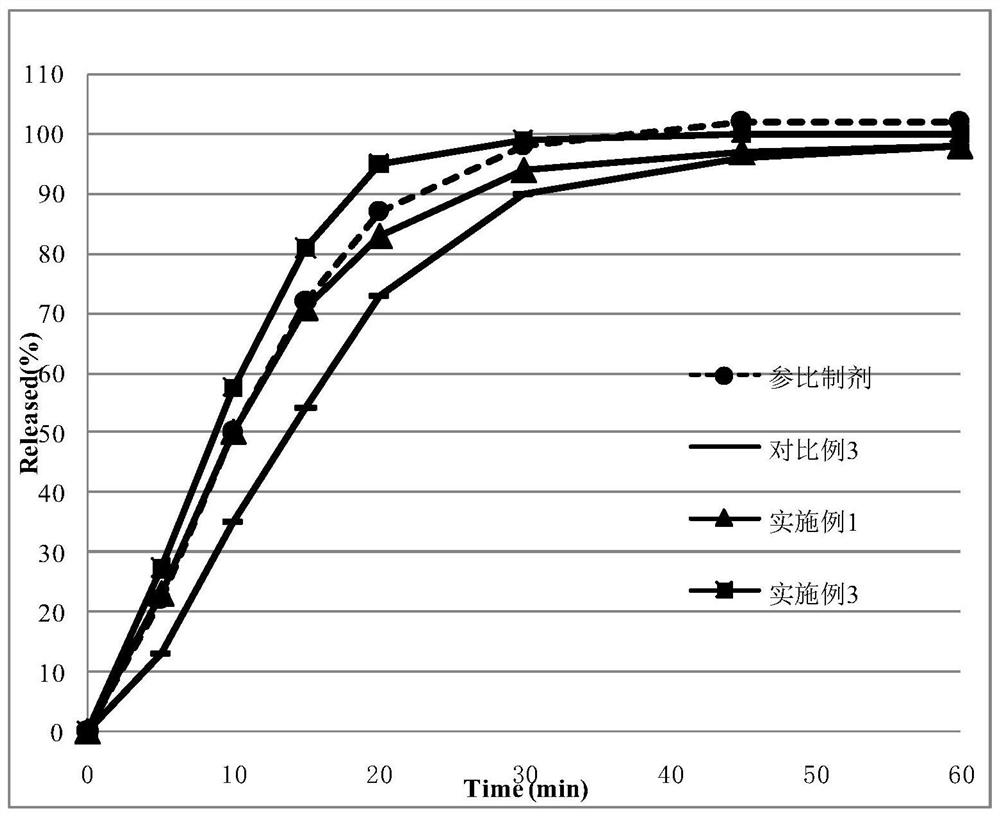

Orodispersible domperidone tablets

InactiveCN101394850BHigh hardnessImprove featuresOrganic active ingredientsDigestive systemMANNITOL/SORBITOLMedicine

The present invention relates to an orodispersible tablet comprised of, by weight: a maximum of 15% of a low-dose, therapeutically active substance; from 55% to 70% of mannitol of a particle size between 30 μm and 300 μm; at least 2% of maltodextrin; from 3.5% to 8% of croscarmellose sodium; from 10% to 20% of microcrystalline cellulose; from 0.5% to 1.5% of magnesium stearate; and from 1% to 5% of flavoring (s) and sweetener (s).

Owner:PIERRE FABRE MEDICAMENT SAS

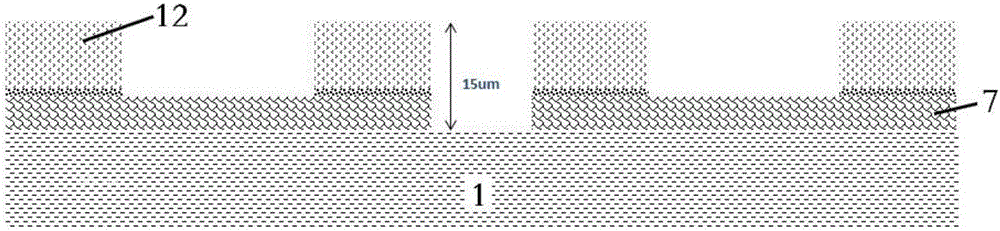

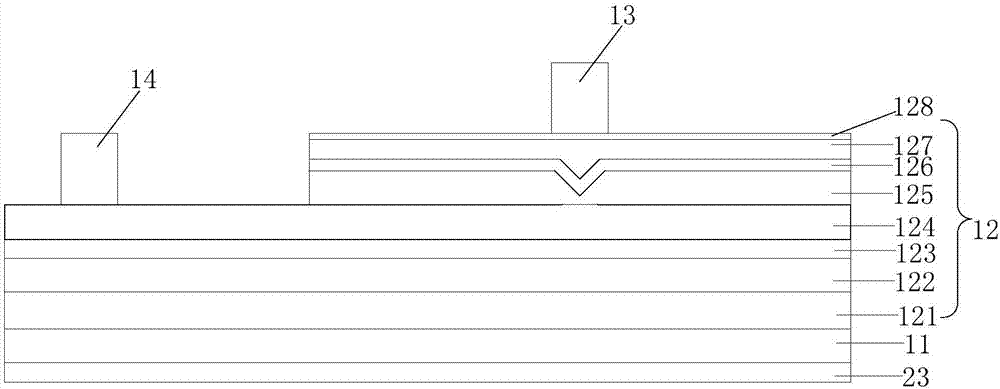

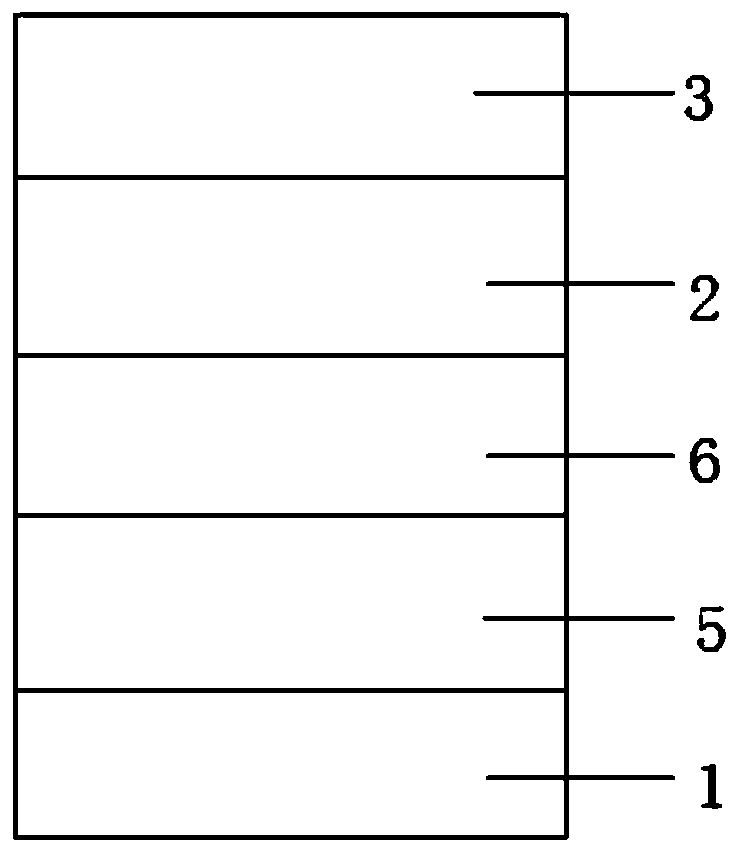

GaN-based yellow-light LED structure

InactiveCN108010999AAvoid splintersImprove uniformitySemiconductor devicesElectron blocking layerLead structure

The invention discloses a GaN-based yellow-light LED structure. The GaN-based yellow-light LED structure comprises a chip component and a light emitting diode component, the chip component comprises asilicon carbide substrate, an epitaxial layer growing on the silicon carbide substrate, and a P electrode and an N electrode arranged on the epitaxial layer, the epitaxial layer comprise an InN buffer layer, an AlGaN buffer layer, a non-intentionally doped GaN contact layer, an N-type doped GaN contact layer, an InGaN preparation layer, a yellow-light multi-quantum well layer, an electron blocking layer, a P-type doped GaN contact layer, and a transparent conducting layer stacked in sequence, the N electrode is arranged on the N-type doped GaN contact layer, the P electrode is arranged on thetransparent conducting layer, the InGaN preparation layer and the yellow-light multi-quantum well layer both include an inverted cone structure, and the light emitting diode component comprises a support used for fixing the chip component, a welding wire and a support electrode. According to the GaN-based yellow-light LED structure, phenomena of cracking and fragmentation can be avoided, and theuniformity is improved.

Owner:SICHUAN JIUDINGZHIYUAN INTPROP OPERATIONS CO LTD

Preparation method of tablet with improved performance

ActiveCN113057944AImprove stabilityImprove securityOrganic active ingredientsPill deliveryTabletingActive ingredient

The invention belongs to the technical field of pharmaceutical preparations, and discloses a preparation method of a tablet with improved performance. The preparation method comprises the following steps: uniformly mixing a bulk drug, a melting material, a diluent 1 and a disintegrating agent 1, conducting melting and granulating, uniformly mixing a granulation product with a diluent 2, a disintegrating agent 2 and a lubricant, and conducting tabletting to obtain the tablet. The preparation method not only can ensure that the bulk drug is kept stable in the processes of preparation and storage, but also solves the problem of sticking in a tabletting process, improves production efficiency, and has the characteristics of simple process, short production period, low cost and the like.

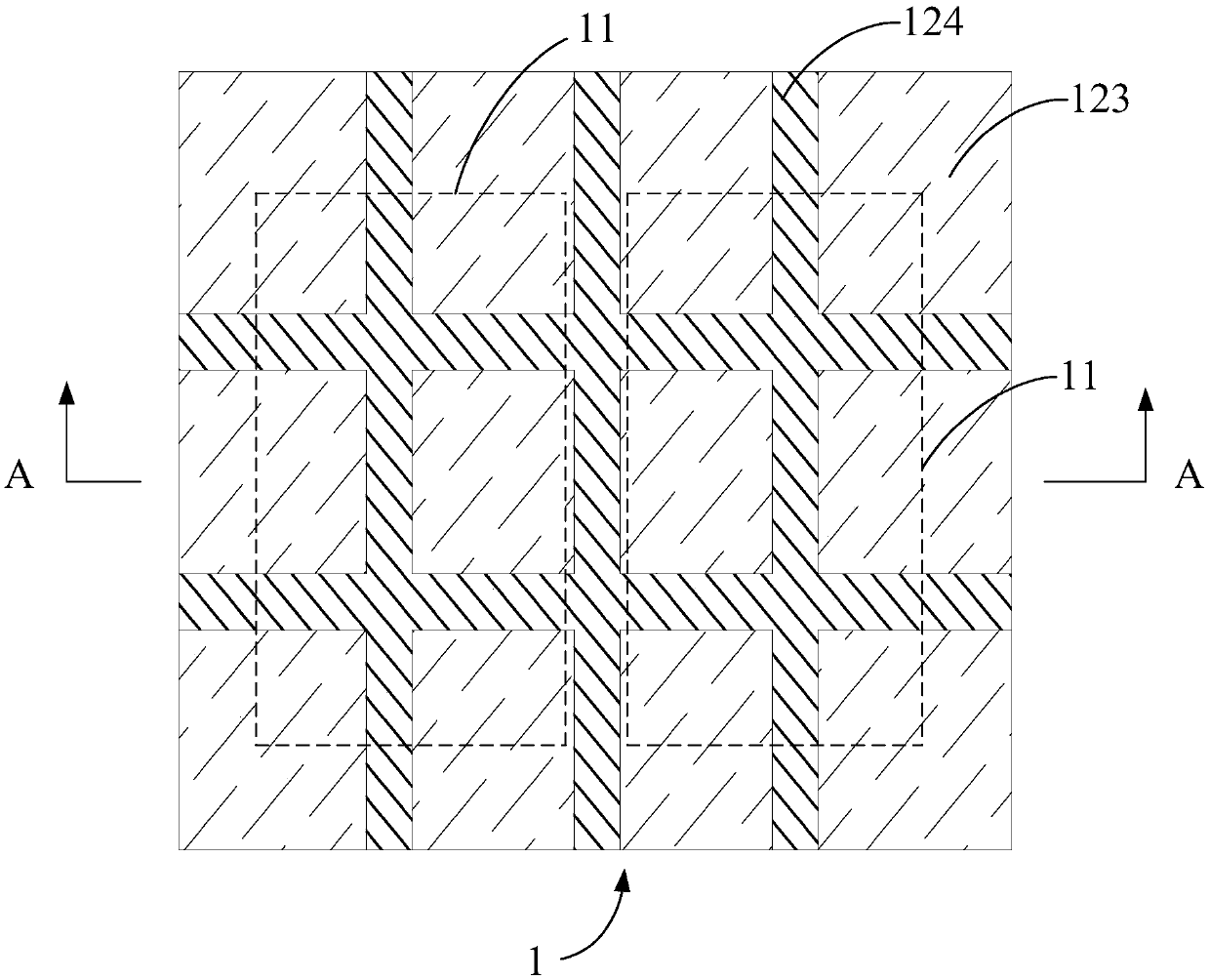

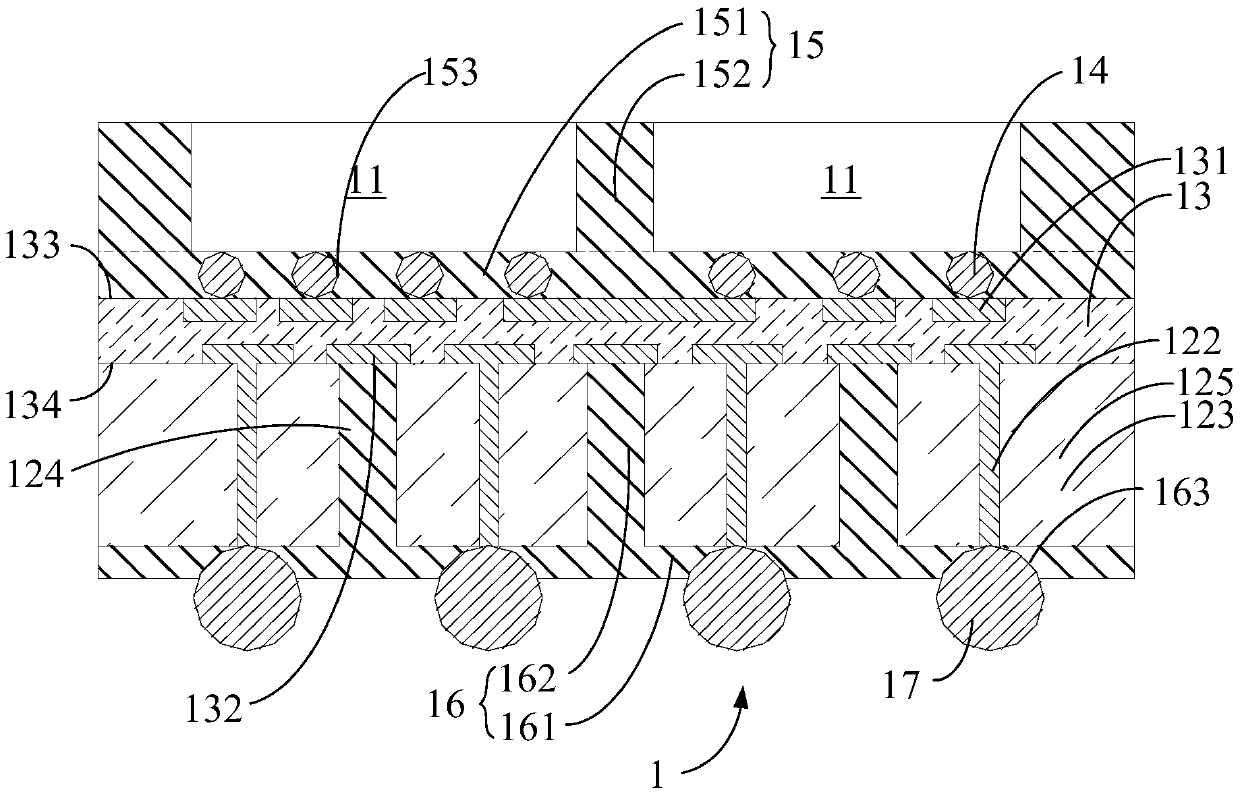

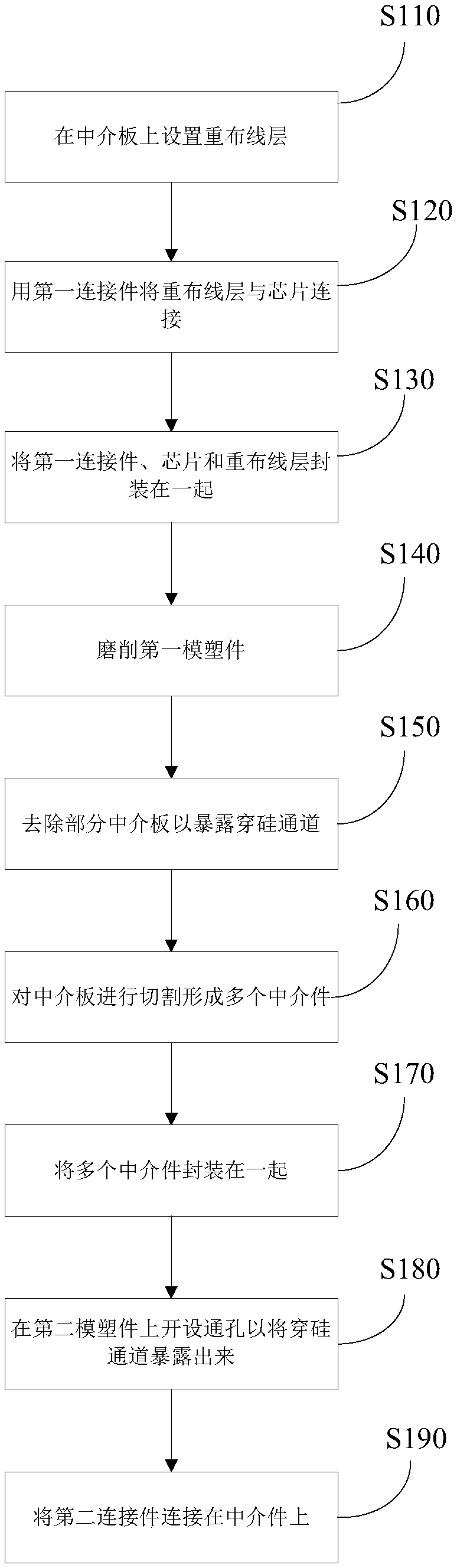

Semiconductor package and manufacturing method

PendingCN111244059AAvoid splintersSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectrical connection

The invention discloses a semiconductor package and a manufacturing method. The semiconductor package comprises a rewiring layer, a plurality of first connecting pieces, a plurality of chips, a plurality of intermediate pieces and a plurality of second connecting pieces, wherein the rewiring layer comprises a first surface and a second surface opposite to the first surface; the plurality of firstconnecting pieces are connected to the first surface of the rewiring layer; the plurality of chips are all arranged on one side, deviating from the rewiring layer, of the first connecting pieces and are all connected to the first connecting pieces; the plurality of intermediate pieces are connected to the second surface of the rewiring layer, a groove is formed between every two adjacent intermediate pieces, and one side surface, close to the rewiring layer, of each groove is in direct contact with the second surface of the rewiring layer; and the plurality of second connecting pieces are connected to one side, deviating from the rewiring layer, of the intermediate pieces, and the chip is electrically connected to the second connecting pieces through the first connecting pieces, the rewiring layer and the intermediate pieces. The arrangement of the groove can effectively prevent the semiconductor package from cracking due to warping of an intermediate substrate in the manufacturing process, and the yield of the semiconductor package is improved.

Owner:CHANGXIN MEMORY TECH INC

Panax japonicus tablets and preparation method thereof

ActiveCN107737146AWith promoting blood circulation and removing blood stasisWith hemostasis and pain reliefAntipyreticAnalgesicsAdditive ingredientMagnesium stearate

The invention relates to panax japonicus tablets and a preparation method thereof and belongs to the technical field of medicines. The method comprises the steps of soaking one part of panax japonicussubmicron powder in water, and then, separating filtrate from decoction dregs; dissolving hydroxypropyl methylcellulose in the filtrate, so as to obtain a binder; sprinkling the binder to a mixture of lactose, pregelatinized starch, the other part of panax japonicus submicron powder and the decoction dregs while stirring so as to prepare damp mass, then, carrying out screening, drying, and mixingwith magnesium stearate, and then, carrying out tabletting. The panax japonicus tablets rich in nutritional ingredients such as notoginsenoside R1, ginsenoside Re, ginsenoside Rb1, ginsenoside Rd, ginsenoside Rg1 and ginsenoside Rg3 have the characteristic of convenience in carrying and taking. The panax japonicus tablets have the actions of activating blood circulation to dissipate blood stasis,arresting bleeding and alleviating pain, strengthening body, enhancing immunity, resisting fatigue and the like.

Owner:YANGZHOU UNIV

A tempered fixture and its rack

The invention discloses a tempering fixture and its rack, comprising teeth and tooth slots located between two adjacent teeth, the tooth slots are used for inserting glass sheets to be tempered, and the width direction of the tooth valleys of the tooth slots An expansion margin is left; the expansion margin corresponds to the maximum difference between the expanded thickness of the glass sheet to be tempered and the expanded width of the tooth valley during the tempering process. During the tempering process, the glass sheet to be tempered is placed in the tooth slot of the rack corresponding to the tempering fixture. Since the width direction of the tooth valley of the tooth slot has an expansion allowance, and the expansion allowance corresponds to the tempering treatment The maximum difference between the expanded thickness of the glass sheet to be tempered and the expanded width of the tooth valley, so the edge of the glass plate to be tempered will not be squeezed with the edge of the tooth valley, and the above rack structure can be used to avoid Edge chipping and cracking problems are easy to occur when tempering with tempering fixtures.

Owner:LENS TECH CHANGSHA

Bamboo ginseng slices and preparation method thereof

Bamboo ginseng slices and a preparation method thereof belong to the technical field of medicine. After soaking part of the superfine powder of bamboo ginseng in water, the filtrate is separated from the dregs; after dissolving hydroxypropyl methylcellulose in the filtrate, an adhesive is obtained; under agitation, the adhesive is sprayed on lactose, pre- The soft material is obtained from the mixture of gelatinized starch, another part of bamboo ginseng superfine powder and medicinal residue, which is then sieved, dried, mixed with magnesium stearate, and then pressed into tablets. Get rich in notoginseng saponin R 1 , Ginsenoside Re, Ginsenoside Rb 1 , Ginsenoside Rd, Ginsenoside Rg 1 and ginsenoside Rg 3 The bamboo ginseng slices with nutritional ingredients are easy to carry and take. It has the effects of promoting blood circulation and removing blood stasis, stopping bleeding and relieving pain, strengthening the body, enhancing immunity and anti-fatigue.

Owner:YANGZHOU UNIV

Welding apparatus for solar module

InactiveCN102044590BAvoid flash pointReduce lobesFinal product manufacturePhotovoltaic energy generationWood splinterStress point

The invention relates to a welding apparatus for a solar module, comprising a hot aluminum plate, a label backing paper, a panel and a double faced adhesive tape, wherein the panel is arranged on one side of a cell film, the double faced adhesive tape is coated on an upper surface and a lower surface of the panel, the panel coated with the double faced adhesive tape and one end of the cell film close to the panel are clamped between the label backing paper and the hot aluminum plate. Compared with the prior art, a weld point can be located well and the weld balance can be reserved by utilizing the welding apparatus, a stress point tending to cause the splinter and concealed crack of the cell film can be effectively avoided; the welding apparatus has effect of buffering external force so as to avoid the external force from being directly acted on the cell film.

Owner:CEEG SHANGHAI SOLAR SCI & TECH

3C-SiC epitaxial structure

PendingCN111599854AQuality improvementReduced band gapSemiconductor devicesCrystallographyCondensed matter physics

The invention discloses a 3C-SiC epitaxial structure. The 3C-SiC epitaxial structure sequentially comprises a substrate, a GaN buffer layer and a 3C-SiC epitaxial layer from bottom to top. The GaN buffer layer with higher forbidden band width and critical breakdown field intensity is inserted between the substrate and the 3C-SiC epitaxial layer, so that the voltage withstanding performance of the3C-SiC device is improved. When the 3C-SiC grows on the Si substrate, the diffusion of Si atoms during the heating process will form interface holes, an AlN buffer layer grows on the Si substrate firstly, and atom migration recrystallization hardly occurs once the AlN buffer layer covers the substrate at a high temperature, so that the defect of the interface holes formed by volatilization of Si is effectively inhibited, and a high-quality 3C-SiC epitaxial structure is obtained.

Owner:安徽长飞先进半导体有限公司